许多FPGA规划中都会涉及到多个时钟,运用器材内部的PLL或许DLL会使得多个时钟的办理变得愈加简单。可是当多个时钟都是用PLL/DLL发生时,他们的体系复位信号怎样规划才愈加安稳呢?

在上一章《FPGA——复位规划》的内容里提出了异步复位、同步开释的办法,那么在体系复位后、PLL时钟输出前,即体系的作业时钟不确定的情况下,应该怎样考虑这个复位问题呢?

下面就解释一下所用的办法。

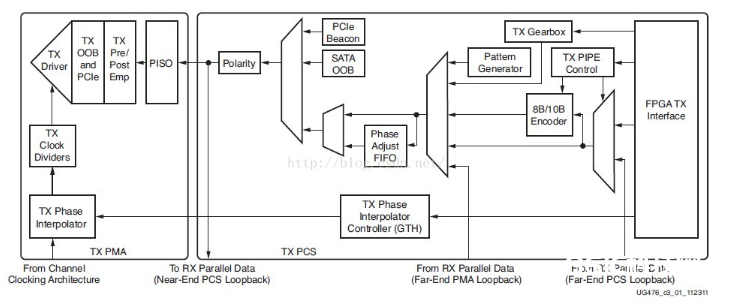

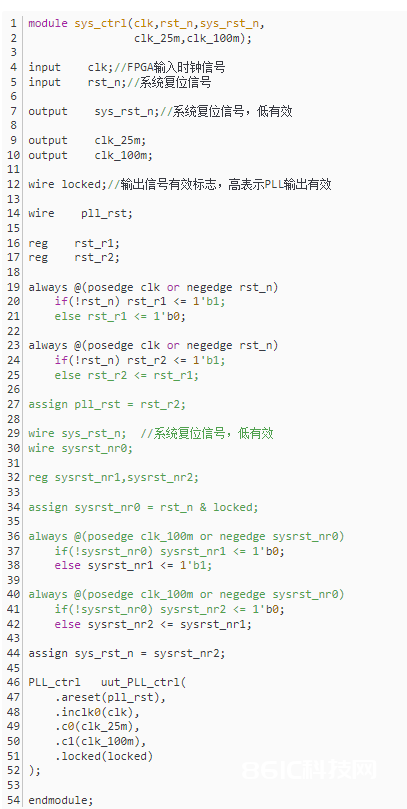

如下图,便是所用的RTL电路图。先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步开释处理,然后这个复位信号输入PLL,一起将clk也输入PLL。规划的初衷是在PLL输出有用时钟之前,体系的其他部分都坚持复位状况。PLL的输出locked信号在PLL有用输出前一向时低电平,PLL输出安稳有用之后才会拉高该信号,所以这儿就把前面说到的FPGA外部输入复位信号rst_n和这个locked信号相与作为整个体系的复位信号,当然了,这个复位信号也需要让适宜的PLL输出时钟异步复位、同步开释处理一下。也便是说,为了到达牢靠安稳的复位信号,该规划中对复位信号进行了两次处理,分别是在PLL输出前和PLL输出后。