衔接/参阅器材

ADA2200

同步解调器和可装备模仿滤波器

AD7192

内置PGA的4.8 kHz、超低噪声、24位Σ-Δ型ADC

ADG794

低压、300 MHz、四通道2:1多路复用模仿高清电视音频/视频开关

ADP151

超低噪声、200 mA CMOS线性调理器

电路功用与优势

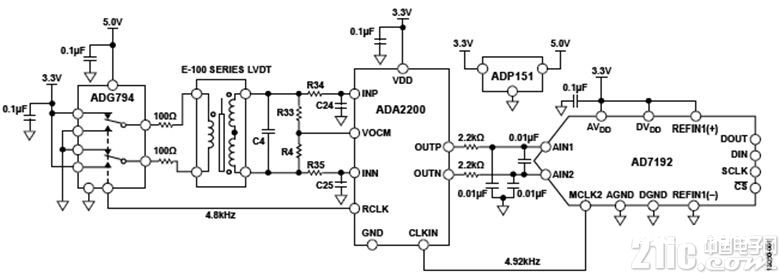

图1所示电路是一款完好的线性可变差分变压器(LVDT)信号调度电路,可准确丈量间隔机械参阅点的线性方位或线性位移。模仿域中的同步解调用于提取方位信息并按捺外部噪声。24位、Σ-Δ模数转化器(ADC)可数字化方位输出信息,以完结高精度。

LVDT在活动中心和线圈组件之间选用电磁耦合。这种非触摸式(因而是无冲突的)作业方法是它们广泛用于航空航天、进程操控、机器人、核、化学工厂、液压、动力涡轮以及其他恶劣作业环境和要求具有长作业寿数与高可靠性运用的首要原因。

包括LVDT鼓励信号在内的整个电路功耗仅为10 mW。电路鼓励频率和输出数据速率均为SPI可编程。 该体系答应在可编程带宽和动态规模之间进行权衡取舍,支撑1 kHz以上的带宽,且在20 Hz带宽时具有100 dB动态规模,是精细工业方位和计量运用的抱负之选。

图1. LVDT信号调度电路(原理示意图: 未显现一切衔接和去耦)

电路描绘

ADA2200同步解调器可在信号解调至与LVDT中心位移成份额的低频输出电压之前对LVDT次级信号进行滤波,然后提取方位信息。ADA2200驱动AD7192 24位Σ-Δ型ADC,后者对输出进行数字化和滤波处理。ADA2200发生同步LVDT鼓励信号,而ADG794开关将CMOS电平鼓励信号转化为精细3.3 V方波信号,驱动LVDT初级绕组。

LVDT是肯定位移传感器,可将线性位移转化为份额电信号。LVDT是特别的绕线变压器,具有活动中心,其方位与待测方位贴合。鼓励信号施加于初级绕组。跟着中心的移动,次级绕组上的电压成份额发生改动;依据该电压即可核算方位。

LVDT的类型有许多,此外提取方位信息的办法也各不相同。图1中的电路选用4线形式LVDT。将两个LVDT的次级输出相连使其电压相反,然后履行减法。当LVDT中心坐落零点方位时,这两个次级端上的电压持平,两个绕组上的电压差为零。跟着中心从零点方位开端移动,次级绕组上的电压差也随之添加。LVDT输出电压相位依据方向而改动。

该电路的主时钟由AD7192 ADC发生。ADA2200承受主时钟并发生其内部一切时钟,包括用作LVDT鼓励信号的参阅时钟。ADA2200上的时钟分频器装备为发生4.8 kHz鼓励信号。ADG794将鼓励信号转化为精细±3.3 V方波信号,该+3.3V来自于ADC电源电压。3.3 V电源也用作ADC基准电压;因而,鼓励信号与ADC基准电压之间的份额联系能够改进电路的噪声功用和稳定性。体系的3.3 V电源由ADP151低压差调理器供给;后者由5 V电源驱动。

LVDT次级绕组和ADA2200输入之间的耦合电路用来约束信号带宽,并调理RCLK和ADA2200输入之间的相对相位。该电路装备为具有最大正交(相位 = 90°)呼应以及最小同相(相位 = 0°)呼应。这使得能够仅经过丈量正交输出就能确认方位,进而使ADA2200输出电压对电路中相位的改动不甚灵敏。 LVDT的温度改动导致有用串联电阻和电感发生改动,是相位改动的首要来历。

ADA2200输出端的抗混叠滤波器坚持ADC所支撑的信号带宽。AD7192内部数字滤波器的输出带宽约等于0.27乘以输出数据速率。为了将输出带宽坚持在4.8 kHz最大输出数据速率,输出抗混叠滤波器的-3 dB转机频率能够设为2 kHz左右。关于要求较低输出数据速率的体系,可相应下降抗混叠滤波器的转机频率。

集成式同步解调器

ADA2200集成式同步解调器组成电路中心。它选用共同的电荷同享技能来履行模仿域内的离散式时刻信号处理。ADA2200具有全差分信号途径。它由高阻抗输入缓冲器后接一个固定低通滤波器(FIR抽取滤波器)、一个可编程IIR滤波器、一个解调器和一个差分输出缓冲器组成。它的输入和输出共模电压等于1.65 V(3.3 V电源电压的1/2)。

ADA2200承受来自AD7192 ADC的4.92 MHz时钟信号,然后发生其内部一切时钟,以及用作LVDT鼓励信号的4.8 kHz参阅时钟。ADA2200集成可装备时钟分频器,可编程支撑许多不同的鼓励频率。

CMOS开关

挑选ADG794 CMOS开关是因为它具有低导通电阻、快速开关时刻、先开后合式开关动作以及低成本等特色。

ADG794将ADA2200的低压CMOS电平RCLK输出转化为低阻抗差分输出方波源,然后驱动LVDT。为使开关留有裕量以便驱动正3.3 V信号,ADG794 VDD输入选用5 V电源供电。

LVDT

图1中的电路只需略作改动即可支撑各种LVDT。Measurement Specialties, Inc. E-100 LVDT选用四线式形式,以便演示电路的首要特色。E-100冲程规模为±2.54 mm,冲程端输出灵敏度为240 mV/V,满量程规模最大线性度差错为±0.5%,作业频率规模为100 Hz至10 kHz。完好详情请拜见E-Series LVDT数据手册。

ADA2200输入耦合网络

可调谐ADA2200输入耦合网络以支撑不同的LVDT。LVDT次级绕组电感和分流电容(C4)组成振荡电路。 R4和R33电阻下降了振荡电路的Q值,使该电路不易受LVDT绕组电感和电阻的改动影响,但功耗有所上升。R34/C24和R35/C25组成的RC滤波器对可下降信号带宽,一起供给调理电路相对相位所需的额定自由度。ADA2200内部相位灵敏检测器(PSD)的最大输出发生在0°或180°相对相移处。

关于选用4.8 kHz方波鼓励信号的E-100 LVDT而言,选用下列元件值可获得最大输出条件下的最优相位:

● R4 = R33 = 2.2 kΩ

● R34 = R35 = 1 kΩ

● C24 = C25 = 3300 pF

● C4 = 0.01 μF

如需调谐该电路,则可经过放置LVDT中心以发生挨近满量程输出信号的方法丈量相位;然后,丈量同相(I)和正交(Q)输出信号。选用这些丈量成果便可核算相对相位:

调理网络元件,直到θREL肯定值低于约±3°;这样能够改进电路关于LVDT电气参数改动的灵敏度。

ADC挑选和同步

挑选AD7192 Σ-Δ型ADC,因为该器材支撑可装备输出数据速率,并具有各种不同的数字滤波器输出选项,然后答应在带宽和噪声之间进行权衡取舍。主时钟输出功用可轻松完结ADC采样时钟频率与ADA2200输出信号的确认。这关于优化数字滤波器功用而言是有必要的。由LVDT信号确认方位所需的数值是一次鼓励时钟周期的均匀值。因而,当AD7192输出数据速率设为4.8 kHz时,即设为一个鼓励时钟周期时,可获得所需的均匀值。假如鼓励时钟周期和ADC采样频率未确认,则康复的方位丈量信息中包括过错。除以输出数据速率便可有用求取多个鼓励时钟周期的均匀值。

ADA2200输出信号哪怕在LVDT中心方位固定的状况下亦含有电能,数值为鼓励信号频率的倍数。还可在频率域中剖析数字滤波器功用。AD7192具有sinc3或sinc4传递函数,该传递函数在输出数据速率的倍数处归零。这些频率重量是杂散差错的来历。经过将ADC的输出数据速率设为鼓励信号频率(或鼓励频率的约数)便可按捺输出杂散。假如鼓励时钟周期和ADC采样频率未确认,则杂散将不会落在传递函数的零点。

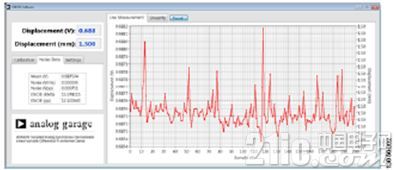

用于功用剖析的用户软件

该电路支撑图形用户界面,可方便地进行板上的器材装备,并评价电路功用。该软件的选项卡可履行电路校准和器材装备,以及显现噪声功用、线性度功用和实时方位丈量。

图2. 用户软件屏幕截图

噪声剖析

该电路的输出噪声是ADC输出数据速率的函数。表1显现数字化数据相关于ADC采样速率的有用位数(ENOB),假定满量程输出电压为2.5 V。该电路的噪声功用与LVDT中心方位无关。

表1. 噪声功用与带宽的联系

假如ADA2200输出噪声与频率无关,则估计有用位数将在输出数据速率每4次折叠下降时添加一位。 ENOB在较低输出数据速率下的添加放缓是因为输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的首要成分。

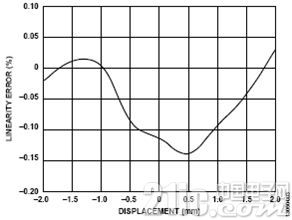

线性度测验成果

首先在±2.0 mm中心位移处履行一次两点校准即可丈量线性度成果。由这两次丈量成果可确认斜率和失调,然后完结预期直线拟合。 然后,在±2.5 mm满量程规模内丈量中心位移。从预期直线拟合数据中减去丈量数据即可确认线性度差错。

图3. 方位线性度差错与LVDT内核位移的联系

测得的数据显现电路功用优于E-Series LVDT数据手册中指定的线性度功用。

多LVDT同步作业

许多运用都会近间隔运用多个LVDT。若这些LVDT以类似的载波频率运转,杂散磁耦合或许导致拍频。 发生的拍频或许会影响这些条件下的丈量精度。为防止这种状况,一切LVDT有必要同步作业。

经过让器材一起退出复位状况,可同步多个ADA2200器材。ADA2200在RST引脚免除置位之后的第一个CLKIN上升沿时退出复位形式。因而,从单一源驱动一切ADA2200 CLKIN引脚以及一切RESETB线路便足以保证器材同步作业。防止在CLKIN上升沿邻近对RESETB免除置位,以防器材在不一起钟沿上复位。 可监控ADA2200器材的RCLK输出,保证ADA2200器材正确同步。

常见改动

在某些体系中,或许需求运用SAR ADC,而非Σ-Δ型转化器。 这些状况下,ADC转化时钟有必要与ADA2200更新速率同步。 如前所述,ADA2200输出会在鼓励频率的倍数处含有杂散。 这些杂散可经过移动均匀滤波器或级联多个移动均匀滤波器加以按捺。 移动均匀滤波器易于完结,且具有超卓的时域特性。 若要彻底按捺杂散,则移动均匀样本巨细有必要等于8个样本的整数倍。

图4显现了ADA2200衔接至AD7091R-2,后者是一个超低功耗、双通道、12位SAR ADC。 运用一个双通道ADC,因而ADA2200的OUTP和OUTN输出可次序采样。 因为ADA2200输出为分立式时刻样本,经过对两个次序输出样本履行减法操作(即VOUTP – VOUTN)便可完结差分丈量。

图4. 选用双通道SAR ADC进行差分采样

SYNCO信号在每个ADA2200输出采样周期内变为有用。SYNCO可用来中止微操控器,以便获取一对ADC样本(对OUTP和OUTN采样)。在上述示例中,采样周期等于鼓励时钟频率乘以8(或38.4 kHz);因而,ADC采样速率为76.8 kSPS。

电路评价与测验

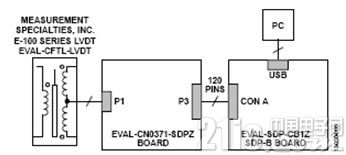

CN-0371电路运用EVAL-CN0371-SDPZ电路板和EVAL-SDP-CB1Z SDP-B操控器板。 这两片板具有120引脚的对接衔接器,能够快速完结设置并评价电路功用。 电路板包括待评价电路,SDP-B板合作CN-0371评价软件运用,捕捉电路板数据。

设备要求

需求以下设备:

● 带USB端口的Windows XP(32位)、Windows Vista 或Windows 7的PC

● EVAL-CN0371-SDPZ电路板

● EVAL-SDP-CB1Z SDP-B操控器板

● CN-0371评价软件

● Measurement Specialties, Inc. E-100经济型LVDT (EVAL-CFTL-LVDT)

开端运用

下载CN0371.zip文件,然后运转setup.exe文件。 默许状况下,程序安装在Analog Devices目录下。 程序名称为CN0371。

功用框图

电路框图拜见图5。 有关完好的电路原理图请拜见EVAL-CN0371-SDPZ-Schematic.pdf文件,该文件坐落CN-0371规划支撑包中。 用于电路板的5 V电源由USB总线经过SDP-B板的120引脚衔接器供给。

图5. 测验设置框图

设置

将EVAL-CN0371-SDPZ电路板上的120引脚衔接器衔接到EVAL-SDP-CB1Z SDP-B板上的CON A衔接器。 运用尼龙五金配件,经过120引脚衔接器两头的孔牢牢固定这两片板。

测验

发动评价软件,并经过USB电缆将PC衔接到SDP-B板上的微型USB衔接器。

一旦USB通讯树立,就能够运用SDP-B板来发送、接纳和收集来自电路板的数据。

图6显现电路板衔接SDP-B板的相片。 有关SDP-B板的信息请参阅UG-277用户攻略。

有关测验设置、校准以及怎么运用评价软件来捕捉数据的详细信息,请参阅CN-0371软件用户攻略。

针对原型开发的衔接

EVAL-CN0371-SDPZ电路板规划为调配EVAL-SDP-CB1Z SDP-B板运用,但任何微处理器都可与AD7192的SPI接口完结对接。关于另一个调配EVAL-CN0371-SDPZ电路板运用的操控器而言,第三方有必要开发相应软件。

现在已有一些转接板能完结与Altera或Xilinx现场可编程门阵列(FPGAs)的接口。 运用Nios驱动器,Altera的BeMicro SDK板能合作BeMicro SDK/SDP转接板一起运用。任何集成FMC衔接器的Xilinx评价板均可与FMC-SDP转接板一起运用。

EVAL-CN0371-SDPZ还兼容Digilent、Imod接口标准。

图6显现体系测验设置的相片。

图6. EVAL-CN0371-SDPZ电路板衔接EVAL-SDP-CB1Z SDP-B板和LVDT(中心衔接精细应变计接头)