第1章 长途更新LCD显现的布景与运用

1.1 LCD的发生与开展

液晶显现器,简称LCD(Liquid Crystal Display)。世界上第一台液晶显现设备呈现在20世纪70年代初,被称之为TN-LCD(歪曲向列)液晶显现器。80年代,STN-LCD(超歪曲向列)液晶显现器呈现,一起TFT-LCD(薄膜晶体管)液晶显现器技能被研制出来,但液晶技能仍未老练,难以遍及。80年代末90年代初,日本把握了STN-LCD及TFT-LCD出产技能,LCD工业开端高速开展。

现在,LCD是笔记本电脑和掌上电脑的首要显现设备,在投影机中,它也扮演着十分重要的人物,并且它开端逐步进入到桌面显现器商场中。信任不远的未来,LCD显现器将会更为遍及地运用于商业、工业、军事等范畴。

1.2 长途视频监控体系的简述

前期的视频监控体系受限于地域约束,跟着视频监控技能与网络技能的开展,呈现了长途视频监控体系。长途视频监控体系是把图形信息转变成信号信息,经过吸取、传输、显现等设备完结必定间隔内图形转换为图画,在互联网上传输,然后完结较远间隔能够看到现场图形信息的体系。

长途视频监控体系经过互联网打破了地域约束,跟着长途视频监控技能的老练以及运用,人们的出产、日子以及企业办理正在发生新的改变,长途视频监控体系广泛渗透到教育、政府、娱乐场所、医院、酒店、运动场馆、城市治安乃至家庭等多个范畴。

1.3 长途更新LCD显现在长途视频监控的运用

长途视频监控体系首要包括:前端摄像设备、传输存储设备、终端操控显现设备。其间,LCD显现作为监控显现设备运用于长途视频监控体系中。图 1为某视频监控体系规划原理图。

图 1 某视频监控体系规划原理图

第2章 体系全体规划方案

2.1研讨需求与方针

2.1.1研讨需求

本规划“依据FPGA的LCD显现的长途更新”作为长途视频监督体系的监控终端设备,伴跟着视频监控体系的开展而开展。近年来,我国视频监控商场受安全城市建设,北京奥运会、上海世博会、广州亚运会、深圳大运会等安保项目以及各职业视频监控需求快速增加等要素的影响和拉动,取得了超常规快速开展,全体商场规模敏捷扩展。

作为我国视频监控商场未来开展方向之一的网络化视频监控体系,其商场规模将于2013年达168.91亿元,增速远超职业均匀增加率水平。鉴于技能条件约束,高清视频监控一般树立在网络化的运用根底之上,若考虑给予智能高清视频监控商场占IP视频监控商场15%的比例预算,则2011-2013年智能高清监控商场规模将别离达13亿元、18亿元和25亿元,复合增速将高于36%。综上所述,能够估计未来3-5年视频监控商场将继续坚持微弱增加,职业全体处于高速开展阶段。可见,本规划有着广泛的运用远景以及商场需求。

2.1.2研讨方针

本次规划定位为视频监控体系的终端设备,其在体系中的方位如图 2所示。

图 2 视屏监控体系结构图

本规划预期完结的功用与技能指标:

-

供给杰出的人机界面和简略便利的操作方法;

-

供给两种视频监控方法:实时视频播映以及前史录像的播映;

-

预留USB接口,便运用户扩展前端存储功用;

-

供给用户办理功用,完结权限办理;

-

支撑图画屏蔽与图画抓拍;

-

完结图画分辨率:640*480;

-

完结视频帧率:30fps

其间,监控人员具体的操作方法为经过鼠标来挑选观看实时视频或查询视屏录像:

-

在观看实时视频时,本规划运转FTPClient运用程序向视屏录像服务器恳求实时的视屏数据,将接纳到的实时视屏先缓存在本地的内存中,然后进行解码、播映,经过HDMI接口将视屏数据传输到LCD显现器上面显现。

-

在查询前史录像时,本规划拟供给阅读视屏录像服务器中一切视屏录像的功用,用户依据自己的需求,选取相关的视屏文件,当用户挑选下载视屏文件到本地时,本规划从视屏录像服务器上面缓存视屏文件到内存中,然后写入挂载的U盘中。当视屏下载结束后,运转播映器程序播映下载的视屏文件,供给播映、行进、撤退、暂停等常用的播映功用。

2.2 体系概要规划

2.2.1 Genesys开发板简介

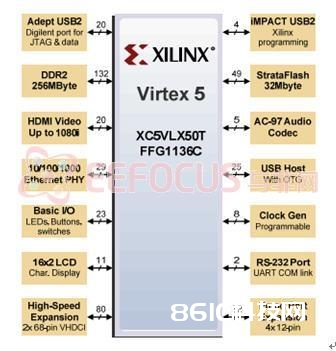

Digilent的Genesys开发板集成了功用强壮的Xilinx Virtex®-5 FPGA,为广阔用户带来了一个功用强壮、便利有用的规划渠道。其规划框图如图 3所示。

图 3 Genesys开发板的组成框图

Genesys板上还集成了千兆以太网接口、高速存储器、高分辨率音频和视频电路、以及USB主机接口等选项。Genesys开发板选用业界干流规划,无论是杂乱体系,仍是专用的高功用运用,Genesys都能为您供给有用的解决方案。其首要特性如下所示:

-

Xilinx Virtex 5 LX50T FPGA, 1136-pin BGA package

-

256Mbyte DDR2 SODIMM with 64-bit wide data

-

10/100/1000 Ethernet PHY and RS-232 serial port

-

multiple USB2 ports for programming, data, and hosting

-

HDMI video up to 1600×1200 and 24-bit color

-

AC-97 Codec with line-in, line-out, mic, and headphone

-

real-time power monitors on all power rails

-

16Mbyte StrataFlash™ for configuration and data storage

-

Programmable clocks up to 400MHz

-

112 I/O’s routed to expansion connectors

-

GPIO includes eight LEDs, two buttons, two-axis navigation switch, eight slide switches, and a 16×2 character LCD

-

ships with a 20W power supply and USB cable

2.2.2依据Genesys开发板的完结设想

依据上面所述的预期完结功用与技能指标,并结合Genesys开发板的资源,本规划的完结设想:

-

运用XILINX公司的Microblaze作为整个体系的中央处理器;

-

在Microblaze软核处理器体系中进行PeatLinux操作体系的移植;

-

运用FTP协议进行图画数据的传输;

-

经过有线以太网的通讯方法与FTP服务器进行衔接,并下载FTP服务器里的视频数据进行播映或存储在本地的U盘上;

-

运用带有HDMI的LCD液晶显现器作为显现设备;

2.2.3 Genesys开发板上的资源运用状况

依据规划的要求,Genesys开发板上的硬件资源既能满意本规划的硬件需求又能显现出其优胜的功用。表格 1为本规划在Genesys开发板上的资源运用状况。

表格 1 本规划在Genesys开发板上的资源运用状况

|

Genesys开发板的硬件资源 |

本规划中的运用状况 |

|

Adept USB2 |

√ |

|

DDR 256MByte |

√ |

|

HDMI Video |

√ |

|

10/100/1000 Ethernet PHY |

√ |

|

Basic I/O |

√ |

|

16 X 2 LCD |

|

|

High-Speed Expansion |

|

|

iMPACT USB2 |

√ |

|

StrataFlash 32Mbyte |

√ |

|

AC-97 Audio Codec |

|

|

USB Host |

√ |

|

Clock Gen |

√ |

|

RS-232 Port |

√ |

|

Pmod Port Expansion |

√ |

第3章 体系具体规划

3.1 体系硬件渠道规划

3.1.1 体系的硬件构成

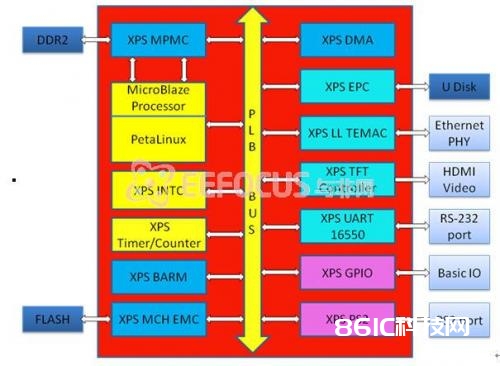

本体系的硬件规划由以下部分构成:MicroBalze处理器、中止操控器XPS INTC、XPS Timer/Counter定时器/计数器、XPS BRAM接口操控器、外部存储器操控器XPS MCH EMC、多端口存储器操控器 XPS MPMC,DMA操控器XPS DMA、外设操控器 XPS EPC、三态以太网MAC核 XPS LL TEMAC、XPS TFT操控器、串口操控器XPS UART 16650、通用IO操控器 XPS GPIO、XPS PS2等操控器组成。图4为本体系的结构框图。

其间,MicroBalze处理器、中止操控器XPS INTC、XPS Timer/Counter定时器/计数器构成了移植Petalinux根本硬件渠道。多端口存储器操控器 XPS MPMC衔接外部的DDR2 SODIMM,外部存储器操控器XPS MCH EMC衔接外接的Flash。XPS EPC供给USB Host功用用来衔接U盘。XPS LL TEMAC 核用来供给以太网接入。XPS TFT 操控器衔接HDMI接口,驱动LCD的显现。XPS UART 16650 衔接串口,作为移植PetaLinux的调试接口。XPS PS2 IPCore 衔接PS2接口,在本规划中衔接鼠标,供给用户操作接口。

图 4 体系结构框图

3.1.2 体系所需的IP核简介

为了进步规划功用和缩短规划周期,本规划将会充分运用Xilinx公司所供给的多个IP核进行开发规划。本规划中将会运用到的IP核以及运用该IP核的理由如下所述:

-

软处理器 本规划运用的处理器IP核为MicroBlaze。MicroBlaze内核是一款32位 RISC 哈佛架构软核处理器,具有丰厚的、针对嵌入式运用进行了优化的指令集。MicroBlaze 具有超越 70 种装备选项,支撑从超小型嵌入式微操控器到运转 Linux 的高功用嵌入式计算机的各种装备。这种灵活性的中心在于两种版别的 MicroBlaze:针对面积进行了优化的 MicroBlaze(带有3级指令履行流水线)和针对功用进行了优化的 MicroBlaze(带有5级指令履行流水线)。

-

中止操控器 规划中,选取了XPS Interrupt Controller IP Core该中止操控器。该操控器具有如下特征:作为32bit的从设备衔接到32、64或128位的PLB总线上;可装备的中止输入数目;触发沿可设置为上升沿或下降沿。

-

定时器 规划中需求运用定时器来为PetaLinux发生时钟节拍,规划中选了XPS Timer/Counter,是用于衔接PLB总线上的32位定时器。该IP一起具有如下特征:作为32bit的从设备衔接到32、64或128位的PLB总线上;其PLB接口支撑字节使能;可编程的定时器位宽;PWM输出。

-

DDR2操控器 选用XPS MPMC IP Core作为本体系的DDR2内存操控器。该操控器具有如下特征:支撑SDMA;支撑单速率内存(SDR)和双速率内存(DDR/DDR2/DDR3/LPDDR);支撑过错查验、功用显现和寄存器调试功用。

-

片上Block RAM操控器 选用BRAM Interface Controller作为片上Block RAM的操控器。该操控器具有如下特征:支撑32、64、128位的PLB接口;支撑32、64、128位的内部RAM数据宽度;32bit的地址宽度。

-

FLASH操控器 选用XPS MCH EMC作为外部FLASH存储操控器,该操控器具有如下特征:可作为32bit的从设备衔接到32、64或128位的PLB总线上;支撑多达4个的外部存储块;支撑单beat传输和burst传输;支撑同步/异步SRAMs和Nor Flash内存芯片。

-

DMA操控器 选用XPS Central DMA Controller作为体系的DMA操控器,该操控器具有如下特征:可作为32bit的从设备衔接到32、64或128位的PLB总线上;支撑一个通道的源地址到意图地址的内存直接读取;供给可编程的源地址、方针地址和传输长度;参数化的本地FIFO深度和burst突发深度;支撑不接连块的会输。

-

U盘操控器 选用XPS External Peripheral Controller作为U盘存储的操控器,该操控器具有如下特征:可作为32bit的从设备衔接到32、64或128位的PLB总线上;支撑同步或异步的方法与外设通讯;可依据外设芯片来设定数据宽度;可装备的外部总线接口时序。

-

以太网操控器 选取XPS LL TEMAC作为本规划的以太网MAC操控器,该操控器具有如下特征:具有2K、4K、8K、16K、32K 字节的接纳和发送数据FIFO缓存;过滤过错帧;支撑多种PHY接口;全双工操作;支撑VLAN帧。

-

TFT显现操控器 选取XPS TFT Controller作为LCD操控器,该操控器具有如下特征:支撑18bit VGA或24bit DVI;支撑25MHz 时钟完结640*480分辨率、60Hz刷新率;支撑PLB接口与TFT接口的两个独立时钟。

-

UART操控器 选取XPS 16650 UART作为本规划的串口操控器,该操控器具有以下特征:支撑PLB V4.6接口;软硬件上兼容悉数16450和16550UARTs;满意一切的串口接口协议。

-

经过I/O操控器 规划中选用PLB General Pupose Input/Output来操控LED灯,该操控器可装备为单端或双端GPIO通道;每个GPIO可动态装备为输入或输出口;可出产中止请示。

-

PS2操控器 本规划中运用XPS PS2 Controller作为鼠标的操控器,该操控器的特征有:作为32bit的从设备衔接到32、64或128位的PLB总线上;可装备成单端或双端的PS2操控器;支撑两个PS2设备,别离由两个8字节宽的寄存器操控。

3.1.3 移植PetaLinux的可行性剖析

Genesy Virtex-5 FPGA Development Board开发板上面有256MB的DDR2 SODIMM、16Mbyte StrataFlash(总共32M字节)。这16Mbyte StrataFlash作为非易失存储器来寄存FPGA的装备文件,单个FPGA的装备文件巨细不超越2MByte,剩下30M字节供用户运用。PetaLinux一般规矩下的最小装备为需求4MByte的DDR2,引荐运用16MByte的DDR2,至少8Mbyte的FLASH。因而,在Genesy Virtex-5 FPGA Development Board开发板上面嵌入MicroBlaze处理器核后,再进行PetaLinux的移植是可行的。本规划选用的嵌入式操作体系为2.6内核的PetaLinux。

3.2 嵌入式体系的选取

支撑MicroBlaze 处理器的嵌入式操作体系许多,比方μC/ OS-II、BuleCat ME Linux、RTA MB、 hreadX、PetaLinux等。PetaLinux 操作体系是面向MicroBlaze 软核处理器的全功用嵌入式 Linux 操作体系。其发布选用了“all in one” 的整合方法, 将针对 MicroBlaze 处理器定制的Linux2. 4/ 2. 6 内核源码、 U2boot 源码、相关的开发东西以及开发板参阅硬件渠道装备,集成在一个压缩包内发行,极大地便利了开发人员的运用。该操作体系首要具有以下几大特征:

-

针对 FPGA 嵌入式开发的特征选用了板级支撑包。

-

主动生成东西,能够依据用户界说的嵌入式硬件渠道信息主动生成板级支撑包,简化了操作体系的移植。

-

PetaLinux 发布的源码树中包括了部分常用 IP 核的驱动程序(如 GPIO、 EthernetLite、 UartLite 等) ,减少了用户移植、 编写驱动程序的作业量。

-

依据规划的不同需求,能够经过装备菜单将 PetaLinux 装备成without MMU support 和MMU support 两种版别,即μClinux 和规范Linux。

-

PetaLinux包括了很多的脚本指令(如petalinux2cop2y2autoconfig、petalinux2new2platform、petalinux2new2app等) ,给用户的运用供给了快捷条件。

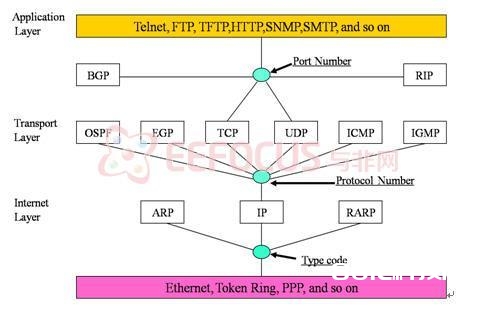

本标题要求完结以FTP协议长途更新LCD,FTP是文件传输协议的缩写,它是一种用于文件传输的Internet规范。一般,咱们能够以为FTP是一种依据TCP/IP协议的运用程序,它作业在OS网络模型的第七层,TCP协议的运用层上。

完善的内置网络是Linux的一大特征。 Linux在通讯和网络功用方面优于其他操作体系。其他操作体系不包括如此严密地和内核结合在一起的衔接网络的才能,也没有内置这些联网特性的灵活性。而Linux为用户供给了完善的、强壮的网络功用。

支撑Internet是其网络功用之一。Linux免费供给了很多支撑Internet的软件,Internet是在Unix范畴中树立并昌盛起来的,在这方面运用Linux是适当便利的,用户能用Linux与世界上的其他人经过Internet网络进行通讯。

文件传输是其网络功用之二。用户能经过一些Linux指令完结内部信息或文件的传输。

长途拜访是其网络功用之三。Linux不只答应进行文件和程序的传输,它还为体系办理员和技能人员供给了拜访其他体系的窗口。经过这种长途拜访的功用,一位技能人员能够有用地为多个体系服务,即便那些体系坐落相距很远的当地。

PetaLinux强壮的网络功用能够很好的完结本标题网络传输的要求,并且跟着PetaLinux的不断开展,越来越多的Xilinx公司的IP Core驱动程序(XPX LL TEMAC, XPS UART 16550,XPS GPIO,XPS DMA)加入了其内核中,大大减小了开发的难度,加上linux是开源的,在网上有很多的资源能够获取,从另一方面加快了规划开发的进程。依据以上长处,挑选了PetaLinux作为本次规划的嵌入式操作体系。

3.3 嵌入式体系运用程序规划

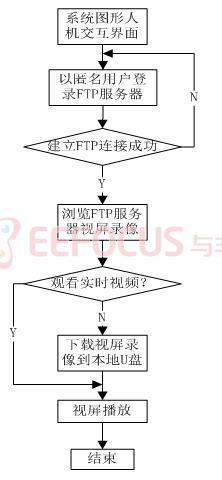

依据FPGA的LCD显现的长途更新的软件部分可分为FTP客户端模块、视屏播映器模块和图形人机交互模块三部分,其软件的组成结构如图 5所示,它们的效果别离是:

-

FTP客户端模块:完结FTP客户端的根本功用并供给文件下载的接口函数供上层调用。

-

视屏播映器模块:完结视屏文件的播映操控。

-

图形人机交互模块:供给整个体系的图形化用户办理接口。

图 5 软件组成

3.3.1 FTP客户端的规划

FTP在TCP/IP协议层间的方位如图 6所示:

图 6 FTP在TCP/IP协议层间的方位

FTP与其他依据TCP协议的运用程序不同,它在客户进程和服务器进程之间运用了两个TCP衔接:一个是操控衔接,客户端与FTP服务器经过操控衔接进行交流,衔接FTP,发送FTP指令都是经过操控衔接来完结的,它会一向继续到客户进程与服务器进程之间的会话完结停止;另一个是数据衔接,每逢有文件在客户机与服务器之间传输时,就树立一个数据衔接,数据恳求完结后,FTP封闭该段数据衔接。FTP选用这种方法将传输操控与数据传输的通道彼此别离,最大极限地进步了网络中数据的吞吐量。

视屏录像服务器中保存了视屏录像,假设在视屏录像服务器上也运转了FTP服务器程序,当用户点播实时视频时,本规划以匿名用户登陆FTP服务器将视屏文件的部分先缓存到本地的DDR2 SODIMM中,然后一起进行下载和播映。当用户挑选查询视屏录像时,首先将需求观看的视屏下载到本地的U盘中,然后运用播映器进行播映。考虑到文件下载是一种十分耗时的操作,为了进步视屏文件的下载功率,视屏文件的下载操作需求在子线程中完结。

3.3.2 视屏播映器模块的规划

视屏播映器模块预备在PeatLinux上面移植Mplayer播映器。MPlayer是Linux上的视屏播映器,它的功用十分强壮,能够播映很多格局的文件,在X86 PC机上运转很安稳,也能够把它移植到非X86CPU上的嵌入式体系中来。相对其它播映器来说,其资源占用十分少,不需求任何体系解码器就能够播映各种媒体格局,关于MPEG/XviD/DivX格局的文件支撑特别好。MPlayer能运用很多本地的Xanim,RealPlayer和Win32 DLL编解码器,播映大多数MPEG、VOB、AVI、OGG、VIVO、ASF/WMV、QT/MOV、FLI、RM、NuppelVideo、yuv4mpeg、FILM、RoQ文件。借助于MPlayer你能观看VideoCD、SVCD、DVD、3ivx、RealMedia和DivX格局的电影。MPlayer的另一个大的特征是支撑广泛的输出设备,它能够在X11、Xv、DGA、OpenGL、SVGAlib、fbdev、Aalib、DirectFB下作业,并且你也能运用GGI和SDL(由此运用它们支撑的各种驱动形式)和一些初级的硬件相关的驱动形式。这个播映器能很安稳地播映被损坏的MPEG文件,并且它能播映Windows media player都打不开的有损坏的AVI文件,乃至,没有索引部分的AVI文件也能够播映。

Mplayer播映器选用了MEncoder解码器。MEncoder选用的编解码器包是libavcodec,这个编解码器包能够在多种渠道上对Cinepak、DV、H.263、H.264/MPEG-4 AVC、HuffYUV、Indeo、MJPEG、MPEG-1、MPEG-2、MPEG-4 Part 2、RealVideo、Sorenson、Theora、WMV编码格局的视频流进行解码,它一起也是已知完结这些使命最快的解码器。

Mplayer移植到嵌入式渠道时,编译后的可履行程序的巨细在10~16MByte之间,因为Genesys开发板只要30MByte的Flash能够运用,所以不将Mplayer编译后的可履行文件放在文件体系中,而是将它存储在U盘中,待运转时再将它加载到开发板上履行。

3.3.3 图形人机交互模块

本规划以鼠标作为用户输入接口,选用带有HDMI接口的LCD显现器作为输出设备,运用QT 2.2.0进行图形界面的规划。QT/E是跨渠道的C++图形用户界面(GUI)东西包,它是闻名的QT开发商TrollTech发布的面向嵌入式体系的QT版别,Qt是现在KDE等项目运用的GUI支撑库,许多依据Qt的X Windows程序能够十分便利地移植到嵌入式Qt/Embedded版别上。自从Qt/Embedded发布以来,就有许多嵌入式Linux开发商运用Qt/Embedded进行嵌入式GUI运用开发。

Qt/Embedded是一个多渠道的C++图形用户界面开发东西包,它重视与能给用户供给精巧的图形界面所需的一切元素,并且其开发进程是依据面向对象的编程思维,并且Qt/embedded支撑真实的组成编程。

整个规划的软件工程流程图,如图 7所示:

图 7 体系的软件流程图

3.4 调试环境的建立阐明

依据前面的规划要求,本规划在调试时需求用到视频录像服务器。但因为实践条件的约束,故运用带有千兆以太网口的高功用PC作为视频服务器。