Cortex-M0 处理器简介

1. Cortex-M0 处理器依据冯诺依曼架构(单总线接口),运用32位精简指令集(RISC),该指令集被称为Thumb指令集。与之前比较,新的指令集增加了几条ARMv6架构的指令,并且加入了eThumb-2指令集的部分指令。Thumb-2技能扩展了Thumb的运用,答应一切的操作都能够在同一种CPU状况下履行。Thumb指令集既包括16位指令,也包括32位指令。C编译器生成的指令大部分是16位的,当16位的指令无法完成所需求的操作时,32位指令就会发挥作用。这样以来,在代码密度得到提高的一起,还避免了两套指令集之间进行切换带来的开支

2. Cortex-M0一共支撑56个根本指令,其间某些指令或许会有多种形式。相对于Cortex-M0较小的指令集,其处理器的才能可不一般,因为Thumb是通过高度优化的指令集。从理论来说,因为读写存储是的指令是彼此独立的,并且管用或逻辑操作的指令运用寄存器,Cortex-M0处理器能够被归到加载-存储(load-store)结构中。

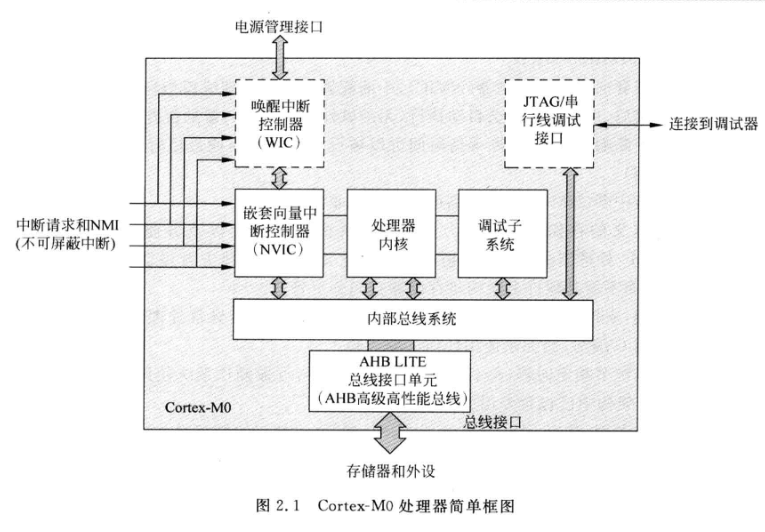

3. 处理器中心包括:

寄存器组 包括16个32位寄存器,其间有一些特别寄存器

算术逻辑单元

数据总线

操控逻辑

流水线依据规划可分为三种状况: 取指、译码、履行。

4. 嵌套向量中止操控器(NVIC)能够处理最多32个中止恳求和一个不行屏蔽中止(NMI)输入。

5. NVIC需求比较这个在履行中止和恳求中止的优先级,,然后主动履行高优先级的中止。

6. 假如要处理一个中止,NVIC会和处理器进行通讯,告诉处理器履行中止处理程序。

7. 唤醒中止操控器(WIC)为可选的单元,在低功耗运用中,在封闭了处理器大部分模块后,微操控器会进入待机装填,此刻,WIC能够在NVIC和处理器处于休眠的情况下,履行中止屏蔽功用。当WIC检测到一个中止时,会告诉电源办理部分给体系商铺,让NV%&&&&&%和处理器内核履行剩下的中止处理。

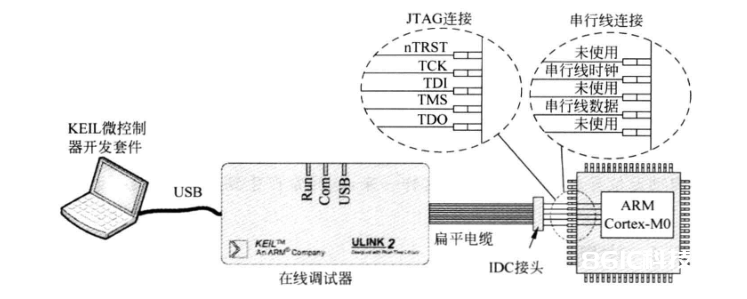

8. 关于调试子体系,当调试事情产生时,处理器内核会被置于暂停状况,这是开发人员能够查看当时处理器的状况。硬件调试东西有JTAG和SWD(串行线调试)。

ARM Cortex-M0 处理器的特性

体系特性

thumb指令集,具有高效和高代码密度

高功能,最高到达0.9DMIPS/MHz

内置的嵌套向量中止操控器(NVIC),中止装备和反常处理简单

确认的中止呼应事情,中止等候事情能够被设定为固定值或最短事情(最小16个时钟周期)

不行屏蔽中止(NMI),对高可靠性体系非常重要

内置的体系节拍定时器(systick)。24位定时器,可被操作体系运用,或许用作通用定时器,架构中现已包括专用的反常类型

恳求办理调用,具有SVC反常和PendSV反常(可挂起的办理服务),支撑嵌入式os的多种操作

架构界说的休眠形式和进入休眠的指令,休眠特功能大大下降能量的耗费。因为进入休眠状况需求运用特定的指令,而不是运用寄存器,架构界说的休眠形式也提高了软件的可移植性。

反常处理能够捕获到体系中的多种过错。

运用特性

中止数量可装备

支撑大端或小端存储器

可选择的唤醒中止操控器(WIC),处理器能够在休眠状况下掉电以下降功耗,而W%&&&&&%能够在中止产生时唤醒体系