1 概述

TI公司的TMS320C6655/57 DSP最高可以供给2.5GHz的累积DSP,使得该渠道具有高能效,并易于运用。此外,它与一切现有的C6000系列、定点和浮点DSP彻底向后兼容。其KeyStone架构供给了一个可编程的渠道,整合了各种子体系(C66x内核、存储器子体系、外设和加速器),并运用一些立异的组件和技能,大极限地提高了器材内和器材间的通讯,可以使多种DSP资源有用和无缝地操作。

这一架构有一些要害组件,如,多核导航器,可以对各种组件之间进行高效的数据管理。Teranet是一个无堵塞转化结构,可以使内部数据快速地移动。其多核同享存储器控制器可以直接拜访同享存储器和外部存储器,而不影响交流结构的功用。

关于定点运用,C66x核具有C64x+多核的4×倍数累加(MAC)的才能。此外,C66x核集成了浮点运算才能和每个核粗核算功用,它是较好的40GMACS/核和20GFLOPS/核(@1.25GHz作业频率)。它可以履行8个单精度浮点的MAC操作(每个周期),而且可以履行双倍和混合精度运算,契合IEEE754规范。该型C66x核集成了90个新指令(相关于C64x +核),以用于浮点和向量数学处理。这些增强功用大幅度地提高了信号处理中运用的DSP内核的功用。该型C66x核与TI公司曾经的C6000固定和浮点DSP内核向后代码兼容,确保了软件的可移植性,缩短了软件开发周期。

C6655/57 DSP器材集成了很多的片上存储器。除了32kB的L1程序和数据高速缓冲存储器以外,在每个核上还具有1024kB的专用存储器,可以装备为映射RAM或高速缓冲存储器。该器材还集成了1024kB的多核同享存储器,可以用来作为同享的L2 SRAM和/或同享的L3 SRAM.一切的L2存储器都具有过错检测和过错纠正功用。为了便利快速拜访外部存储器,该器材还包含了一个32位的DDR-3外部存储器接口(EMIF),为1333MHz运转,并具有ECC内存支撑。

该系列支撑多种高速规范接口,包含RapidIOver2,第二代PCI Express和千兆以太网。它还包含I2C、UART、多通道缓冲串行端口(McBSP)、通用并行端口、一个16位异步EMIF,以及通用的CMOS IO.该器材还选用了一个称为超链接的,40Gbaud全双工接口,以用于高吞吐量,低推迟通讯(设备之间或FPGA)。

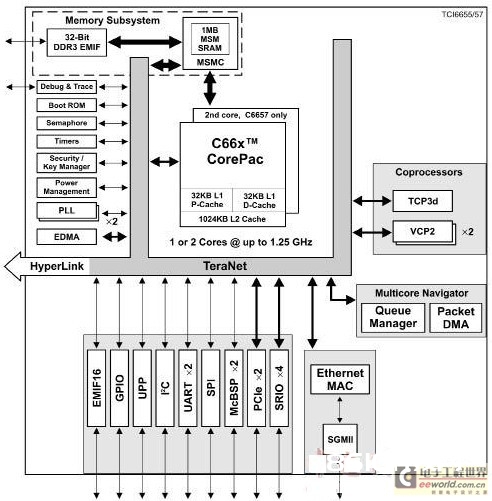

2 TMS320C6655/57体系框图

C6655/57器材具有一套完好的开发工具,其间包含:增强的C编译器、汇编优化器(来简化编程和调度)和WindowsR调试器接口,用于源代码履行的监督。

1

图1 TMS320C6655/57框图

3 TMS320C6655/57首要特性

•一个(C6655)或两个(C6657)TMS320C66x DSP内核子体系 (CorePacs),每个内核子体系

– 850MHz(C6657),1.0GHz或1.25GHz的C66x定点/浮点CPU核40GMAC/核,用于固定点(1.25GHz)20GFLOP/核,用于浮点(1.25GHz)

-内存32kB L1P每核32kB L1D每核 1024kB 本地L2每核

•多核同享存储器控制器(MSMC)

– 1024kB MSM SRAM存储器(由两 个DSP C66x CorePacs同享,用于C6657)

-存储器维护单元,用于MSM SRAM和DDR3_EMIF

•多核导航器

– 8192多用途硬件行列与行列管理器

-根据分组的DMA,用于零开支传输

•硬件加速器

-两个Viterbi协处理器

-一个Turbo协处理器解码器

•外设

-四通道SRIO2.1每通道1.24/2.5/3.125/5Gbaud操作支撑支撑直接I / O,信息传递支撑四个1×,2个2×,一个4×,和两个1×+一个2×链路装备

-第二代PCIe单端口支撑1或2车道最多支撑5Gbaud(每通道)

-超链接支撑衔接其他KeyStone架构的器材,供给可扩展性资源最高支撑40Gbaud

-千兆以太网(GbE)子体系一个SGMII端口支撑10/100/1000Mbps操作

– 32位DDR3接口DDR3-13338GB寻址内存空间

-16位EMIF

-通用并行端口8位双通道或16位每个支撑SDR和DDR传输

-两个UART接口

-两个多通道缓冲串行端口(McBSP)

– I2C接口

– 32个GPIO引脚

– SPI接口

-信号灯模块

– 8个64位定时器

-两个片上锁相环

– SoC安全支撑

•商用温度0℃~85℃

•扩展级温度40℃~100℃

•扩展低温55℃~100℃

4 评价板简介

C6657 Lite EVM精简版是一款高功用、低成本、独立的开发渠道,运用户可以评价和开发,选用德州仪器TMS320C6657数字信号处理器(DSP)的产品。该评价模块(EVM)也可作为TMS320C6657 DSP的硬件参阅规划渠道。该EVMs的形状巨细相当于一个PICMG AMC.0 R2.0的AdvancedMC模块。TMDSEVM6657LE带有一个集成,高速,具有体系盯梢才能的XDS560V2夹层模拟器。还带有原理图、代码示例和运用笔记,以便利开发,并缩短上市时刻。

2

图2 评价板TMDXEVM6657L框图

5 评价板首要特性

•德州仪器的定点DSP TMS320C6657

•512MB的DDR3内存(最高支撑1024Mbytes)

•128MB的NAND闪存

•16MB的NOR闪存

•一千兆位以太网端口,支撑

10/100/1000Mbps的数据速率–RJ-45衔接器和AMC查找之间交流

•170引脚B+风格的AMC接口

•超链接的高功用衔接器

根据TMS320C6657的1.25GHz DSP的参阅计划

TMS320C6657|DSP|数字信号处理器|可编程渠道

中电网

导读:TI公司的TMS320C6655/57是定点/浮点数字信号处理器(DSP),根据KeyStone多核架构,内核速度高达1.25GHz,集成了各种包含C66x内核、存储器子体系、外设和加速器在内的各种子体系,适用于高功用低功耗可编程运用,如使命要害型、测验与自动化、医疗印象以及基础设施设备等。

1 概述

TI公司的TMS320C6655/57 DSP最高可以供给2.5GHz的累积DSP,使得该渠道具有高能效,并易于运用。此外,它与一切现有的C6000系列、定点和浮点DSP彻底向后兼容。其KeyStone架构供给了一个可编程的渠道,整合了各种子体系(C66x内核、存储器子体系、外设和加速器),并运用一些立异的组件和技能,大极限地提高了器材内和器材间的通讯,可以使多种DSP资源有用和无缝地操作。

这一架构有一些要害组件,如,多核导航器,可以对各种组件之间进行高效的数据管理。Teranet是一个无堵塞转化结构,可以使内部数据快速地移动。其多核同享存储器控制器可以直接拜访同享存储器和外部存储器,而不影响交流结构的功用。

关于定点运用,C66x核具有C64x+多核的4×倍数累加(MAC)的才能。此外,C66x核集成了浮点运算才能和每个核粗核算功用,它是较好的40GMACS/核和20GFLOPS/核(@1.25GHz作业频率)。它可以履行8个单精度浮点的MAC操作(每个周期),而且可以履行双倍和混合精度运算,契合IEEE754规范。该型C66x核集成了90个新指令(相关于C64x +核),以用于浮点和向量数学处理。这些增强功用大幅度地提高了信号处理中运用的DSP内核的功用。该型C66x核与TI公司曾经的C6000固定和浮点DSP内核向后代码兼容,确保了软件的可移植性,缩短了软件开发周期。

C6655/57 DSP器材集成了很多的片上存储器。除了32kB的L1程序和数据高速缓冲存储器以外,在每个核上还具有1024kB的专用存储器,可以装备为映射RAM或高速缓冲存储器。该器材还集成了1024kB的多核同享存储器,可以用来作为同享的L2 SRAM和/或同享的L3 SRAM.一切的L2存储器都具有过错检测和过错纠正功用。为了便利快速拜访外部存储器,该器材还包含了一个32位的DDR-3外部存储器接口(EMIF),为1333MHz运转,并具有ECC内存支撑。

该系列支撑多种高速规范接口,包含RapidIOver2,第二代PCI Express和千兆以太网。它还包含I2C、UART、多通道缓冲串行端口(McBSP)、通用并行端口、一个16位异步EMIF,以及通用的CMOS IO.该器材还选用了一个称为超链接的,40Gbaud全双工接口,以用于高吞吐量,低推迟通讯(设备之间或FPGA)。

2 TMS320C6655/57体系框图

C6655/57器材具有一套完好的开发工具,其间包含:增强的C编译器、汇编优化器(来简化编程和调度)和WindowsR调试器接口,用于源代码履行的监督。

图1 TMS320C6655/57框图

3 TMS320C6655/57首要特性

•一个(C6655)或两个(C6657)TMS320C66x DSP内核子体系 (CorePacs),每个内核子体系

– 850MHz(C6657),1.0GHz或1.25GHz的C66x定点/浮点CPU核40GMAC/核,用于固定点(1.25GHz)20GFLOP/核,用于浮点(1.25GHz)

-内存32kB L1P每核32kB L1D每核 1024kB 本地L2每核

•多核同享存储器控制器(MSMC)

– 1024kB MSM SRAM存储器(由两 个DSP C66x CorePacs同享,用于C6657)

-存储器维护单元,用于MSM SRAM和DDR3_EMIF

•多核导航器

– 8192多用途硬件行列与行列管理器

-根据分组的DMA,用于零开支传输

•硬件加速器

-两个Viterbi协处理器

-一个Turbo协处理器解码器

•外设

-四通道SRIO2.1每通道1.24/2.5/3.125/5Gbaud操作支撑支撑直接I / O,信息传递支撑四个1×,2个2×,一个4×,和两个1×+一个2×链路装备

-第二代PCIe单端口支撑1或2车道最多支撑5Gbaud(每通道)

-超链接支撑衔接其他KeyStone架构的器材,供给可扩展性资源最高支撑40Gbaud

-千兆以太网(GbE)子体系一个SGMII端口支撑10/100/1000Mbps操作

– 32位DDR3接口DDR3-13338GB寻址内存空间

-16位EMIF

-通用并行端口8位双通道或16位每个支撑SDR和DDR传输

-两个UART接口

-两个多通道缓冲串行端口(McBSP)

– I2C接口

– 32个GPIO引脚

– SPI接口

-信号灯模块

– 8个64位定时器

-两个片上锁相环

– SoC安全支撑

•商用温度0℃~85℃

•扩展级温度40℃~100℃

•扩展低温55℃~100℃

4 评价板简介

C6657 Lite EVM精简版是一款高功用、低成本、独立的开发渠道,运用户可以评价和开发,选用德州仪器TMS320C6657数字信号处理器(DSP)的产品。该评价模块(EVM)也可作为TMS320C6657 DSP的硬件参阅规划渠道。该EVMs的形状巨细相当于一个P%&&&&&%MG AMC.0 R2.0的AdvancedMC模块。TMDSEVM6657LE带有一个集