一、导言

本方案是用VHDL言语来完成的依据RS232按位串行通讯总线的行列式矩阵键盘接口电路,具有复位和串行数据的接纳与发送功用,依据发光二极管led0-led2的显现状况可判别芯片的工作情况;完成一切电路功用的程序均是在美国ALTERA公司出产的具有现场可编程功用的芯片EPM7128SLC84-15上调试经过的。能经过动态扫描来判有键按下、将键值转化成对应的ASCII码值,在时钟脉冲的效果完成串行数据的接纳与发送。

二、规划方案

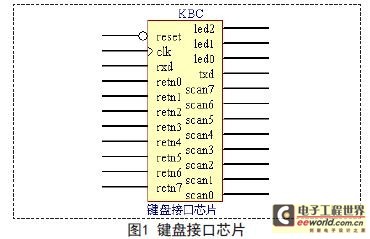

1.芯片引脚界说

reset复位输入端;clk时钟输入端;rxd串行数据接纳端;retn0-retn7键盘扫描行输入线;txd串行数据发送端;scan0-scan7键盘扫描列输出线;led0-led2显现输出端。

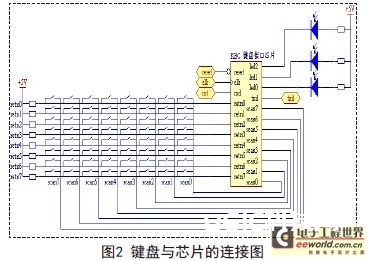

2.键盘与芯片的衔接图(如图2所示,为8×8的64键键盘)

3.动态扫描原理

(1)顺次使列线scan0-scan7输出0电平,查看行线retn0-retn7的电平状况。假如行线retn0-retn7的电平全为高电平,表明没键按下。假如retn0-retn7上的电平不全为高电平,表明有键按下。

(2)假如没键按下,就回来扫描。有键按下则进行逐行扫描,找出闭合键的键号。其进程是:先使scan0=0,scan1-scan7=1,检测retn0-retn7上的电平,假如retn=0,则表明榜首行榜首列的键被按下,假如retn1=0,则表明第二行第二列的键被按下,其它顺次类推;假如retn0-retn7均不为0,则表明这一列没键按下;然后再使scan1=0,检测第二列按键,这样一向循环下去,知道把闭合的键找到停止。

当有键按下时,依据该时间的scan值和retn值就可判别按下的是哪一个键。

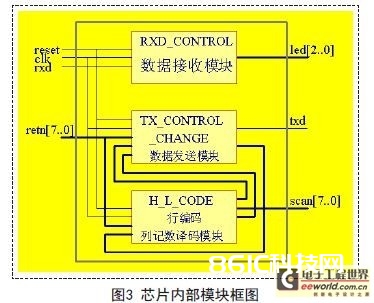

4.芯片内部模块框图

三、芯片规划

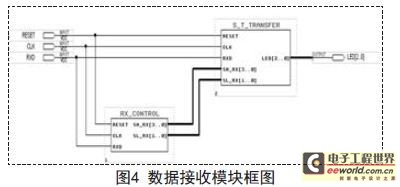

数据接纳模块框图如图4所示。

Reset复位输入端;clk时钟输入端;rxd串行数据接纳端;led[20]输出按下键对应的ASCII码值的低三位去驱动发光二极管。

该模块完成对串行数据的接纳记数和串并改换的操控功用。

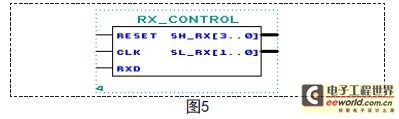

1.串行数据接纳操控单元

Reset 复位输入端;clk 时钟输入端;rxd 串行数据接纳端;sh_rx[30]接纳计数器高4位;sl_rx[10]接纳计数器低2位。

将串行数据接纳计数器设置位一个6位计数器,高4位为sh_r,低2位为sl_r,运用该计数器的状况完成串行数据的同步操控和记数操控。

2.串并转化电路单元

从RXD端接纳的串行数据进经过串并改换后,将其低三位经LED输出端输出,驱动发光二极管LED0,LED1,LED2发光,然后显现接纳端RXD的每个数据的低三位。当每个数据的低三位相一起,显现状况就不改变,不然就呈现闪耀现象,以此来查看芯片的工作情况。

四、总结

本方案是用VHDL言语来完成的依据RS232按位串行通讯总线的行列式矩阵键盘接口电路的规划,具有复位和串行数据的接纳与发送功用,依据发光二极管led0-led2的显现状况可判别芯片的工作情况;完成一切电路功用的程序均是在美国ALTERA公司出产的具有现场可编程功用的芯片EPM7128SLC84-15上调试经过的。该电路的规划贴近生活,实用性强,制成芯片后可作为一般的PC机键盘与主机的接口运用。