RealView DeveloperSuite(RVDS)东西室ARM公司推出的新一代ARM集成开发东西(上一代为ADS)。支撑一切ARM系列核,并与很多第三方实时操作体系及东西商协作简化开发流程。其包括以下组件:GUI(GraphicsUser Interface,图形用户界面)开发环境(CodeWarrior和AXD)、支撑软件组成。有了这些部件,用户就可认为ARM系列的处理器编写、调试自己的程序。

Code Warrior IDE供给了一个简略通用的图形化用户界面用于办理项目。能够以ARM处理器为方针,运用CodeWarrior IDE开发C、C++和ARM汇编代码。

AXD是ADS软件中独立于CodeWarrior IDE的图形软件,AXD用于对程序进行调试。(和Jlink一同运用)

作业状况

从编程的视点看,ARM微处理器的作业状况一般有两种,并可在两种状况之间切换:

- ARM状况,此刻处理器履行的是32位的字对齐的ARM指令。

- Thumb状况,此刻处理器履行的是16位半字对齐的Thumb指令。

在程序履行过程中,微处理器能够随时在两种作业状况之间切换,而且,处理器作业状况的改动并不影响处理器的作业形式和相应寄存器中的内容。

存储器格局

ARM体系结构将存储器看作是从零地址开端的字节的线性组合。从零字节到三字节放置第一个存储的字(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,顺次摆放。作为32位的微处理器,ARM体系结构所支撑的最大寻址空间是4G。

ARM体系结构能够用两种方法来存储字数据,称之为大端格局和小端格局。

- 大端格局:字数据的高字节存储在低地址上,而低字节存储在高地址上。

- 小端格局:字数据的高字节存储在高地址上,而低字节存储在低地址上。

ARM微处理器的指令长度能够是32位(在ARM状况下),也可认为16位(在Thumb状况下)。ARM微处理器中支撑字节(8位)、半字(16位)、字(32位)三种数据类型,

ARM支撑7中作业形式,分别为:

1、用户形式(Usr):用于正常履行程序

2、快速间断形式(FIQ):用于高速数据传输

3、外部间断形式(IRQ):用于一般的间断处理

4、办理形式(svc):操作体系运用的维护形式

5、数据拜访停止形式(abt):当数据或指令预取停止时进入该形式,可用于虚拟存储及存储维护。

6、体系形式(sys):运转具有特权的操作体系使命。

7、未定义指令间断形式(und):当未定义的指令履行时进入该形式,可用于支撑硬件

ARM微处理器的作业形式能够经过软件改动,也能够经过外部间断或反常处理改动。运用程序运转在用户形式下,当处理器运转在用户形式下时,某些被维护的体系资源是不能被拜访的。

除用户形式以外,其他六种形式称为非用户形式或特权形式;其间除用户形式和体系形式外的5种又称为反常形式,常用于处理间断或反常,以及需求拜访受维护的体系资源等状况。

ARM的寄存器

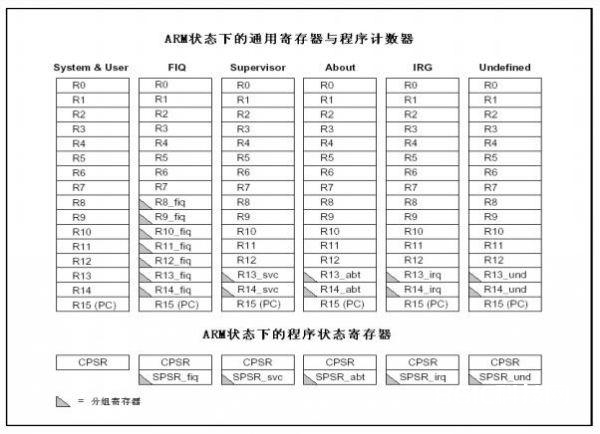

ARM微处理器共有37个32位寄存器,其间31个通用寄存器,6个为状况寄存器。可是这些寄存器不能被一起拜访,详细哪些寄存器能够拜访,取决于ARM作业状况及详细的运转形式。但在任何时候,通用寄存器R14-R0、程序计数器PC、一个状况寄存器都是能够拜访的。

寄存器(ARM状况):在ARM作业状况下,任一时间能够拜访16个通用寄存器和一到两个状况寄存器。在非用户形式下(特权形式)下,则可拜访到特定形式分组寄存器,详细见图:

寄存器(Thumb状况):是ARM状况下寄存器集的一个子集,程序能够直接拜访8个通用寄存器(R7-R0)、程序计数器(PC)、仓库指针(SP)、衔接寄存器(LR)和CPSR。详细见下页图:

Thumb状况下的寄存器安排与ARM状况下的寄存器安排的联系:

- Thumb状况下和ARM状况下的R0-R7是相同的。

- Thumb状况下和ARM状况下的CPSR和SPSR是相同的。

- Thumb状况下的SP对应于ARM状况下的R13。

- Thumb状况下的LR对应于ARM状况下的R14。

- Thumb状况下的程序计数器PC对应于ARM状况下R15。

不分组寄存器(The unbanked registers)

R0—R7

分组寄存器(The banked registers)

R8—R14

程序计数器:

R15(PC)

-

R0-R7是不分组寄存器。这意味着在一切处理器形式下,拜访的都是同一个物理寄存器。未分组寄存器没有被体系用于特别的用途,任何可采用通用寄存器的运用场合都能够运用未分组寄存器。

-

分组寄存器R8-R12

-

分组寄存器R13、R14.

R13一般用做仓库指针SP,R14用作子程序链接寄存器,指向函数的回来地址。 -

R15是程序计数器,也称为PC。其值等于当时正在履行的指令的地址+8(由于在取址和履行之间多了一个译码的阶段)。

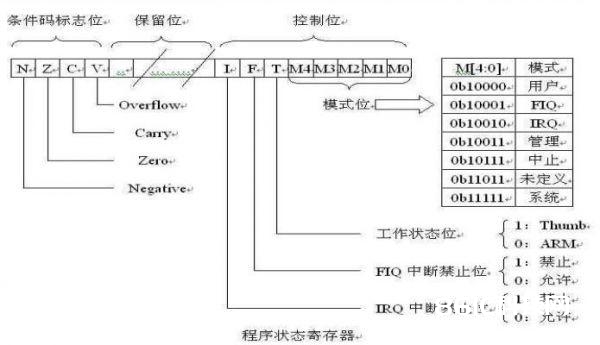

状况寄存器:

ARM一切作业形式下都能够拜访程序状况寄存器CPSR。CPSR包括条件码标志、间断制止位、当时处理器形式以及其它状况和操控信息。CPSR在每种反常形式下都有一个对应的物理寄存器—程序状况保存寄存器SPSR。当反常出现时,SPSR用于保存CPSR的值,以便反常回来后康复反常产生时的作业状况。

ARM的寻址方法:

所谓寻址方法便是处理器依据指令中给出的地址信息来寻觅物理地址的方法。

当即寻址:操作数自身就在指令中给出。

ADD R0, R0,#1

ADDR0,R0,#0x3f

第二个源操作数即为当即数,要求以“#”为前缀。

寄存器寻址:运用寄存器中的数值作为操作数。

ADDR0,R1,R2

寄存器直接寻址:以寄存器中的值作为操作数的地址,而操作数自身存放在存储器中。

ADDR0,R1,[R2]

LDR

基址变址寻址:将寄存器(该寄存器一般称为基址寄存器)的内容与指令中的给出的地址偏移量相加,然后得到一个操作数的有用地址。

LDRR0,[R1,#4]

LDRR0,[R1,#4]!

LDR R0,[R1],#4

LDR R0, [R1,R2]

多寄存器寻址:一条指令能够完结多个寄存器值的传送。最多完结16个通用寄存器值得传送。

LDMIAR0,{R1,R2,R3,R4}

该指令的后缀IA表明在每次履行完加载后,R0按字长添加,因而,指令可将接连存储单元的值传送到R1 -R4。

相对寻址:以程序计数器PC的当时值为基地址,指令中的地址标号作为偏移量,将两者相加之后得到操作数的有用地址。

BLNEXT

……

NEXT

……

MOV PC,LR

仓库寻址:仓库是一种数据结构,运用一个称作仓库指针的专用寄存器指示当时的操作方位,仓库指针总是指向栈顶。

递加仓库:向高地址方向成长

递减仓库:向低地址方向成长

满仓库:仓库指针指向最终压入仓库的有用数据项

空仓库:仓库指针指向下一个要放入数据的空方位

ARM指令集

跳转指令:完结程序流程的跳转,1.运用专门的跳转指令。2.直接向程序计数器PC写入跳转地址值。(跳转之前结合运用 MOV LR,PC.保存将来回来地址值,然后完结在4G接连的线性地址空间的子程序调用。)

指令:B、BL、BLX、BX

B{条件}

B Label

程序无条件跳转到标号Label处履行

CMP

BEQ Label

当CPSR寄存器中的Z条件码置位时,程序跳转到标号Label处履行。

BL{条件} 方针地址

在跳转之前,会在寄存器R14中保存PC当时值。

BLX 方针地址

从ARM指令集跳转到指令中所指定的方针地址,并将处理器的作业状况由ARM状况切换到Thumb状况,该指令一起将PC的当时内容保存到寄存器R14中。因而,当子程序运用Thumb指令集,而调用者运用ARM指令集时,能够经过BLX指令完结子程序的调用和处理器作业状况的切换。一起,子程序的回来能够经过将寄存器R14值到PC中来完结。

BX{条件} 方针地址

方针地址能够是ARM指令,也能够是Thumb指令。

B

BL

BLX

BX

数据处理指令:数据传送指令、算术逻辑运算指令和比较指令

MOV{条件}{S} 意图寄存器,源操作数

MOV指令完结从另一个寄存器、被移位的寄存器或进一个当即数加载到意图寄存器。其间S选项决议指令的操作是否影响CPSR中条件标志位的值,当没有S时指令不更新CPSR中条件标志位的值。

MOV R1, R0,LSL#3

MVN{条件}{S} 意图寄存器,源操作数

MVN指令可完结从另一个寄存器、被移位的寄存器、或将一个当即数加载到意图寄存器。与MOV指令不同之处是在传送之前按位被取反了,即把一个被取反的值传送到意图寄存器中。其间S决议指令的操作是否影响CPSR中条件标志位的值,当没有S时指令不更新CPSR中条件标志位的值。

MVNR0,#0xff

CMP{条件}操作数1,操作数2

CMP指令用于把一个寄存器的内容和另一个寄存器的内容或当即数进行比较,一起更新CPSR中条件标志位的值。该指令进行一次减法运算,但不存储成果,只更改条件标志位。标志位表明的是操作数1与操作数2的联系(大、小、持平),例如,当操作数1大于操作数2时,尔后的有GT后缀的指令将能够履行。

CMP R1,R0

CMPR1,#100

TST{条件} 操作数1,操作数2

TST指令用于把一个寄存器的内容和另一个寄存器的内容或当即数进行按位的与运算,并依据运算成果更新CPSR中条件标志位的值。操作数1是要测验的数据,而操作数2是一个位掩码(掩码是一串二进制代码对方针字段进行位与运算,屏蔽当时的输入位),依据测验成果设置相应标志位。当位与成果为0时,EQ位被设置。

TSTR1,#%1

ADD{条件}{S} 意图寄存器,操作数1,操作数2

ADD指令用于把两个操作数相加,并将成果存放到意图寄存器中。操作数1应是一个寄存器,操作数2能够是一个寄存器,被移位的寄存器,或一个当即数。

ADDR0,R1,R2,LSL#1

SUB{条件}{S} 意图寄存器,操作数1,操作数2

SUB指令用于把操作数1减去操作数2,并将成果存放到意图寄存器中。操作数1应是一个寄存器,操作数2能够是一个寄存器,被移位的寄存器,或一个当即数。

SUBR0,R2,R3,LSL#1

AND{条件}{S} 意图寄存器,操作数1,操作数2

AND指令用于在两个操作数上进行逻辑与运算,并把成果放置到意图寄存器中。操作数1应是一个寄存器,操作数2能够是一个寄存器,被移位的寄存器,或一个当即数。该指令常用于屏蔽操作数1的某些位。

ANDR0,R0,#3

ORR{条件}{S} 意图寄存器,操作数1,操作数2

ORR指令用于在两个操作数上进行逻辑或运算,并把成果放置到意图寄存器中。操作数1应是一个寄存器,操作数2应是一个寄存器,被移位寄存器,或一个当即数。该指令常用于设置操作数1的某些位。

ORRR0,R0,#3

BIC{cond}{S} Rd,Rn,operand2

BIC指令用于铲除Rn中的某些位,并把成果存放在Rd中,操作数operand2为32位的掩码,假如掩码中设置了某一位为1,则铲除这一位。

B%&&&&&%R0,R0,#11

MUL{条件}{S}

MUL指令完结将操作数1与操作数2的乘法运算并把成果放置到意图寄存器中,一起能够依据运算成果设置CPSR中相应的条件标志位。其间,操作数1和操作数2均为32位的有符号数或无符号数。

MUL

MULS

程序状况寄存器拜访指令

ARM微处理器支撑程序状况寄存器拜访指令,用于在程序状况寄存器和通用寄存器之间传送数据。

MRS{条件} 通用寄存器,程序状况寄存器(CPSR或SPSR)

MRS的用途是将状况寄存器中的内容传递到通用寄存器中。

1、当需求修正程序状况寄存器中内容时,可用MRS进程序状况寄存器的内容读入到通用寄存器,修正后再写回程序状况寄存器。

2、当在反常处理或进程切换时,需求保存程序状况寄存器的值,可先用MRS读出程序状况寄存器的值,然后保存。

MRS R0,CPSR

MSR{条件}程序状况寄存器(CPSR或SPSR)_<域>,操作数

MSR指令用于将操作数的内容传递到程序状况寄存器的特定域中。其间,操作时能够是通用寄存器或当即数。<域>用于设置程序状况寄存器中需求操作的位,32位的程序状况寄存器可分为4个域:

位[31:24]为条件标志位域,用f表明;

位[15:8]为扩展位域,用x表明;

MSR CPSR,R0

MSRCPSR_c,R0