CRC是一种实践通讯中运用很广泛的线性分组码,具有很强的检错才能,但没有纠错才能。在运用的时分可以依据不同的场合挑选硬件电路或许软件算法来完结,硬件完结的原理是依据特定的CRC多项式对输入信号和上一次校验成果进行移位异或操作,得到本次CRC校验成果;软件则可以选用多种不同算法进行核算,相应的时刻复杂度会有所不同

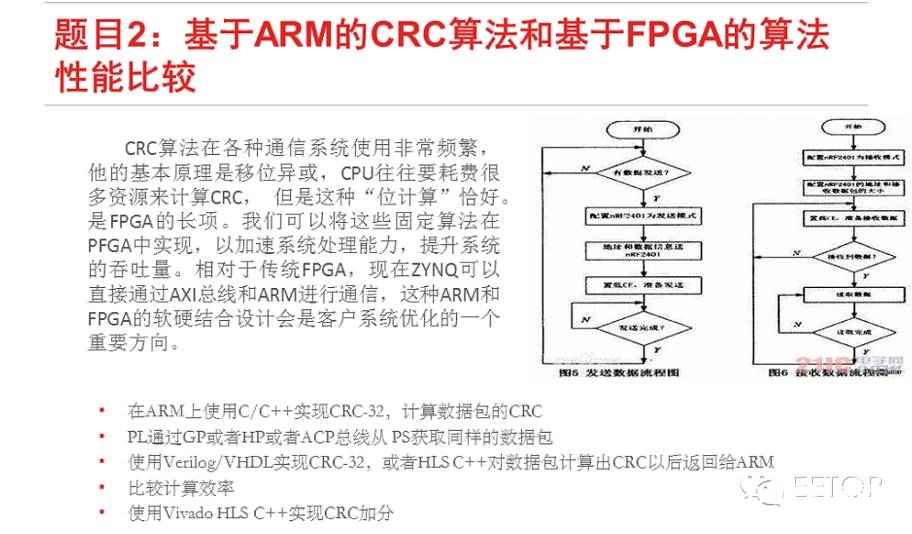

标题剖析:本标题的规划意图在于运用FPGA中硬件资源对某些流程固定的软件算法进行加快,即algorithm-hardware codesign,是软硬协同规划中更为具体的一种办法,本标题中的CRC算法仅仅其间一种实例。这种由硬件电路完结的软件算法一般可以很大程度上的下降核算时刻,价值仅是FPGA内部所耗费的一些逻辑、存储资源,但关于现在的FPGA芯片来讲是完全可以承受的。本标题的建立将充沛验证MicroZed开发板中Zynq系列芯片的优势,因为它集成了高功用ARM处理器内核、足够外设资源和FPGA逻辑资源,关于软硬件协同规划的嵌入式运用,是很好的挑选。

(二)进程阐明

1.软件学习:Vivado+ SDK

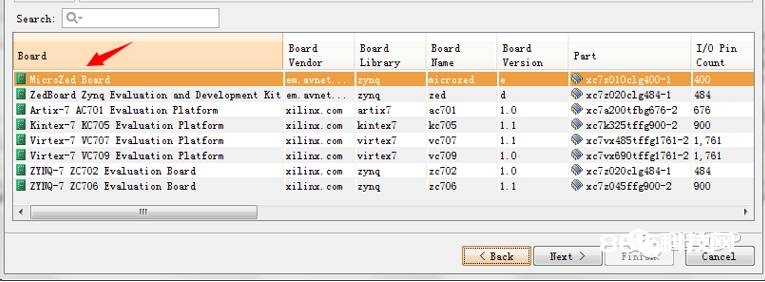

要在两周时刻内完结应战标题,需赶快学会标题规则的Vivado + SDK软件开发流程。其间第一个方针就是要建立起依据ARM CortexA9的嵌入式体系,才可以进行下一步CRC算法的完结和调试。在Vivado 2013.4及以上的版别中都包括支撑MicroZed开发板的硬件界说和板级支撑包,新建工程时选中就会将开发板的一切信息导入到工程中,非常便利。

有许多网友或MicroZed、Zynq运用者上传过很具体的图文开发流程,在这里我就不再重复演示了。这些教程包括了从入门级到专家级的MicroZed开发板、Vivado/SDK软件运用教程乃至代码。正是因为这些人乐于共享的精力,才使得国内FPGA规划技术可以快速、深化的发展起来。在这里跟我们引荐一个名字叫“亚当泰勒玩转MicroZed”的连载,中英版都有,但英文版的更全一些。这个入门级的图文教育可以教我们怎么从一个新手快速了解依据Vivado+SDK的MicroZed开发流程,本标题可以顺利完结离不开这位外国友人的协助。连载中除了阐明开发板的运用、软件规划/调试流程外,还包括部分PS根本外设的运用办法,比方GPIO、中止操控器、三重定时器以及PS与PL进行通讯运用的AXI4总线建立/调试办法等。在这里提一下用Vivado进行规划的一个典型特色:在建立嵌入式硬件体系时,它选用的是模块图的办法比PlanAhead更直观一些,下图就是本标题终究规划的体系模块图:

其间包括了CortexA9处理器体系、AXI总线互连IP以及PL完结的自界说CRC算法IP。

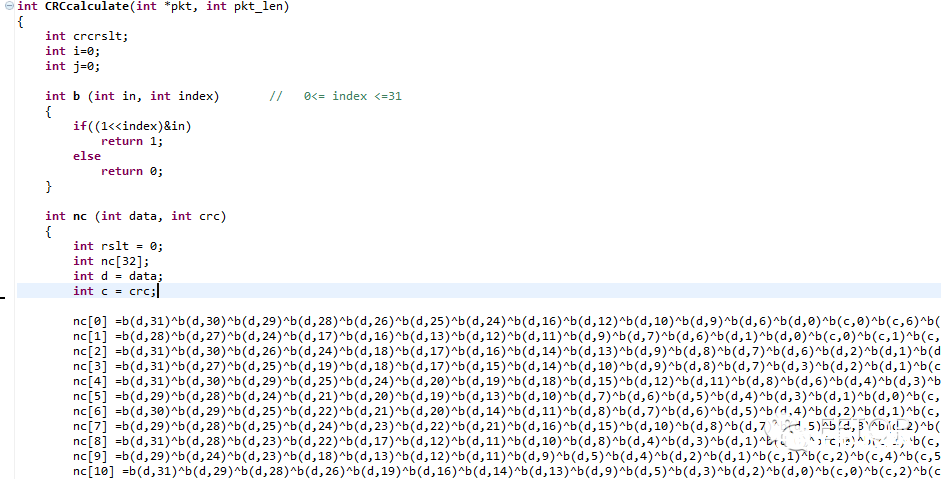

2.依据ARM的CRC算法完结(PS端)及功用比较流程

软件CRC算法完结办法有许多种,现在大多运用查表法,具有较低的算法复杂度和运转时刻。可是此标题的意图在于比较硬件加快对某种软件算法的功用进步,需求运用与PL端相同的算法完结才更有压服性。所以在ARM中完结的32bit CRC校验选用依据出产多项式按bit异或的办法,需求将输入的32bit整型数据拆分为32个单bit数据进行运算,然后将成果重新组合为32bit整型,如下所示

别的,为保证以太网数据包CRC校验的真实性,在本标题中运用了Wireshark从网络中随意抓取的一个ARP播送包,如下图:

下面向我们阐明本标题进行功用比较时选用的流程:

首要,在进行功用比较时,一致时刻规范是必要的。因为PS端进行时刻核算选用的是TTC三重定时器,将其作业频率设为体系内部ARM_PLL发生的CPU_1X,约为133MHz。一起将其经过FCLK_CLK0信号输出到PL端用作CRC校验模块的作业时钟,可以保证PS端与PL端的计时规范一致性,如下图:

别的,为表现CRC循环冗余校验中的“循环”特色,自己将ARP数据包的完好校验进程分步出现了出来。运用了开发板上仅有的GPIO按键进行进程操控,每次按键发生一次中止,履行一次中止比较程序。每次中止比较程序进行比照的数据包都会比上一次多一组(32bit),直到完好的ARP数据包完结CRC校验,则持续重复初始的校验进程。

按键中止程序中,首要进行PS端的CRC校验和计时,之后将数据包经过GP总线传送到PL端,PL端接纳到完好数据包后进行主动校验和计时,完结后将成果回来PS端,流程如下:Reset Timer—>Start Timer—>Start CRC Calculate Function—>StopTimer—>Get Counter Value—>Output PS Result—>.Packet Transmit—>StartPL CRC FSM—>Read Back Result—> Output PL Result—>Reset Control Reg—>Return.

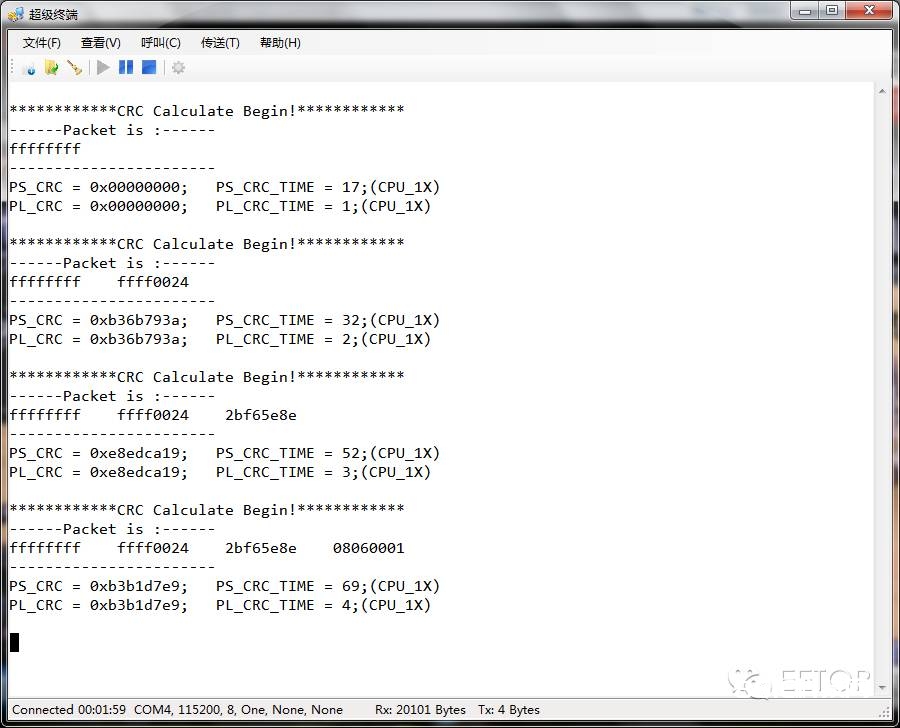

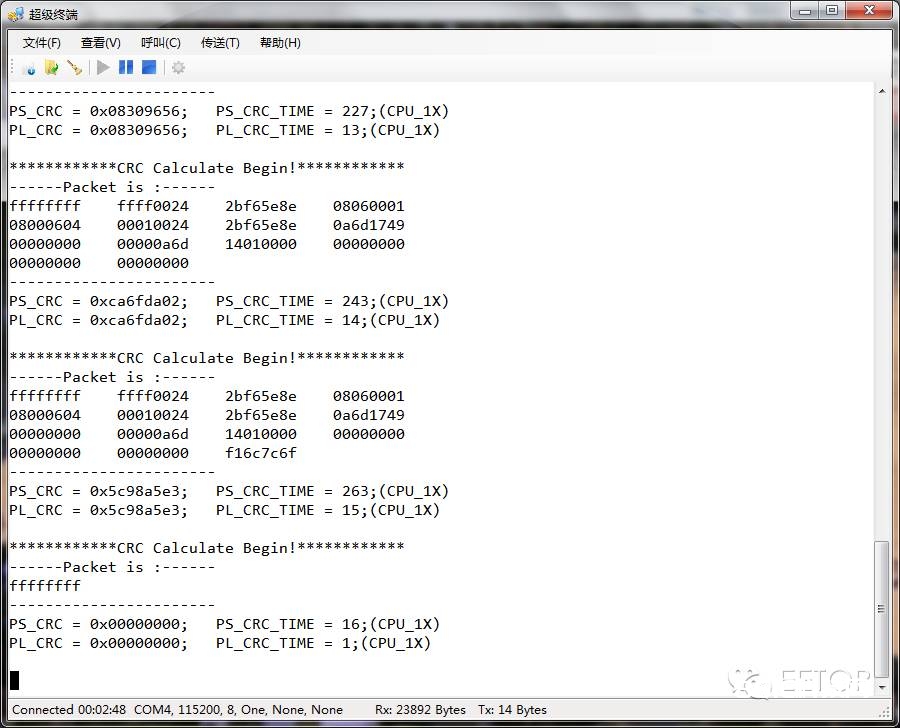

按键中止比较程序输出内容如下:

Ø每次按键触发后,首要输出提示:

“**********CRC Calculate Begin!**************”

Ø随后输出本次PS与PL进行CRC校验的数据:

“———Packet is :———–”

“数据包内容”(32bit为一组)

“———————————”

Ø首要输出PS端CRC校验成果以及核算时刻:

“PS_CRC = 0x……; PS_CRC_TIME = ……”

Ø之后输出PL端CRC校验成果以及核算时刻:

“PL_CRC = 0x……; PL_CRC_TIME = ……”

接连按下按键,则超级终端回来内容如下:

以上就是本标题的CRC算法比较流程以及PS端的完结计划,接下来介绍PL端的完结办法。

3.依据FPGA的CRC算法完结(PL端)

标题要求运用GP,HP,ACP总线完结数据帧的传输,怎么完结数据帧的传输并界定帧的开端和截止是使命的要点。因为数据帧的长度并不大,也没有高速传输的要求,因而选用了最常用的GP总线。

完结计划:自己挑选经过GP总线对自界说外设myip_crc_0中的4个操控/数据寄存器reg0~3进行读写,来完结数据帧的传输以及成果的回来功用。其间reg0为操控寄存器,包括符号帧开端的SOP和帧截止的EOP信号;reg1为数据寄存器,用于接纳对端发送的32bit数据帧;reg2和reg3用于存储CRC校验的成果和耗费的时刻。在一次帧传输开端后,一切接纳的32bit数据会被主动存入FIFO中,当EOP信号有用时开端对FIFO内的悉数数据进行接连的CRC校验并进行计时,校验完结后将成果存储到寄存器中并回来给PS端。

规划细节:生成带有AXI从接口的自界说IP核是本标题规划中的一个要点,需求挑选好对应参数,并一起生成驱动以备软件运用:

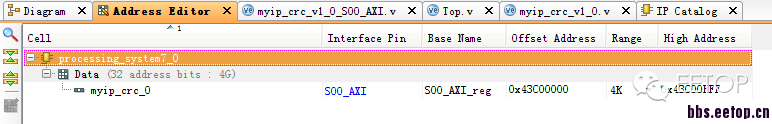

建立好新的IP后需求在AddressEditor中为其分配地址空间

然后进入IP Packager中对其进行各项装备

而且每次修正后记住进入“Reviewand Package”中点击”Re-package IP”进行保存。

IP核生成之后,下一步需求对AXI从接口模块源文件“myip_crc_v1_0_S00_AXI.v”进行部分修正并在其间例化自界说功用模块。该源文件包括AXI Slave接口中每个输入输出信号的含义注释以及AXI协议功用完结部分的代码注释,便利规划人员进行阅览和修正。

在myip_crc_v1_0_S00_AXI.v中除了例化自界说的模块外,对协议自身部分的代码也进行了少量修正,使寄存器reg0~reg3可以一起被PL端进行赋值,而且操控向reg1写入的数据主动写入FIFO中。当接纳到EOP信号后,发动CRC运算,接连读取FIFO中的数据包并进行校验,直到FIFO读空后完结本次校验并将成果写入寄存器reg2、reg3中回来。

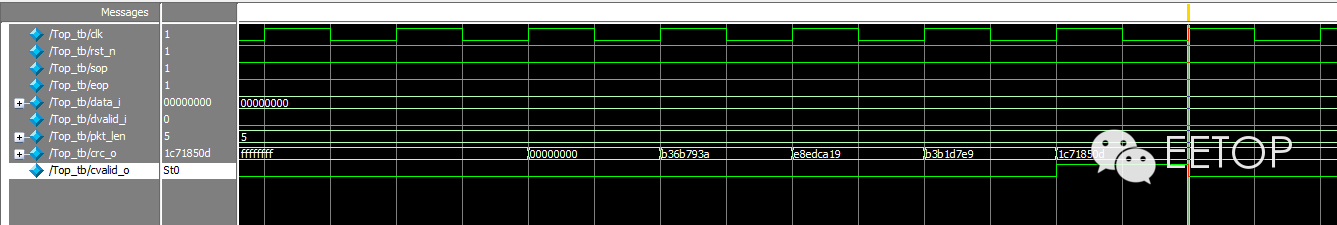

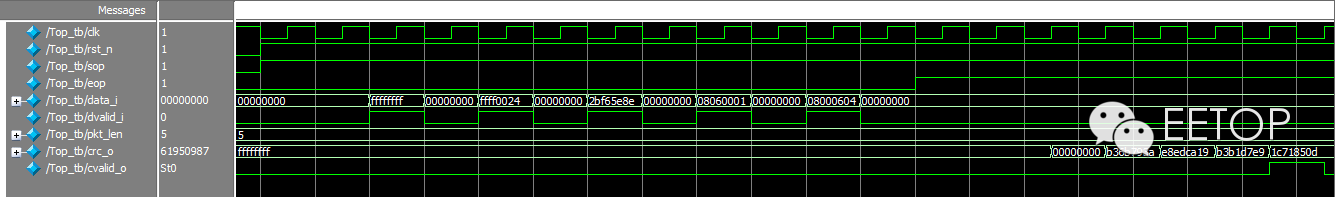

仿真成果:

下图为数据包接纳及校验进程仿真,测验的是数据包长度为五的状况

下图为五组接连的校验成果,与超级终端回来的初始五次比较成果符合

以上就是PL端CRC算法的规划完结办法。

(三)总结

本次为期两周的Zynq极客应战赛告于阶段了,关于楼主来说这次竞赛的应战性还不小。困难首要表现在竞赛之前我仅有过MicroBlaze + XPS的SOC经历,没有触摸过Zynq器材和Vivado。在短时刻内了解软硬件、规划流程需求非常专心的学习和测验,而且寻觅适宜的学习资源。别的,时刻也是一个问题,在应战期间突发的工作会打乱规划调试的进展,真实用来进行开发的时刻也就一个星期左右。优势在于之前是做核算机网络运用方面的,对标题二中CRC算法的FPGA规划完结有必定经历。终究,在规则的时刻内完结了标题中的前四个要求,仅仅还有一些主意未能及时完结,比方运用MAC操控器从网络中实时抓取长度可变、内容较大的数据包进行CRC校验,使本次规划具有更大的运用含义并进步规划难度。

最终,再次感谢EETOP论坛给予本次应战时机。期望越来越多的FPGA、嵌入式爱好者参加到其间,从中学习、考虑、体会,收成更多的常识和技术。一起也祝福我国的电子规划、制作职业可以迅速发展,不断进步!