摘要:针对单片机运用规划中的资源缺乏、牢靠性差和软件晋级问题,规划了一款依据Cortex—M3内核的双核板。该双核板在不添加开发难度的状况下使单片机资源翻倍;经过两个MCU之间的使命合理分工和彼此监督,提高了全体体系的牢靠性;运用CAN总线完结主机与上位机的通讯和晋级程序的下载,并经过操控引脚完结依据ISP功用的从机软件晋级。

导言

在单片机的运用规划中,常常会遇到如下问题:其一,某一了解类型的单片机功用可用,性价比也很好,但限于某种内部资源(如串口数、A/D路数等)缺乏,不得不选用更高级或不太了解的单片机,形成资源的糟蹋和开发周期的延伸。其二,在海洋长途监测等重要范畴,对操控器的牢靠性要求较高,而单片机存在死机的可能性,即便可以经过装备看门狗来防止这种状况,但这种“粗犷”的复位方法并不合理(首要,复位打乱了正常的数据收集和处理作业,导致重要数据丢掉;其次,即便能记录下复位时刻和次数,但复位原因和复位前状况等信息无法侦测,一些本该处理的BUG被掩盖,导致频频复位)。其三,由于开发周期缺乏或测验不充分,导致设备投入运转后呈现毛病,而这些毛病往往经过软件晋级的方法可以处理,但由于设备的运用场所比较特别(如水下),导致软件晋级的本钱很高。

针对上述3种状况,在实践的项目运用中规划了依据STM32的双核板,较好地处理了资源缺乏、稳定性差和依据CAN总线的长途晋级等问题,具有性价比高、开发周期短等长处。

1 双核板规划

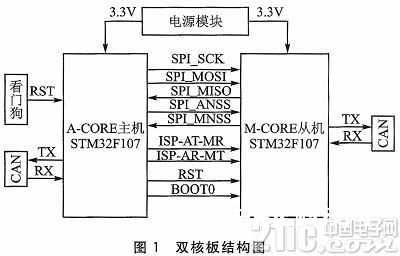

STM32系列单片机具有高性能Cortex—M3内核和外设,功耗低,集成度高,性价比高。别的,ST公司还供给了外设的规范库函数,屏蔽了底层硬件细节,可以使开发人员轻松完结产品的开发,缩短体系开发时刻。正由于如此,STM32系列单片机得到了开发者的喜爱。其运用范畴和客户群不断扩大。其间的 STM32F107归于互联型系列,具有以太网和CAN总线接口,在数据通讯方面具有共同的优势。一种依据STM32F107的双核板如图1所示。

图1中,两个STM32F107最小体系模块别离称为A-CORE和M-CORE,A-CORE具有外看门狗,为主机模块;M-CORE不具有外看门狗,但其RST/BOOT0引脚受A-CORE的操控,可以经过串口完结ISP总线晋级,为从机模块。由于A-CORE和M-CORE均具有电源体系、复位电路和下载接口等调试所需的根本要素,因而可以预先焊接和调试好。在详细项目的开发运用中,将双核板作为一个独立的元件嵌入,一些软件可以提早验证和编写,大大缩短了产品的开发周期。

在正常作业时,主从机两个模块独立作业,两者经过SPI总线彼此通讯。SPI接口传输速率可到达18 Mbps,比I2C和UART通讯要快得多。由于选用双核,通用I/O引脚明显增多,不只可以完结愈加杂乱的规划,并且降低了布局布线的难度。关于了解 STM32的开发者来说,开发难度根本不变,而可运用的资源却简直成倍添加。

在该双核板的规划中,还考虑了A—CORE对M—CORE的在线晋级问题。图1中M—CORE的RST、BOOT0两个引脚受A—CORE操控,来完结 M-CORE的复位和复位地址挑选;而ISP-AT-MR和ISP-AR-MT两个引脚则是作为USART接口,完结对M-CORE的ISP晋级。

2 牢靠性规划

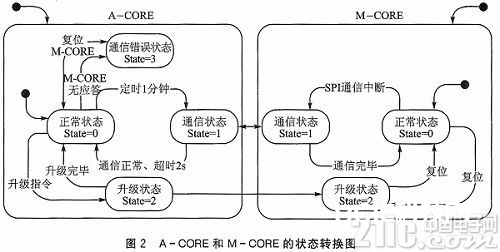

在本文的运用中,A—CORE和M—CORE分工合作。A—CORE首要完结体系的办理作业,如人机交互、数据存储、通讯等;M—CORE首要完结信息收集、外部设备操控等功用,这样规划的长处是功用清楚、负荷分管。担任收集操控的M—CORE可以集中精力完结数据收集和辅佐的操控作业;而担任办理的A— CORE除了完结人机交互、数据存储和通讯外,还需求守时建议与M—CORE的通讯,以确保彼此监督。

M—CORE收到A—CORE的指令后,会将当时的作业状况报告给A—CORE,再由A—CORE经过CAN总线等手法上传给更高层的通讯主机。假如A— CORE发现M—CORE不能正常回复信息,则阐明M—CORE处于不正常状况,必要时可完结对M—CORE的“危机干涉”。例如,在接连屡次均不能正常通讯的状况下,可以以为M—CORE已处于死机状况,A—CORE将复位M-CORE。A—CORE和M—CORE的状况转换图如图2所示。

明显,这种双核结构和守时通讯机制,可以使每个MCU知道对方的作业状况。尽管在结构上分出了A—CORE和M—CORE,但由于每个MCU都有CAN总线与通讯主机相连,因而每个MCU都可以独自通向主机报告作业状况,报告的内容都可以经过CAN总线接纳到,因而起到了彼此监督的效果。

3 依据CAN总线的软件晋级

具有长途软件晋级的设备具有更广泛的适用性,可以在设备装置到位后,经过软件晋级在线修正一些问题,不光节约人力物力,也可以使设备的功用逐步完善。

双核板具有CAN总线,该总线不光是数据交换的通道,也是软件晋级的通道。上位机可以经过CAN总线将需求晋级的程序代码下传到A—CORE,A— CORE操控M—CORE的RST/ BOOT0引脚,使M—CORE复位并进入ISP状况,然后完结在线晋级。由此可见,要完结依据CAN总线的在线软件晋级,需求3个条件:一是待晋级体系 M—CORE本身具有ISP功用,能经过串口完结程序的下载;二是A—CORE本身集成CAN总线,可经过CAN总线接纳上位机发送的待晋级程序代码;三是A-CORE可以操控M—CORE的RST/BOOT0引脚,完结在线晋级。

3. 1 STM32的ISP晋级

ISP(In-System Programming)方法相关于传统的并行编程方法有了极大的前进,无需将单片机从电路板上卸下就可进行编程。STM32系列芯片复位时,可以经过BOOT1和BOOT0的逻辑电平来决议体系的发动形式,见表1所列。

体系复位时,CPU依据这两个引脚的逻辑电平把相应形式的开端地址映射到发动空间(0x 0000 0000)。在发动推迟之后,CPU从坐落0x0开端的发动存储区履行代码。由于实践运用中很少从内嵌SRAM中发动,故可将BOOT1引脚直接设置为低电平,只经过判别BOOT0引脚的凹凸电平来挑选从用户闪存或体系存储器中发动。若复位时BOOT0的逻辑电平为高,则复位后从体系存储器发动,可经过 USART1与Bootloader进行通讯。

STM32芯片具有开放式的在线烧录ISP协议,答应第三方依据该协议编写ISP下载软件,对STM32芯片进行FLASH的更新操作。在进行ISP方法晋级时,先发送0x7F完结主动波特率匹配,可以辨认最高115 200 bps的串口波特率。假如正确回应0x79,表明指令履行正常。握手正确后,就可以经过ISP指令完结对STM32的ISP操作,完结FLASH的擦除和编程。

3.2 FLASH分区存储

STM32F107片内集成256 KB FLASH和64 KBSRAM,FLASH由主存储块(Main Block)和信息块(Information Block)组成。主存储块用于寄存用户程序,每页2 KB,共128页,容量为32K×64位,地址规模为0x0800 0000~0x 0803 FFFF;信息块容量为2 360×64位,分为发动程序代码和用户挑选字节。发动程序代码从0x 1FFF B000~0x 1FFF F7FF,共18 KB,用户挑选字节从0x 1FFF F800~0x 1FFF F80F,共16字节。

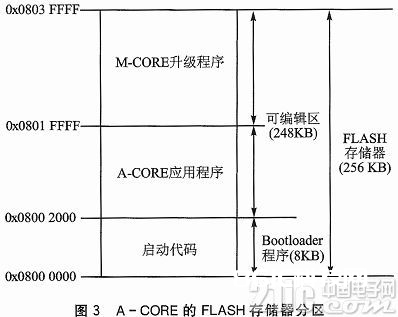

A-CORE的FLASH存储器分区如图3所示。

0x0800 0000~0x0800 1FFF,共8 KB空间,为Boot-loader代码空间。

0x0800 2000~0x0801 FFFF,为120 KB空间,寄存A-CORE本身程序。

0x0802 0000~0x0803 FFFF,为128 KB空间,寄存M-CORE运用程序。

上述空间分配,尽管晋级程序的空间受到了约束,但在大多数状况下是可行的,由于A—CORE和M—CORE使命分管,其本身的程序量均缺乏总FLASH容量的一半。假如呈现了空间缺乏的现象,完全可以换用更大容量的MCU。

3.3 软件晋级流程

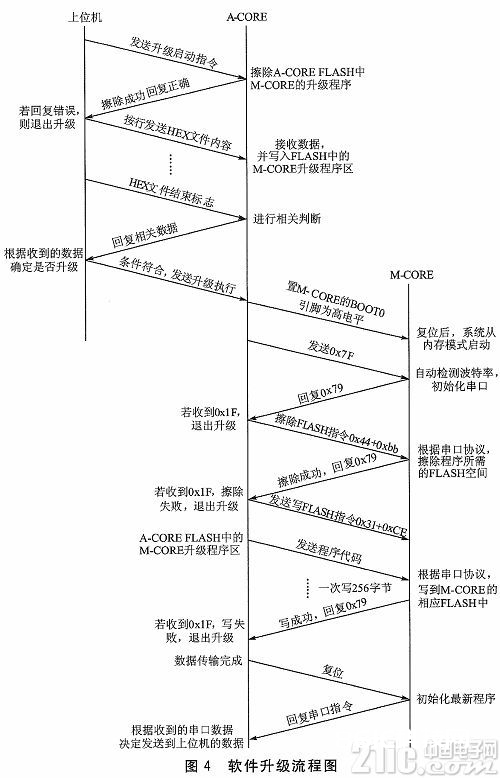

要完结A—CORE对M—CORE的软件晋级,其进程可以分为两个阶段:依据CAN总线的数据传输和依据USART的ISP进程。

(1)依据CAN总线的数据传输

当M—CORE需求更新用户程序时,上位机将编译成功的M—CORE晋级程序的HEX文件经过CAN总线发送到A—CORE。上位机先发送晋级指令,A—CORE接纳到晋级指令后,将FLASH中M—CORE晋级程序区(0x 0800 2000~0x 0801 FFFF)擦除,擦除成功后回复上位机,若回复错误信息,则退出晋级;上位机接纳到回复后,按行发送HEX文件内容,A—CORE接纳到数据后,顺次写入A—CORE的M—CORE晋级程序区(0x 08002000~0x 0801 FFFF)中,接纳结束后向上位机发送写入结束指令。

(2)依据USART的ISP进程

当A-CORE接纳到上位机发送的晋级履行指令后,晋级流程如下:

①置M-CORE的BOOT0引脚为高电平,然后置RST引脚为低电平,复位M-CORE,使其从体系的内存形式发动,然后将RST引脚拉高。

②A—CORE向M—CORE发送0x7F,M—CORE接纳该数据,并依据该数据与A—CORE主动匹配波特率,进行回复。若回复0X79,则表明可以进行相关擦除和写FLASH操作了,若回复0x1F,则晋级失利。

③A—CORE收到正确的应对,则发送0x44+0xBB,依据程序巨细擦除FLASH,依据STM32F107内部固有的Bootloader串口协议,擦除完结后回复A—CORE。

④A—CORE等候接纳M—CORE的回复,收到正确的应对之后,发送0x31+0xCE,把存储到A—COREFLASH中的M—CORE晋级程序区的内容写到M—CORE的相应FLASH中,一次写256个字节,直到把一切的用户程序写入用户存储区。

⑤A—CORE操控BOOT0引脚,并操控RST为低电平,对M—CORE进行硬件复位,M—CORE从头初始化程序,然后运转刚刚更新的用户程序。

软件晋级交互流程如图4所示。

结语

依据STM32的双核板可以有用处理单个微处理器内存资源不行的问题,在根本不添加开发难度的基础上,使体系资源加倍添加,可以完结更为杂乱的运用规划;经过A—CORE和M—CORE彼此监控,提高了整个体系的牢靠性,可以有用发现软硬件危险;经过双核有用的使命分工,减小了单个MCU的担负,使体系运转愈加牢靠;依据ISP和CAN总线的长途晋级体系,有用运用了CAN总线通讯速率高、抗干扰能力强、传输间隔远的特色以及STM32系列本身具有的 ISP功用,在设备装置今后仍可以晋级程序,既方便了智能设备的开发,又降低了保护本钱。

- STM32单片机中文官网

- STM32单片机官方开发工具

- STM32单片机参阅规划