1、时刻标尺:格局:`timescale 仿真时刻单位/时刻精度,举例:`TImescale 1ns/100ps,仿真时刻单位位1ns,可是仿真时刻精度能够到达100ps。

我们应该注意到有个#符号,该符号的意思是指推迟相应的时刻单位。该时刻单位由TImescale决议.一般在testbench的最初界说时刻单位和仿真精度,比方`TImescale 1ns/1ps,前面一个是代表时刻单位,后边一个代表仿真时刻精度。以上面的比如而言,一个时钟周期是20个单位,也便是20ns。而仿真时刻精度的概 念便是,你能看到1.001ns时对应的信号值,而假设TImescale 1ns/1ns,1.001ns时分的值就无法看到。

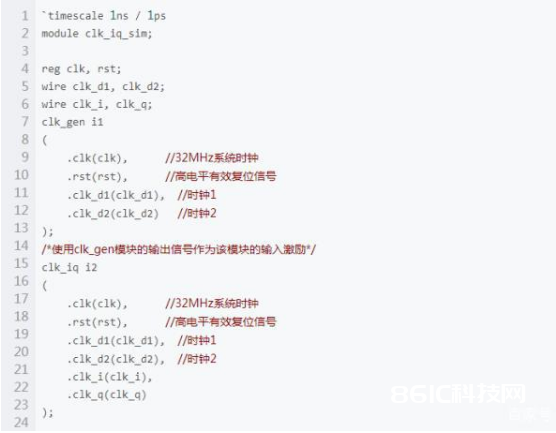

2、界说信号类型:本来模块中的输入信号,界说成reg 类型,本来模块中的输出信号,界说为wire类型,但这儿有个问题,如果在testbench中自身有一个模块需求,如用来发生时钟,送给要仿真的模块,那怎样界说信号类型呢?

其实仍是相同的界说,输入信号界说为reg类型,输出界说为wire类型,可是这个模块的输出送给仿真模块作输入,这个输入便是wire类型了,如下图所示的clk_d1和clk_d2这两个信号就只能界说为wire类型。

3.文件的输入测验数据

有时分,需求很多的数据输入,直接赋值的话比较繁琐,能够先生成数据,再将数据读入到寄存器中,需求时取出即可。用 $readmemb体系使命从文本文件中读取二进制向量,$readmemh 用于读取十六进制文件。例如:reg [7:0] mem[0:255] // 一个8bit位宽,长度256的寄存器组initial $readmemh ( “E:/readhex/mem.dat”, mem ) // 将.dat文件读入寄存器组mem中initial $readmemh ( “E:/readhex/mem.dat”, mem, 128, 1 ) // 参数为寄存器加载数据的地址开端和完毕。

4. 仿真成果写入文件

用函数 $fwrite ($fdisplay),函数功用,将数据写入到txt文件中(与fscanf正好相反)。$fwrite和$fdisplay的差异,$fwrite写下一个数不会主动转行,能够加\n来转行,$fdisplay则会主动转行。这儿只介绍$fwrite了,$fdisplay和$fwrite根本相同的写法。