文章转自ADI官网,版权归属原作者一切

在许多操控体系的中心区域,数模转化器 (DAC) 在决议体系的功用和精度方面起着十分要害的效果。本文将介绍两款新的精细 16 位 DAC,并对经过缓冲高速互补电流输出 DAC 的输出以完结变压器平等功用的构思进行评论。

片内体系基准电压源改进了精度

在恶劣环境下运转的电子体系或许有必要在忍耐极点温度的一起坚持超卓的精度和安稳性。此类体系往往需求多个分辨率高达 16 位的数模仿转化器。DAC 输出电压的精度终究取决于其基准电压的精度。为了在各种温度下完结这种水平的功用,一般会运用独自的精细基准电压源。可是,现在推出了包括低漂移基准电压源的全新精细四通道 DAC 系列,它的功用足够好,能够作为体系基准电压源。

基准电压源应在各种不同的负载、电源改动和温度条件下坚持安稳的电压。不幸的是,高功用的独立基准电压源往往体积较大、本钱贵重且功耗高 — 而片内基准电压源往往功用欠安。

直到现在,当体系规划师面对是将精细的 DAC 与外部基准电压源配对,仍是承受低功用片内基准电压源带来的苦楚时,往往不得不挑选 DAC 和外部基准电压源。他们不能盼望片内基准电压源的功用,因为这些电压源在各种温度下改动极大,而且往往短少最大 TC 标准,无法用作体系基准电压源。

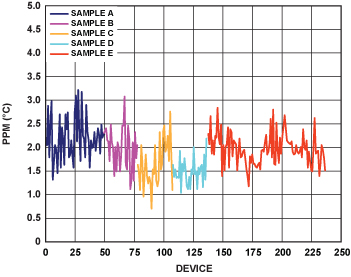

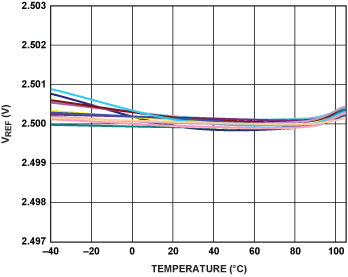

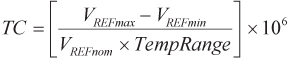

AD5686R 打破了这一常规。这款四通道、电压输出、16 位 nanoDAC+® 数模转化器供给了 2.5 V 片内基准电压源,而且最大温度漂移为 5 ppm/°C(一般为 2 ppm/°C)。这一功用水平与独立基准电压源的功用水平适当,使得片内基准电压源能够替代体系基准电压源,然后节约空间、本钱和功耗。5-ppm/°C 的最大漂移标准答应进行精细差错量核算。图 1 和图 2 显现了 AD5686R’ 片内基准电压源的功用。图 1 显现了五个独自采样批次的数百个 DAC 的温度系数分布图。图 2 显现了九个 DAC 在 –40°C 至 +105°C 温度规模内的实践输出电压。

办法:关于参阅电压,温度系数 (TC) 一般运用箱式办法确认,该办法在规则的温度规模内评价最大电压改动。TC 以 ppm/°C 为单位,依照以下方程式核算

其间

VREFmax 是在温度规模内测得的最大基准电压输出。

VREFmin 是在温度规模内测得的最小基准电压输出。

VREFnom 是标称基准输出电压。

TempRange 是规则的温度规模 (°C)。

低温系数是经过加热生产中零件并微调输出电压以补偿随温度改动的曲线而得出的。紧密合作能够保证电阻差异不会影响基准电压源的功用,而且还让 DAC 到达极端超卓的 ±2-LSB 积分非线性 (INL) 标准。

关于 AD5686R/AD5685R/AD5684R

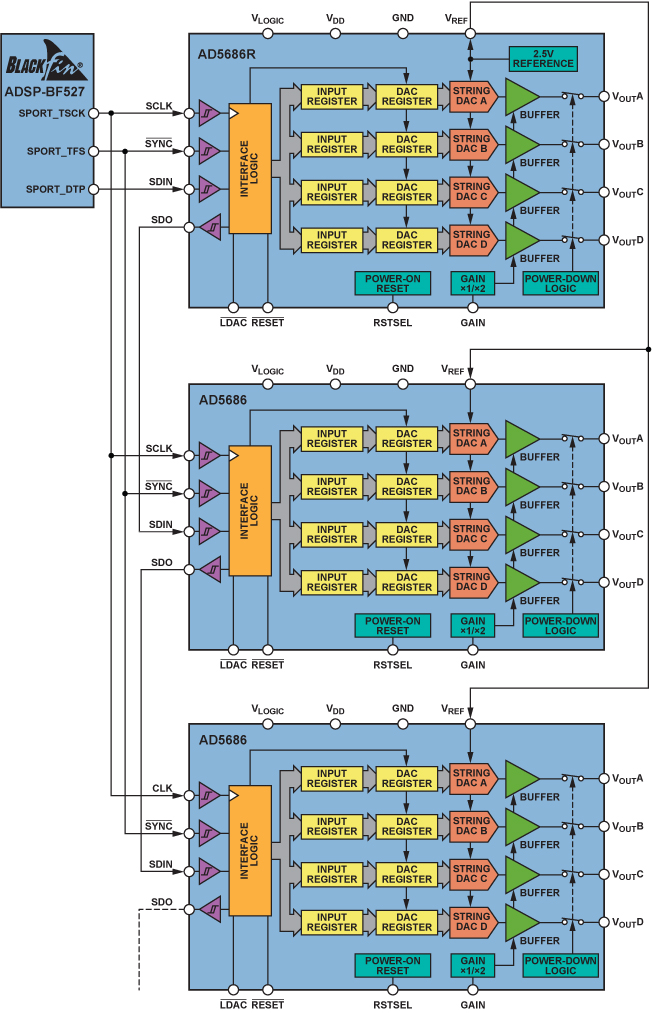

AD5686R/AD5685R/AD5684R 归于 nanoDAC+ 系列,它们是四通道、低功耗、16/14/12 位 DAC,供给经过缓冲的电压输出。商场对精度高、操作简洁且封装尺度细巧的数模转化器的需求日益增多,nanoDAC+ 系列正是为了满意这一需求而开发的。这些新器材包括已默许启用的片内 2.5V 2-ppm/°C 基准电压源。增益挑选引脚可将满度输出设置为 2.5 V (GAIN = 1) 或 5 V (GAIN = 2)。这些器材选用单个 2.7 V 至 5.5 V 电源,具有 0.1% 的最大增益差错、2 mV 的最大偏置差错和保证的单调性。它们供给 LFCSP (3-mm × 3-mm) 和 TSSOP 封装,而且 4-kV ESD 额定值突显了它们具有极端强壮的功用。DAC 输入可经过 1.8 V SPI 兼容接口进行编程。上电复位电路会保证 DAC 输出电源最多为 0 V,而且坚持此状况,直到进行有用的写入。复位引脚答应进行异步复位。基准电压源输出引脚答应在外部将片内基准电压源用作体系基准电压源。菊花链功用能够完结具有更多通道数量的体系。外部基准电压源型 AD5686/AD5685/AD5684 答应以最低的本钱在一切通道上共用单个基准电压源。图 3 显现了多通道体系中运用这些 DAC 的部分。

电压切换式 16 位 DAC 供给低噪声、快速设置和更佳线性度

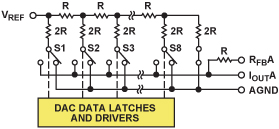

电阻梯式乘法 DAC 根据改动游戏规则的 10 位 CMOS AD7520—大约 40 年前推出—开端与反相运算扩大器合作运用,而且供给了便于虚拟接地的扩大器求和点 (IOUTA)(图 4)。

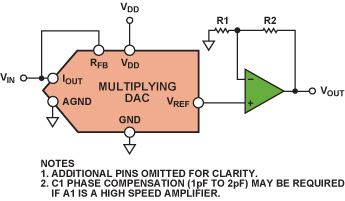

可是,它们还能够在少量情况下用于那些供给同相电压输出的电压切换式装备中,并将运算扩大器用作电压缓冲器(图 5)。在这里,基准电压 VIN 运用于 IOUT,而且输出电压 VOUT 可在 VREF 处供给。不久会推出针对此意图优化的 12 位版别。

快速开展到现在:跟着单电源体系越来越遍及,规划师面对的应战是如安在更高电压下极力坚持超卓的功用水平,一起坚持对功耗的操控。能够在此形式下运用的、具有更高分辨率(多达16 位)的器材受到了商场的更多喜爱。

在电压切换形式下运用乘法 DAC 的显着长处是不会发作任何信号反相,因而正基准电压会发作正输出电压。但在这种形式下运用时,R-2R 梯形架构也存在缺陷。与在电流操控形式下运用相同的 DAC 比较,与 R-2R 梯形网络串联运用的 N 通道开关的非线性电阻会下降积分非线性 (INL)。

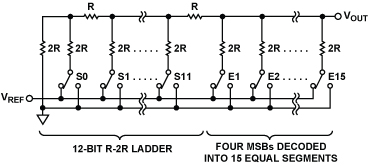

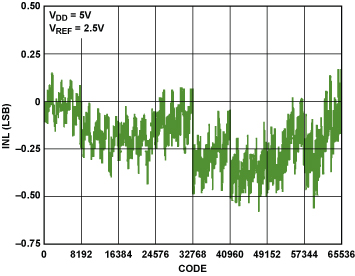

AD5541A 等新式高分辨率 DAC(如图 6 所示)现已开发出来,旨在战胜乘法 DAC 的局限性,一起坚持电压切换的优势。经过运用部分分段的 R-2R 梯形网络和辅佐开关,AD5541A 在 16 位分辨率下供给 ±1-LSB 的精度,而且无需调整整个指定温度规模(−40°C 至 +125°C)、11.8 nV/√Hz 噪声和 1-µs 树立时刻。

功用特性

树立时刻:图 7 和图 8 比较了处于电压形式下的乘法 DAC 和 AD5541A 的各自树立时刻。当输出上的容性负载减至最低时,AD5541A 的树立时刻约为 1 µs。

噪声谱密度:表 1 比较了 AD5541A 和乘法 DAC 的噪声谱密度。AD5541A 在 10 kHz 时的功用稍微好于乘法 DAC,但在 1 kHz 时的功用远远胜出乘法 DAC。

表 1. AD5541A 和乘法 DAC 的噪声谱密度比照

| DAC | NSD @ 10 kHz (nV/√Hz) | NSD @ 1 kHz (nV/√Hz) |

| AD5541A | 12 | 12 |

| MDAC | 30 | 140 |

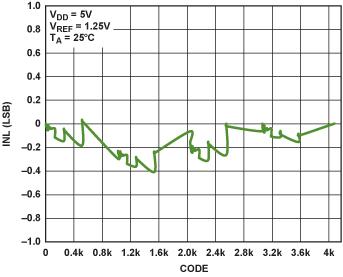

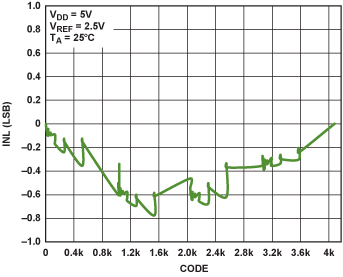

积分非线性:积分非线性 (INL) 用于丈量 DAC 的抱负输出与在去除增益和偏置差错之后的实践输出之间的最大差错。与 R-2R 网络串联运用的开关会影响 INL。乘法 DAC 一般选用 NMOS 开关。在电压切换形式下运用时,NMOS 开关的来历连接到基准电压,漏极连接到梯形网络,而且栅极由内部逻辑驱动(图 9)。

为了使电流流入 NMOS 器材,VGS 有必要大于阈值电压 VT。在电压切换形式下,VGS = VLOGIC – VIN 有必要大于 VT = 0.7 V。

乘法 DAC 的 R-2R 梯形网络经过专门规划,能够经过每个支腿均匀分配电流。这要求全体接地电阻(从每个支腿的顶部检查)有必要彻底相同。这可经过调整开关的小大来完结(每个开关的巨细与其导通电阻成正比)。假如一个支腿中的电阻发作了改动,流过此支腿的电流将会改动,从而导致线性差错。VIN 不能太大,不然会封闭开关,但它有必要大到足以将开关电阻坚持在较低的水平,因为 VIN 的改动会影响 VGS,从而导致导通电阻发作非线性改动,如下所示:

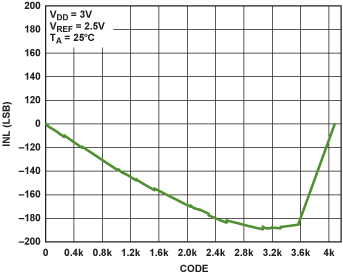

这种导通电阻的改动会使电流失衡并下降线性度。因而,乘法 DAC 的电源电压不能削减太多。反过来,为了坚持线性度,基准电压不该比 AGND 高出 1 V 以上。经过运用 5 V 电源,当从 1.25 V 基准电压源移至 2.5 V 基准电压源时,线性度开端下降,如图 10 和 11 所示。 当电源电压下降到 3 V 时,线性度彻底消失,如图 12 所示。

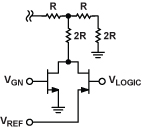

为尽或许削减此影响,AD5541A 选用了互补 NMOS/PMOS 开关,如图 13 所示。现在,开关的总导通电阻来自 NMOS 和 PMOS 开关的并联电阻。如前所述,NMOS 开关的栅极电压由内部逻辑操控。内部发作的电压 VGN 会设置抱负的栅极电压,以平衡 NMOS 的导通电阻与 PMOS 的导通电阻。开关的巨细会调整以与代码成份额,因而导通电阻将会与代码成份额。这样,电流将会调整,而且精度将得以坚持。当基准输入检测到随代码改动的阻抗时,它将由低阻抗源驱动。

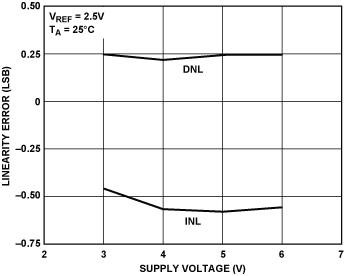

图 14 和 15 显现了选用 5 V 和 2.5 V 基准电压源的 AD5541A 的 INL 功用。

图 16 和图 17 显现线性度在广泛的基准和电源电压规模内改动很小。DNL 的功用体现与 INL 相似。AD5541A 线性度在温度和电源电压上指定;基准电压能够在 2.5 V 和电源电压之间改动。

关于 AD5541A 的更多信息

AD5541A 串行输入、单电源、电压输出 nanoDAC+ 数模转化器能够供给 16 位分辨率,而且具有 ±0.5-LSB 的典型积分和差分非线性。它十分适用于那些在电压切换形式下运用乘法 DAC 的运用场合。它在温度和电源电压上都体现杰出,获得优异的线性度,而且可用于需求精细直流功用和快速树立时刻的 3 V 至 5 V 体系。经过运用规模介于 2 V 和电源电压之间的外部基准电压,未经缓冲的电压输出可在 0 V 到 VREF 的规模内驱动 60 kΩ 的负载。该器材供给 1-µs 的树立时刻(½ LSB)、11.8 nV/√Hz 的噪声以及低故障率,十分合适布置在很多不同的医疗、航空航天、通讯和工业运用领域中。它的 3 线、低功率 SPI 兼容串行接口能够处理高达 50 MHz 的时钟输入信号。AD5541A 选用单个 2.7 V 至 5.5 V 电源,吸入电流仅为 125 µA。它供给 8 引脚和 10 引脚 LFCSP 以及 10 引脚 MSOP 封装,作业温度规模为 –40°C 至 +125°C,起价为 6.25 美元(1000 件)。

高速电流输出 DAC 缓冲器

因为不会添加噪声或耗费功率,变压器一般被认为是将高速电流输出 DAC 的互补输出转化成单端电压输出的最佳挑选。尽管变压器对高频信号操作杰出,可是它们不能处理许多外表和医疗运用所需的低频信号。这些运用场合需求运用低功率、低噪声和高速扩大器以将互补电流转化成单端电压。下面介绍的三个电路均可承受来自 DAC 的互补输出电流并供给单端输出电压。后两个电路的失真与变压器解决方案进行了比照。

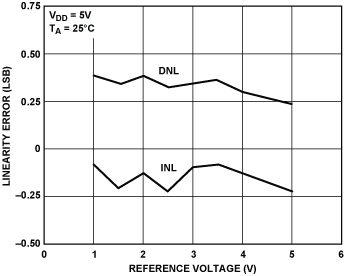

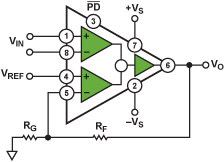

差分扩大器:AD8129 和 AD8130 差分-单端扩大器(图 1)用于第一个电路(图 2)。关于高频信号,它们具有极高的共模按捺才能。AD8129 对 10 以上的增益是安稳的,AD8130 则是单位增益安稳。其用户可调的增益能够经过两个电阻 RF 和 RG 的比率进行设置。不管增益怎么设置,AD8129 和 AD8130 的引脚 1 与引脚 8 上均具有十分高的输入阻抗。基准电压(VREF,引脚 4)能够用于设置偏置电压,然后将它乘以与差分输入电压相同的增益。

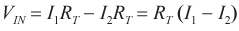

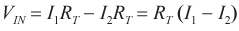

方程式 1 和 2 显现了扩大器的输出电压与 DAC 的互补输出电流之间的联系。终端电阻 RT 履行电流至电压的转化;RF 和 RG 的比率决议增益的巨细。在方程式 2 中,VREF 设置为 0。

|

(1) |

|

(2) |

在图 2 中,此电路选用了四通道、高速、低功耗 14 位 DAC,在此,互补电流输出级添加了低功耗 DAC 的速度并减小了低功耗 DAC 的失真。

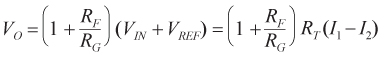

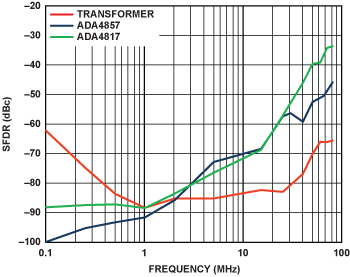

图 3 显现了在两个电源电压值下运用 DAC 和 AD8129 时的无杂散动态规模 (SFDR),该规模作为频率的函数,而且 RF = 2 kΩ,RG = 221 Ω,RT = 100 Ω,VO = 8 V p-p。之所以在这里挑选 AD8129,是因为它能够供给较大的输出信号、对 G = 10 安稳而且比 AD8130 具有更高的增益带宽积。在两种情况下,SFDR 一般均优于 55 dB,超越 10 MHz,而且在较低电源电压下改进了大约 >3 dB 。

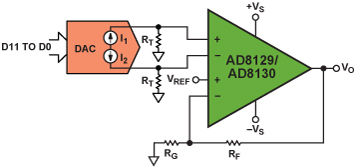

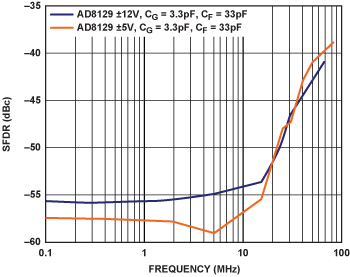

单位增益运算扩大器:第二个电路(图 4)运用包括两个 RT 电阻的高速扩大器。扩大器能够简略地经过 RT 将互补电流 I1 和 I2 转化成单端输出电压 VO。这一简略的电路不答应将扩大器用作增益模块进行信号扩大。

方程式 3 显现了 VO 和 DAC 输出电流之间的联系。失真数据经过与 RT 并联的 5 pF 电容器进行丈量。

|

(3) |

为了展现此电路的功用,DAC 与 ADA4857 和 ADA4817 运算扩大器调配运用,而且 RT = 125 Ω(CT = CF = 5 pF,与 RT 并联,以完结安稳性和低通滤波)。单 ADA4857-1 和双 ADA4857-2 是单位增益安稳、高速、电压反应型扩大器,具有低失真、低噪声和高压摆率。作为超声、ATE、有源滤波、ADC 驱动器等各种运用的抱负解决方案,它具有 850 MHz 带宽、2800 V/μs 压摆率和 10 ns 树立时刻(0.1%)—一切均选用 5 mA 的静态电流作业。凭仗广泛的电压规模(5 V 至 10 V),ADA4857-1 和 ADA4857-2 成为那些要求宽动态规模、超卓精度、高速和低功耗的体系的抱负挑选。

单 ADA4817-1 和双 ADA4817-2 FastFET ™ 扩大器是单位增益安稳、超高速度、电压反应型运算扩大器,具有 FET 输入。它们根据 ADI 专有的超快速互补双极型工艺 (XFCB) 开发,具有超低的噪声(4 nV/√Hz 和 2.5 fA/√Hz)和十分高的输入阻抗。凭仗 1.3 pF 的输入电容、2 mV 的最大偏置电压、低功耗 (19 mA) 和广泛的 −3 dB 带宽 (1050 MHz),它们成为数据收集前端、光电二极管前置扩大器和其他宽带跨阻抗运用场合的抱负之选。它们具有 5 V 至 10 V 的电源电压规模和单或双电源作业才能,合适在有源滤波、ADC 驱动、DAC 缓冲等很多运用场合中作业。

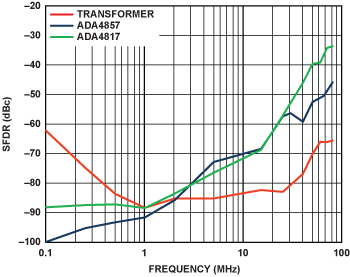

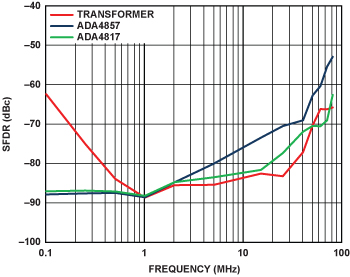

图 5 比较了这一电路与运用变压器的电路的失真和频率( VO = 500 mV p-p)。变压器的失真小于扩大器,后者在高频下具有更低的增益,但其失真在低频下变得越来越差。从图中看出,可在有限的规模内完结近 90 dB 的 SFDR,而且在 10 MHz 之前优于 70 dB。

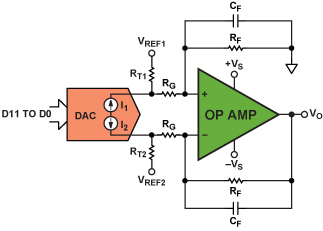

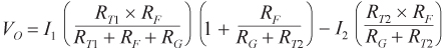

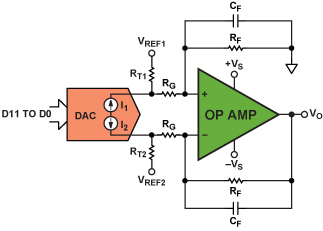

具有增益才能的运算扩大器:第三个电路(图 6)也运用了相同的高速运算扩大器,但它包括一个将扩大器与 DAC 阻隔的电阻网络,这答应设置增益,并能够灵敏运用两个基准电压(VREF1 和 VREF2)之一来调理输出偏置电压。

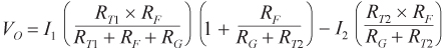

方程式 4 界说了在 VREF1 = VREF1 = 0 时 DAC 输出电流和扩大器输出电压之间的联系。为了匹配用于监督 DAC 的扩大器网络的输入阻抗,两个终端电阻 RT1 和 RT2 有必要独自设置,一起考虑扩大器的特性。

|

(4) |

图 7 比较了此装备中扩大器的失真以及变压器电路的失真。RT1 = 143 Ω,RT2 = 200 Ω,RF = RG = 499 Ω,CF = 5 pF—(完结安稳性和高频滤波),—以及 RL = 1 kΩ。从图中看出,在高频时,ADA4817 的功用与变压器适当,而且在 70 MHz 之前一直优于 −70 dBc SFDR。在低频时,与变压器比较,两个运算扩大器坚持了杰出的保真度。

本文经过比较电路在运用扩大器和变压器时的功用,展现了在将低失真、低噪声、高速扩大器用作 DAC 缓冲器时的一些长处。它还比较了三个运用两种不同扩大器架构的运用电路,而且供给了在运用 DAC 和 AD8129、ADA4857-1/ADA4857-2 以及 ADA4817-1/ADA4817-2 扩大器时的丈量数据示例。数据标明,在频率小于 1 MHz 时,扩大器的功用优于变压器,而且在 80 MHz 之前,扩大器的功用挨近变压器的功用。在功耗和失真之间做出取舍时,扩大器的挑选是十分重要的。