作者 / 陈智昕 电子科技大学(四川 成都 610054)

陈智昕,男(汉族),四川成都人,硕士研讨生,首要从事模仿集成电路的研讨规划。

摘要:提出了一种根据0.35μm BCD工艺的电平位移电路。该电路运用了耐压5V的CMOS器材。经过对惯例电平位移电路进行剖析,提出了优化改进的电平位移电路。电路仿真成果显现,与惯例的电平位移电路比较,改进的电路具有功耗低、输出电平安稳牢靠等特色。

0 导言

跟着最小特征尺度的不断下降,功耗问题现已成为现代集成电路规划的首要考虑要素之一。Dynamic Voltage Scaling Operating(动态电压调整)技能能为集成电路供应多种电源电压。一方面,用低电源电压给非要害途径模块供电,另一方面,在模仿和高速数字模块中运用较高的电源电压。这样的技能关于削减动态以及静态功耗是很必要的[1]。

在集成电路中,不同模组作业在不同的速度下,所以需求一种两层供电结构。在两层电压供应体系中,需求用电平位移电路(Level-shifter Circuit)将低电压转化为高电压以满意后续的模组作业。为了确保全体电路的作业功用,电平位移电路需求具有低功耗的特色[2]。

本文正是根据这样的使用需求,规划了一种低功耗的电平位移电路。文章剩下部分依照以下结构打开。第一部分对传统电平位移电路进行回忆,第二部分为本文所提出的电平位移电路原理,第三部分呈现了所规划电平位移电路的仿真成果。

1 惯例电平位移电路

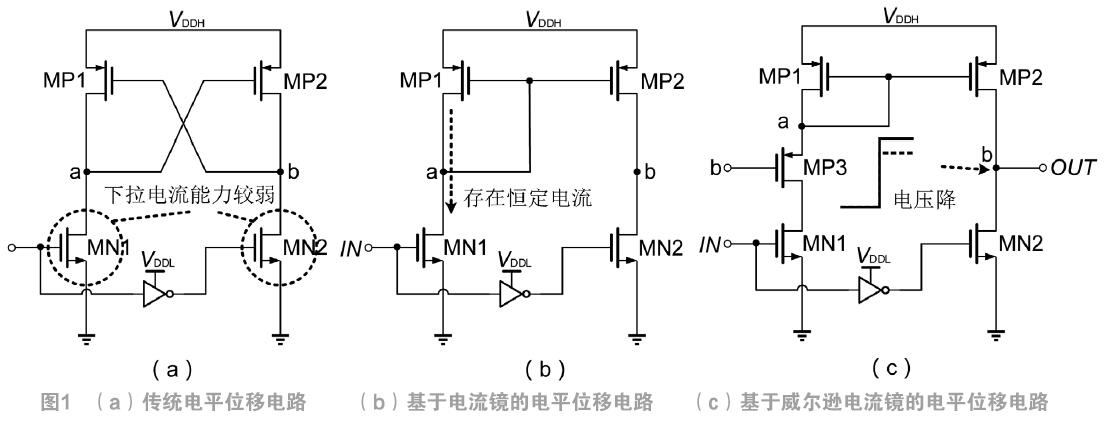

图1(a)为一种传统的电平位移电路,当输入信号IN为“1”(VIN=VDDL)时,MN1敞开,MN2关断,MN1管将结点a电位下拉,然后MP2导通,对结点b充电,跟着结点b电位的上升,MP1关断。相似的,当输入信号变至“0”(VIN=VSS)时,MN1关断而MN2导通,整个进程将反置。值得注意的是,当输入信号由“1”变“0”时,a点的初始电位不能瞬变而依然为“0”,因而MP2一开始依然导通,对结点b进行充电,削弱了MN2对结点b放电的效果,使得电位转化变得缓慢(对结点a的剖析同理)。咱们可以看到在结点a、b存在着上拉管(MP1和MP2)和下拉管(MN1和MN2)的电位抢夺,上拉P管对N管的下拉发生阻止效果。所以,当输入电压与VDDL/VDDH误差很大,特别是低于阈值电压时,下拉管的下拉才能远小于上拉管的上拉才能,电路无法正常转化电平[3]。

为了处理这样的问题,提出了根据电流镜的电平位移电路。如图1(b)所示,该结构使用电流镜约束了电流,然后鄙人拉管对输出结点放电时削弱了上拉管的上拉才能。可是,该结构存在一个显着的缺陷,当输入信号IN处于“1”时,存在较大的流经MP1和MN1的安稳电流,发生了额定功耗。为削减这样的静态功耗,提出了如图1(c)所示根据威尔逊电流镜的电路。电路中引进MP3以消除安稳电流,当输入信号IN为“1”时,输出电位上拉至“1”,使得MP3处于关断状况,然后切断了之前存在的安稳电流。可是,这种结构会形成结点b发生电压降,当结点b电位还未彻底上拉至VDDH时,MP3现已关断,形成结点a电位上浮而关断MP2管,使得结点b的电平起浮且低于VDDH[4-5]。

2 改进的电平位移电路

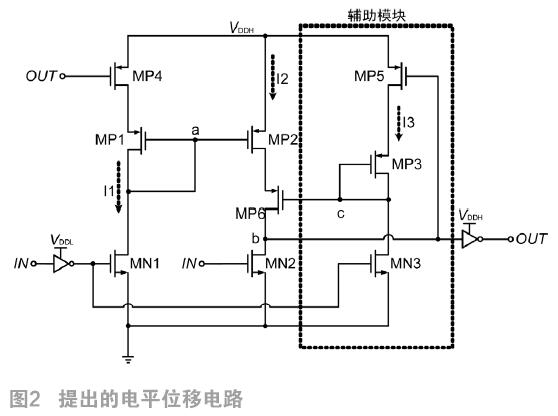

经过对惯例电平位移电路的剖析研讨,咱们可以看出上述电路存在着N管下拉电流才能较弱、继续安稳的大电流以及输出信号无法被彻底上拉至VDDH等问题。而这些问题的发生会使得电路在作业进程中发生更多的功耗。因而,本节在图1(c)所示电路结构基础上,提出了一种改进的电平位移电路,可以优化功耗问题。电路原理图如图2所示。

将图1(c)中MP3管上移至电流镜的上方(即图2中MP4管),使输出端在上电进程中,结点a的电位一直被下拉到地。而不会像图1(c)中那样,结点a的电位因MP3管的断开而上浮,使MP2管的上拉才能削弱而影响输出端电位无法上升到VDDH。与此同时,当输入IN为“1”时,MP4管按捺了流过MP4、MP1和MN1管的电流I1,使得功耗减小。

当输入信号由高变低时,由于结点b电位无法瞬变而仍为“0”。此刻,MP4、MN1管和MP5、MN3管敞开,MN2管关断。然后发生流经MP4、MP1和MN1管的电流I1以及流经MP5、MP3和MN3的电流I3。两股电流被镜像,发生电流I2,并上拉结点b的电位。最终,结点b电位变为“1”,并反应至MP4和MP5管使它们关断,然后切断电流I1、I3,也不再镜像电流I2。输出端变为“0”。由于MN1和MN3管一直敞开,致使结点a、c坚持地电位,MP2、MP6管处于常开状况,然后确保结点b电位可以一直处于VDDH而不起浮,然后对惯例电平位移电路结点呈现电压降的问题进行了优化改进。

当输入信号由低变高时,结点b信号起先依然为“1”。在不增加辅佐模块时,起先结点a电位依然为“0”,MP4管关断,使得MP2管处于强上拉状况,这样很大程度的削弱了MN2管对结点b电位的下拉效果(由于P管的上拉才能大于N管的下拉才能),导致输出端电位下降较慢。增加辅佐模块后,由MP2和MP6两个P管作开关,有用的按捺了结点b电位受P管上拉效果的影响,使得结点b电位可以较安稳地被下拉至“0”。

3 仿真成果及剖析

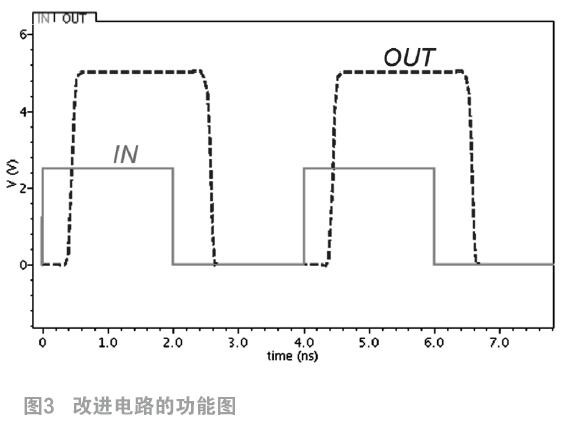

本文所提电平位移电路的仿真成果是根据华虹NEC 0.35μm BCD工艺进行,完成从2.5 V转化为5 V作业电压的功用。本节分别从全体功用、电流功耗以及具体问题优化状况三方面进行剖析。

如图3所示为改进电平位移电路功用波形图。仿真成果表明,所提出的电平位移电路输入2.5 V,经过大约200 ps安稳地转化为5 V输出电压环境,正确完成电路功用。

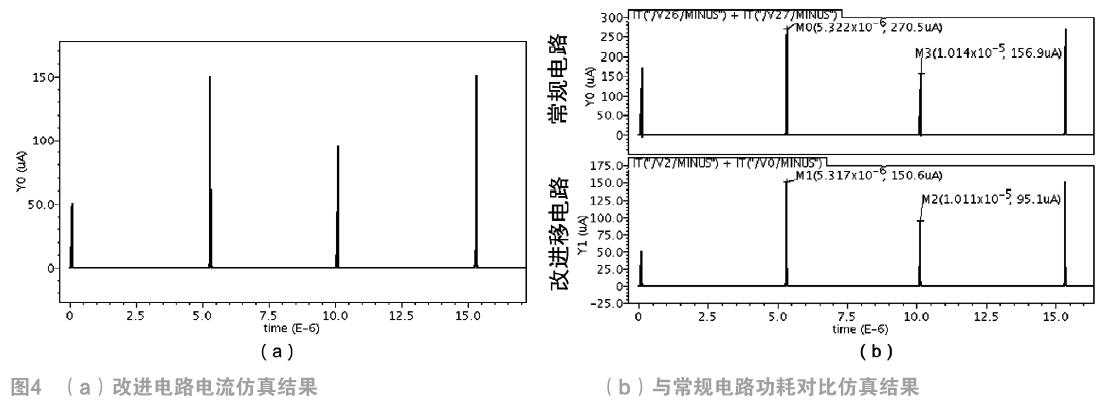

图4为电路功耗仿真成果,经过对IVDDL+IVDDH值进行比照直接反映惯例电平位移电路与改进电平位移电路的功耗巨细。从仿真成果来看,改进电路功耗显着减小,与惯例电路比较,功耗下降约45%,改进成果显着。

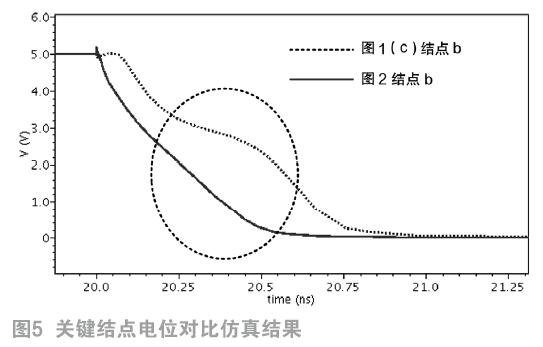

图5所示,为图1(c)惯例电路和图2改进电路结点b在N管对该结点电位进行下拉时的电位改变仿真图。由图可知,惯例电路结点b在电位被N管下拉时受到上拉管MP2未关断的影响,下拉有显着变缓的进程,波形下降沿呈现“二段式”的曲线。而改进电路b结点的下拉进程则愈加安稳,反映出改进电路中辅佐模块有用地按捺了P管上拉才能强对结点b电位的影响,削弱了P管上拉才能,使得b点电位能被下拉N管安稳地放电至“0”。

4 定论

本文提出一种改进的电平位移电路,经过调整反应PMOS管的方位和增加辅佐模块以改进电路功耗等问题。与惯例电平位移电路比较,所提出的电路具有低功耗,输出电平安稳牢靠等长处。

参考文献:

[1] K. Usami et al., “Automated low-power technique exploiting multiple supply voltages applied to a media processor,” IEEE J. Solid-State Circuits, vol. 33, no. 3, pp. 463–472, Mar. 1998.

[2] A. Shapiro and E. G. Friedman, “Power efficient level shifter for 16 nm FinFET near threshold circuits,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 2, pp. 774–778, Feb. 2016.

[3] B.Razavi.Design of Analog CMOS Integrated Circuits.McCraw-Hill Companies Inc.Boston,MA,2001.

[4] S. Lütkemeier and U. Ruckert, “A subthreshold to above-threshold level shifter comprising a Wilson current mirror,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 9, pp. 721–724, Sep. 2010.

[5] P. Corsonello, S. Perri, and F. Frustaci, “Exploring well configurations for voltage level converter design in 28 nm UTBB FDSOI technology,” in Proc. IEEE Int. Conf. Comput. Design (ICCD), Oct. 2015, pp. 499–504.

本文来源于《电子产品世界》2018年第10期第43页,欢迎您写论文时引证,并注明出处。