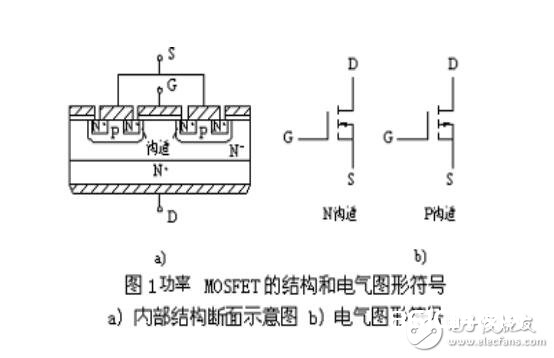

功率MOSFET的作业原理

截止:漏源极间加正电源,栅源极间电压为零。P基区与N漂移区之间构成的PN结J1反偏,漏源极之间无电流流过。

导电:在栅源极间加正电压UGS,栅极是绝缘的,所以不会有栅极电流流过。但栅极的正电压会将其下面P区中的空穴推开,而将P区中的少子—电子吸引到栅极下面的P区外表

当UGS大于UT(敞开电压或阈值电压)时,栅极下P区外表的电子浓度将超越空穴浓度,使P型半导体反型成N型而成为反型层,该反型层构成N沟道而使PN结J1消失,漏极和源极导电。

几种MOSFET驱动电路介绍及剖析

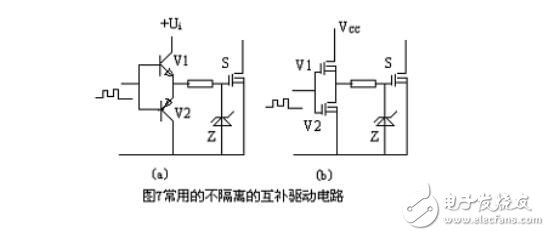

一. 不阻隔的互补驱动电路

图7(a)为常用的小功率驱动电路,简略牢靠成本低。适用于不要求阻隔的小功率开关设备。图7(b)所示驱动电路开关速度很快,驱动才能强,为避免两个MOSFET管直通,一般串接一个0.5~1Ω小电阻用于限流,该电路适用于不要求阻隔的中功率开关设备。这两种电路特色是结构简略。

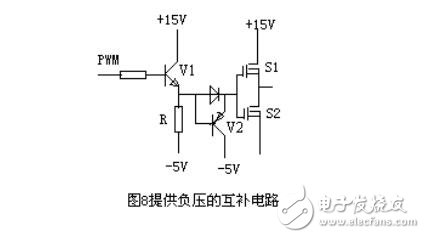

功率MOSFET归于电压型操控器材,只需栅极和源极之间施加的电压超越其阀值电压就会导通。因为MOSFET存在结电容,关断时其漏源两头电压的忽然上升将会经过结电容在栅源两头发生搅扰电压。常用的互补驱动电路的关断回路阻抗小,关断速度较快,但它不能供给负压,故抗搅扰性较差。为了进步电路的抗搅扰性,可在此种驱动电路的基础上添加一级有V1、V2、R组成的电路,发生一个负压,电路原理图如图8所示。

当V1导通时,V2关断,两个MOSFET中的上管的栅、源极放电,下管的栅、源极充电,即上管关断,下管导通,则被驱动的功率管关断;反之V1关断时,V2导通,上管导通,下管关断,使驱动的管子导通。因为上下两个管子的栅、源极经过不同的回路充放电,包括有V2的回路,因为V2会不断退出饱满直至关断,所以关于S1而言导通比关断要慢,关于S2而言导通比关断要快,所以两管发热程度也不完全相同,S1比S2发热严峻。

该驱动电路的缺陷是需求双电源,且因为R的取值不能过大,不然会使V1深度饱满,影响关断速度,所以R上会有必定的损耗。

二. 阻隔的驱动电路

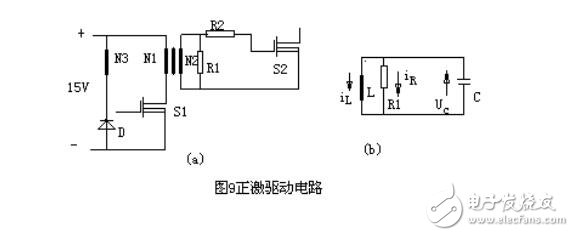

(1)正激式驱动电路。电路原理如图9(a)所示,N3为去磁绕组,S2为所驱动的功率管。R2为避免功率管栅极、源极点电压振动的一个阻尼电阻。因不要求漏感较小,且从速度方面考虑,一般R2较小,故在剖析中忽略不计。

其等效电路图如图9(b)所示脉冲不要求的副边并联一电阻R1,它做为正激变换器的假负载,用于消除关断期间输出电压发生振动而误导通。一起它还能够作为功率MOSFET关断时的能量泄放回路。该驱动电路的导通速度主要与被驱动的S2栅极、源极等效输入电容的巨细、S1的驱动信号的速度以及S1所能供给的电流巨细有关。由仿真及剖析可知,占空比D越小、R1越大、L越大,磁化电流越小,U1值越小,关断速度越慢。该电路具有以下长处:①电路结构简略牢靠,完成了阻隔驱动。 ②只需单电源即可供给导通时的正、关断时负压。 ③占空比固守时,经过合理的参数规划,此驱动电路也具有较快的开关速度。

该电路存在的缺陷:一是因为阻隔变压器副边需求噎嗝假负载防振动,故电路损耗较大;二是当占空比改变时关断速度改变较大。脉宽较窄时,因为是贮存的能量削减导致MOSFET栅极的关断速度变慢。

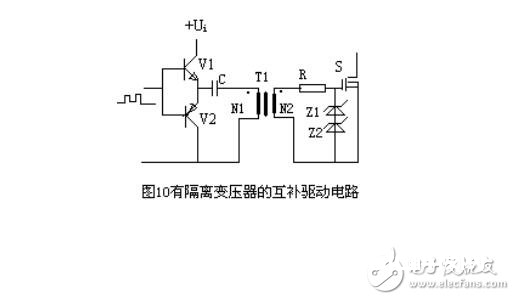

(2)有阻隔变压器的互补驱动电路。如图10所示,V1、V2为互补作业,电容C起阻隔直流的效果,T1为高频、高磁率的磁环或磁罐。

导通时阻隔变压器上的电压为(1-D)Ui、关断时为D Ui,若主功率管S牢靠导通电压为12V,而阻隔变压器原副边匝比N1/N2为12/[(1-D)Ui]。为确保导通期间GS电压安稳C值可稍取大些。该电路具有以下长处:

①电路结构简略牢靠,具有电气阻隔效果。当脉宽改变时,驱动的关断才能不会跟着改变。

②该电路只需一个电源,即为单电源作业。隔直电容C的效果能够在关断所驱动的管子时供给一个负压,然后加快了功率管的关断,且有较高的抗搅扰才能。

但该电路存在的一个较大缺陷是输出电压的幅值会跟着占空比的改变而改变。当D较小时,负向电压小,该电路的抗搅扰性变差,且正向电压较高,应该留意使其幅值不超越MOSFET栅极的答应电压。当D大于0.5时驱动电压正向电压小于其负向电压,此刻应该留意使其负电压值不超越MOAFET栅极答应电压。所以该电路比较适用于占空比固定或占空比改变规模不大以及占空比小于0.5的场合。

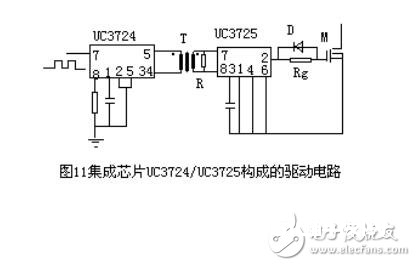

(3)集成芯片UC3724/3725构成的驱动电路

电路构成如图11所示。其间UC3724用来发生高频载波信号,载波频率由电容CT和电阻RT决议。一般载波频率小于600kHz,4脚和6脚两头发生高频调制波,经高频小磁环变压器阻隔后送到UC3725芯片7、8两脚经UC3725进行调制后得到驱动信号,UC3725内部有一肖特基整流桥一起将7、8脚的高频调制波整流成一向流电压供驱动所需功率。一般来说载波频率越高驱动延时越小,但太高抗搅扰变差;阻隔变压器磁化电感越大磁化电流越小,UC3724发热越少,但太大使匝数增多导致寄生参数影响变大,相同会使抗搅扰才能下降。依据试验数据得出:关于开关频率小于100kHz的信号一般取(400~500)kHz载波频率较好,变压器选用较高磁导如5K、7K等高频环形磁芯,其原边磁化电感小于约1毫亨左右为好。这种驱动电路仅适合于信号频率小于100kHz的场合,因信号频率相对载波频率太高的话,相对延时太多,且所需驱动功率增大,UC3724和UC3725芯片发热温升较高,故100kHz以上开关频率仅对较小极%&&&&&%的MOSFET才能够。关于1kVA左右开关频率小于100kHz的场合,它是一种杰出的驱动电路。该电路具有以下特色:单电源作业,操控信号与驱动完成阻隔,结构简略尺度较小,特别适用于占空比改变不确定或信号频率也改变的场合。