摘要:2000年以来,跟着嵌入式技能不断发展,许多依据嵌入式体系的数字化产品现已继PC机之后信息处理的又一大首要东西。它们都需求具有图形处理的功用,而且显现的内容也正阅历从简略2D图形到3D图形的改动。本规划选用OpenGL作为体系的图形API,选取了21条根本的API指令,界说了它们的烘托列表格局和指令字编码,并以此作为IP核的规划规约。

1 项目布景

1.1 研讨布景

LCD显现屏的运用越来越广,数量越来越多。LCD显现屏运用广泛,无处不在。如家庭各种电器设备。更常见是用于各种公共场合如体育馆、广场等商业用途。给咱们传递一种更为直观、生动的信息。从此咱们的日子发生了巨大改动。巨大的运用巨大的商场带来了巨大的商机。而与此一起,立体印象工业酿剧变,3D热潮势不可挡——电视机/显现设备。

依据FPGA的LCD显现的3D印象是为了LCD显现屏的信息量更多,满意人需求。

1.2 依据FPGA的立体显现的优越性

本项目通过在FPGA上用Verilog言语完结3D印象在LCD的成像,具有以下优势:

- 选用可编程的FPGA进行规划,便于规划的更新与晋级,节省本钱。

- 缓解CPU在图形处理方面的担负。

- 满意广阔顾客对3D印象的需求

- LCD体积小、质量轻、功耗低,能够用大规模集成电路直接驱动,能够在亮堂环境下显现,不含射线损伤。

2 项目计划

2.1 完结功用

- 将IP核区分为四部分,这儿咱们别离称之为FPGA1模块、FPGA2模块FPGA3和模块FPGA4模块,模仿CPU发送数据的cpu_module需求咱们用Verilog HDL规划。Cpu_module和IP核的几许改换模块归于FPGA1模块,IP核的光照模块归于FPGS2模块,FPGA3模块则包括了IP核图形管线的图元安装模块,除掉剪切模块、反面除掉模块和投影模块,IP核图形管线最终两个模块光栅化和片段处理归于PFGA4模块。

2.2硬件规划

通过上面临整个体系功用要求, 功用要求的剖析, 咱们能够确认体系的根本硬件结构, 其组成框图如下所示::

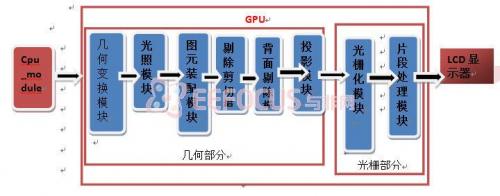

IP核图形管线的组成

图中的cpu module模块用来模仿图形运用程序经CPU处理得到烘托列表的进程,它将烘托列表指令以GPU方言的方式送到GPU,并等候图形管线中8级流水线的处理。整个图形管线分为两部分,几许部分和光栅部分,图中的前6个模块几许改换、光照、图元安装、裁剪、反面除掉、投影归于几许部分,后2个模块光栅化和片段处理归于光栅部分。

下面就图形管线每个模块的功用做一个扼要的陈说。

首先是对cpu module送来的数据进行几许改换,一个三角形图元由三个极点构成,每个极点包括的信息有方位信息、法线信息、色彩信息等。因为三维空间中的物体都是以极点的方式描绘,所以几许改换模块首要是对舀Begin和glEnd之间的极点数据流和相关指令的处理,所做的作业包括对极点坐标的平移、旋转、缩放。

然后是对极点色彩的核算,每个极点都能够有自己的色彩。影响物体色彩的要素有几个方面,一是环境光照的影响,二是物体原料自身对光源进行调制,三是光源的方位,因而该级模块有许多需求依据烘托列表中的指令设置相应的参数,然后依照光照原理和各个模型参数核算出极点的色彩。极点的坐标方位和色彩信息有了今后就需求将独自的极点数据组装成一个个图元,OpenGL支撑的图元有点、线、三角形、折线、线环、三角形带和三角形扇等。咱们的IP核现在只考虑了对三角形图元的处理,因为三角形是最根本的图元,其它图元只要在图元安装一级做一些处理就能够转化为对三角形图元的处理,点和线段的处理比三角形的处理简略,仅仅在光栅化一级稍有不同,而一些杂乱图元则能够分解成三角形图元来处理。

图元安装完结今后就应该对不在视景体内的图元进行除掉,对部分在视景体内的图元进行剪切。因为视界的约束,人不可能一起看到一切的物体,举例来说,你不可能看到自己反面是什么物体,因而在图形学顶用视景体来模仿视界的约束,将一些不显现的图元除掉剪切掉,以防止后级不必要的核算,减轻后级的担负。

反面除掉模块的作业是判别图元的正反面,依据需求显现咱们期望看到的那一面。因为虽然在视景体外面的图元被剪切掉了,可是并不意味着一切剩余的图元都会被显现出来,比方一枚硬币,当印有人头的一面临着咱们的时分,另一面的字就不能呈现在咱们面前,后级的处理也就不需求考虑有字的那一面。

前面五级的处理目标都是三维空间中的极点数据,但咱们的显现设备仅仅二维的,这就需求咱们将视景体中的三维图元映射到二维平面上,投影交流模块的效果就在于此。至此三维图元就变成了二维的图元,后边两级就只需求对二维图元进行处理。

光栅化一级需求将二维图元的坐标改换成整数,因为显现设备的光栅是离散的点阵,该级还需求做的作业是填充图元的内部,别的图元边际的反走样也需求在该级完结。通过该级的处理,二元图元就变成了离散的片元数据,即人们常说的像素数据,每个像素数据都和显现设备光栅上的某个点一一对应。

最终一级是片段处理,它的作业就是在像素数据送到帧缓冲区之前再对像素数据进行挑选,因为只要契合条件的才会被写入到帧缓冲区中。比方有一扇门,当门关起来的时分咱们就看不见门里的物体,这时只需将描绘门的像素数据送到帧缓冲区中,门后边的物体是被门挡住了的,不应该将描绘门后物体的像素数据送到帧缓冲区。而当门开着的时分,咱们需求将描绘门后物体的像素数据送到帧缓冲区中。一起假如需求Alpha混合,则还需求将两个物体的堆叠部分的像素的色彩值做混合处理。

这8个模块是3D图形处理器IP核的中心地点,咱们的作业就是在课题组已有作业的基础上,在4块FPGAJ2用Verilog HDL来规划完善这8个模块。

2.3 IP核的验证渠道

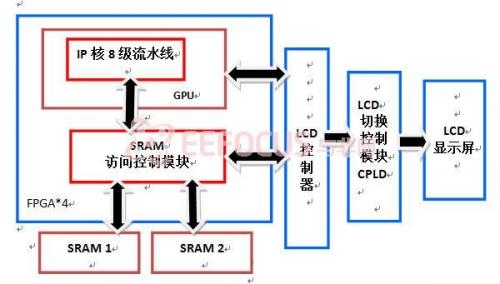

验证渠道的结构示意图如图所示。

验证渠道的结构示意图

验证渠道所运用的4片FPGA芯片是EP2C20Q240C8,它有18752个逻辑单元和239616BitSMemory,芯片之间选用级联的方式,按先后顺序咱们别离用FPGAl、FPGA2、FPGA3、FPGA4来表明。

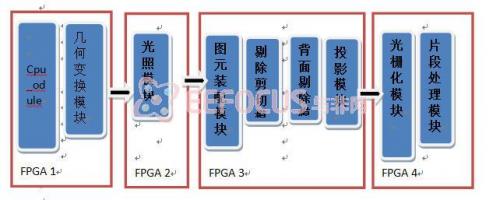

IP核的8个模块需求依照图形管线的结构别离映射到4片FPGA中,依据图形管线各模块所做的作业,每个模块在FPGA中的分配如图3.3所示。

IP核各模块在FPGA中的分配

依照图中的区分,咱们能够看作是将IP核区分成了4部分,这儿咱们别离称之为FPGAl模块、FPGA2模块、FPGA3模块和FPGA4模块。因为条件约束,用来模仿CPU发送数据的epu.module也需求咱们用Verilog HDL规划,epu 和IP核的几许改换模块归于模块,口核的光_module FPGAl照模块归于FPGA2模块,FPGA3模块则包括了IP核图形管线的图元安装模块、除掉剪切模块、反面除掉模块和投影模块,IP核图形管线最终两个模块光栅化和片段处理归于FPGA4模块。