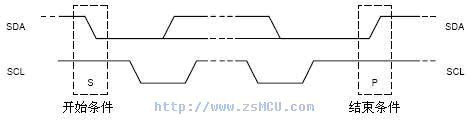

1.1 I2C位传输

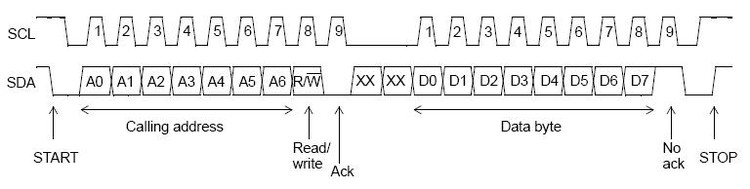

1.3 I2C应对信号

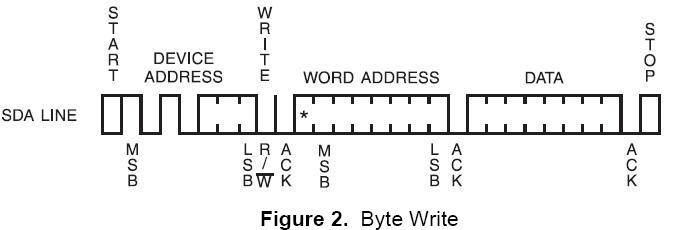

写寄存器的规范流程为:

1.

2.

3.

4.

5.

6.

7.

8.

9.

写一个寄存器

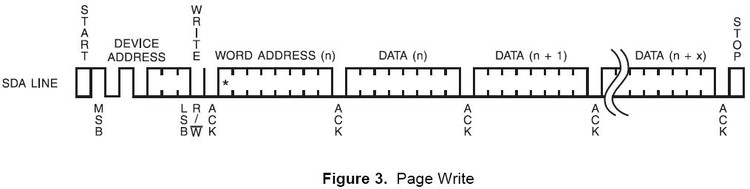

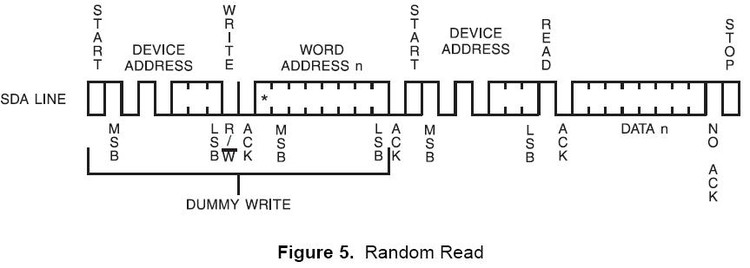

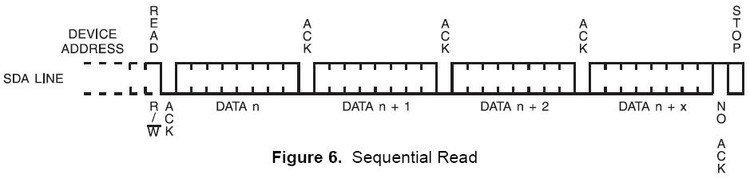

读寄存器的规范流程为:

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

读一个寄存器

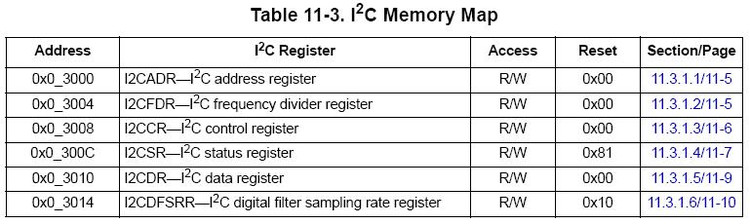

Mpc8560的CCSR中操控I2C的寄存器共有6个。

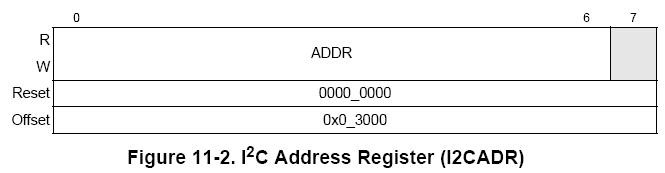

2.1 I2CADR 地址寄存器

CPU也能够是I2C的Slave,CPU的I2C地址有 I2CADR指定

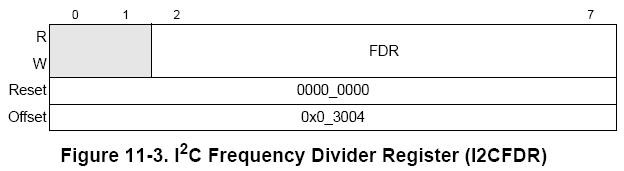

用来设置I2C总线频率

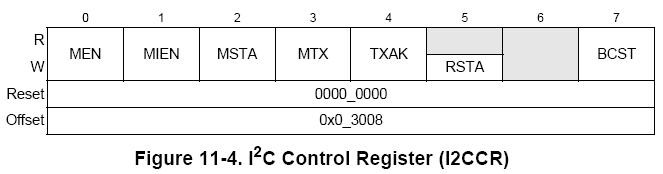

2.3 I2CCR 操控寄存器

MEN: Module Enable.

MIEN:Module Interrupt Enable. 置1时,I2C中止使能。

MSTA:Master/slave mode. 1 Master mode,0 Slave mode.

MTX:Transmit/receive mode select.0 Receive mode,1 Transmit mode

TXAK:Transfer acknowledge. 置1时,CPU在9th clock发送ACK拉低SDA

RSTA:Repeat START. 置1时,CPU发送REPEAT START

BCST:置1,CPU接纳播送信息(信息的slave addr为7个0)

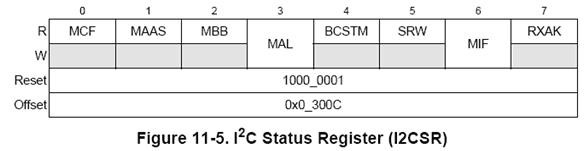

2.4 I2CSR 状况寄存器

MAAS:当CPU作为Slave时,若I2CDR与会话中Slaveaddr匹配,此bit被置1

MBB:0 I2C bus idle

MAL:若置1,表明裁定失利

BCSTM:若置1,表明接纳到播送信息

SRW:When MAAS is set, SRW indicates the value of the R/W command bit of the calling address, which is sent from the master.

MIF:Module interrupt. The MIF bit is set when an interrupt is pending, causing a processor interrupt request(provided I2CCR[MIEN] is set)

RXAK:若置1,表明收到了ACK

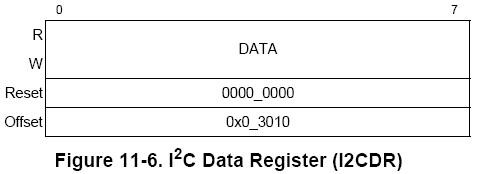

2.5 I2CDR 数据寄存器

这个寄存器贮存CPU即将传输的数据。

3. PPC-Linux中I2C的完成

- static int mpc_xfer(struct i2c_adapter *adap, struct i2c_msg *msgs, int num)

- {

struct i2c_msg *pmsg; int i; int ret = 0; unsigned long orig_jiffies = jiffies; struct mpc_i2c *i2c = i2c_get_adapdata(adap); mpc_i2c_start(i2c); // 设置I2CCR[MEN], 使能I2C module //一直读I2CSR[MBB],等候I2C总线闲暇下来 while (readb(i2c->base + MPC_I2C_SR) & CSR_MBB) { if (signal_pending(current)) { pr_debug(“I2C: Interruptedn”); writeccr(i2c, 0); return -EINTR; } if (time_after(jiffies, orig_jiffies + HZ)) { pr_debug(“I2C: timeoutn”); if (readb(i2c->base + MPC_I2C_SR) == (CSR_MCF | CSR_MBB | CSR_RXAK)) mpc_i2c_fixup(i2c); return -EIO; } schedule(); } for (i = 0; ret >= 0 && i < num; i++) { pmsg = &msgs[i]; pr_debug(“Doing %s %d bytes to 0xx – %d of %d messagesn”, pmsg->flags & I2C_M_RD ? “read” : “write”, pmsg->len, pmsg->addr, i + 1, num); //依据音讯里的flag进行读操作或写操作 if (pmsg->flags & I2C_M_RD) ret = mpc_read(i2c, pmsg->addr, pmsg->buf, pmsg->len, i); else ret = mpc_write(i2c, pmsg->addr, pmsg->buf, pmsg->len, i); } mpc_i2c_stop(i2c); //确保为I2CCSR[MSTA]为0,确保能触发STOP return (ret < 0) ? ret : num; - }