跟着软件无线电理论的日趋老练,软件无线电技能越来越多地使用到军用或民用通讯体系中。其间,数字下变频技能(DDC)是软件无线电中的核心技能之一。数字下变频作业在模仿前端输入模仿信号经模数转化之后,而在终端设备的数字信号处理之前,它首要用于完成将中频信号频谱变到零中频后,再对信号进行抽取,使采样速率变至后端数字信号处理单元所需求的处理速率。

现在跟着A/D改换越来越向射频前端开展,高速采样速率对后续的数字信号处理和整个体系的和谐作业带来了越来越大的压力。为了处理高速采样的大数据量与现有DSP器材处理才干之间很难匹配的问题,规划了一种根据多相滤波的宽带数字下变频结构,将多相滤波下变频的并行结构使用到数字下变频器中,并在后续的混频模块中也选用并行混频的办法来完成,提高了实时处理速度。从原理剖析和FPGA板卡验证两方面临该规划方案进行了验证,均证明本文经过多相滤波数字下变频处理后的数据速率能满意现有DSP器材处理才干的要求。

1 根据多相滤波的宽带正交数字下变频技能

1.1 带通采样定理

带通采样定理:设一个频率带限信号x(t),其频带约束在(fL,fH)这一规划,假如采样频率满意fS满意:

式中,n取能满意fS≥2(fH-fL)=2B的最大正整数,则用fS进行等距离采样所得到的信号采样值x(nTS)能精确地确认原信号x(t)。明显,当fL=0且fH=B时,挑选n=0,式(1)便是Nyquist低通采样定理,它是带通采样的一种特别情况。

在实践的数字接纳机中,信号的带宽B一般会远小于信号的最高频率,假如仍是依照Nyquist采样率来规划,ADC的采样频率会很高,以至于很难完成,或许后处理的速度也满意不了要求。所以很自然地考虑用不丢掉信息的带通采样定理完成。数字接纳机输入的中频信号都是带通讯号,接纳机数字化一般在中频上进行,所以各种电子配备都可运用带通采样定理对模仿信号进行采样将其数字化。

1.2 正交数字下变频

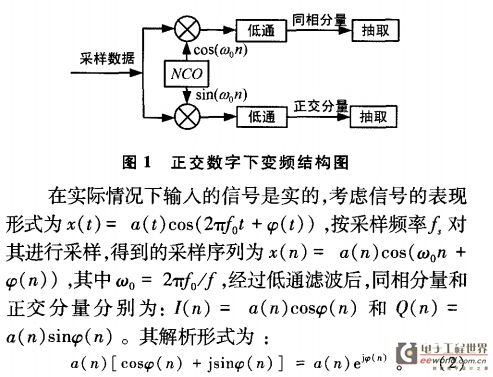

所谓数字混频正交改换实践上便是先对模仿信号x(t)经过采样器后构成数字序列x(n),然后与2个正交本振序列cos(ω0n)和sin(ω0n)相乘,再经过数字低通滤波来完成。完成框图如图1所示。

图1正交数字下变频结构图

经过正交数字下变频后,采样率就能够下降了,因而低通滤波器后往往进行抽取操作。

正交数字下变频能够完成IQ支路的平衡,为完成严厉正交,一般需求进行IQ均衡处理,正交下变频办法在频率调制和相位调制使用中得到广泛的使用。

1.3 抽取器的多相滤波

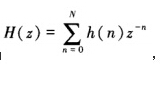

假定FIR数字滤波器的冲击响应为h(n),则其Z改换的界说为

将求和式打开并重写为:

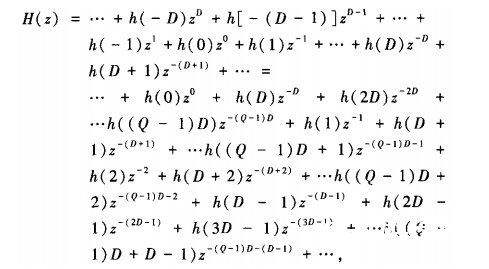

经过兼并后能够写为:

式(4)即为数字滤波器H(z)的多相滤波结构,并运用抽取器的等效联系,等效优化今后的多相滤波器结构如图2所示。

多相滤波的本质能够看作按相位均分的联系把数字滤波器的搬运函数H(z)分化成若干个不同相位的组,构成多个分支,在每个分支上完成滤波。这样做的意图便是用其分支上阶数较少的滤波来完成本来阶数很大的H(z)的滤波。这样做的含义在于工程上易于完成,能高效地进行实时信号的处理。2 FPGA完成规划

2.1 体系规划

天线接纳的信号经过射频前端处理后,将信号混频滤波降至中频1000MHz,带宽为200MHz。由于信号的带宽为200MHz,能够考虑带通采样,将公式1中的n取值为2,核算出采样率为800MHz。数字处理部分要求能将200MHz带宽内恣意100MHz带宽信号变为零中频,传送给DSP进行信号剖析。

采样器传输过来的数据是两路DDR办法,首要对接纳进FPGA的采样数据流进行解DDR操作,变成了4路200MHz数据流。

2.2 一次变频

高采样率的数据流在FPGA内运算适当耗费资源,所以关于宽带信号的FPGA处理来说,假如能下降运算量,那将对错常有含义的。

考虑到用800MHz采样率采一个中频为1000MHz的信号,适当于信号数字频率为200MHz。假如首要将这个信号的中频搬移到零频,那么数字低通滤波器的规划带宽便是信号带宽的一半,这样就能够将采样率下降一半再进行后续处理。

关于800MHz的采样率来发生一个200MHz的下变频的本振信号,一个周期刚好采4个数据点,能够选用一种特别相位联系的DDS序列,余弦序列值别离取1、0、-1和0,正弦序列值别离取0、1、0和-1,那么这个下变频就变得非常简单明了,关于取0的支路来说,后续就不需求核算了;关于取1的支路,适当于数据推迟一拍;关于取-1的支路,就适当于数据取反后加1的操作。这种特别相位联系的下变频处理几乎不耗费FPGA内部资源,并且不引进变频后发生的杂散。

2.3 多相滤波的FPGA完成

考虑到在完成规划较大电路的资源耗费和体系的安稳性要素,保险起见将一次变频后的4路200MHz数据分化为8路100MHz进行后续处理,实践上经过一次变频后的IQ数据里边有一半都是零,这些支路后续的滤波处理就不需求核算了,节约一半资源。

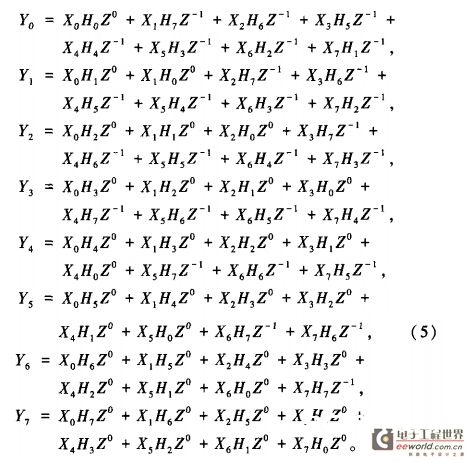

8路子数据流为X0、X1、X2、X3、X4、X5、X6和X7,对滤波器搬运函数日进行分化,经过八相分化后的子滤波器别离为H0、H1、H2、H3、H4、H5、H6和H7,经过分化能够得到输出信号与输入信号之间的联系表达式:

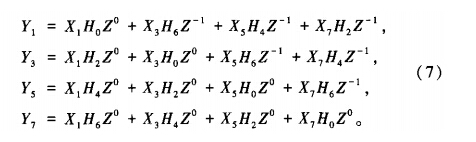

由于多相滤波后信号频谱宽度削减一半,能够对数据进行两倍抽取操作,所以数据挑选其间一半的多相子数据支路即可,又节约了一半资源。这儿挑选偶数支路的输出Y1、Y3、Y5、Y7并考虑到一次变频本振DDS余弦序列的偶数值为0,正弦序列的奇数值为0,经过化简后的同相支路的多相表达式为:

经过化简后的正交支路的多相表达式为:

2.4 二次变频

假如要处理的信号是200MHz带宽中心的100MHz带宽的话,则经过一次变频和多相滤波后的信号就能满意要求,假如后续处理信号的带宽包括两头的各50MHz的信号的话,就必须再加上第二级的数字变频操作才干满意体系的要求,经过多相滤波后的数据流是4路100MHz的正交数据。在这儿,二次变频DDS本振的输出表现办法也是4路并行的正交载波数据,只需求将4个支路的子数据流与4个支路的复载波进行复乘即可。在FPGA的完成过程中,别离例化4个相位的DDS本振核,然后写入相同的相位累加字和不同的初始相位值就完成了对多相复本振IP核的装备。

3 实验仿真与工程验证

本体系的FPGA程序开发使用了XILINX公司的ISE12.4硬件开发东西。FPGA挑选V6系列的V6SX315T芯片。体系选用VHDL言语编程的办法完成。

体系采样率为800MHz,输入AD采样器的模仿信号中频为1000MHz,带宽200MHz。原型低通滤波器规划选用Matlab辅助规划,挑选滤波器规划东西,滤波器归一化通带为0.25,阻带为0.42,阶数为48阶,带外按捺为60dB。以下用一个单音信号验证功用。信号频点为960MHz,经过一次变频后和频信号为1160MHz,差频信号为760MHz,其所对应的数字频率别离为360MHz和40MHz,其间挑选差频40MHz为所保存信号,如图3所示差频与和频有60dB的滤波器按捺,经过多相DDS将频谱再向上搬移20MHz,则所保存信号的频率为60MHz,两次变频后的成果如图3所示。

图3两次变频后的信号频谱

假如选用传统的多相滤波结构完成宽带数字下变频结构,8个滤波支路都要进行核算,那么乘法器将多耗费一倍为768个DSP48E。选用本文所介绍的办法耗费384个DSP48E,FPGA内部资源量能够很多节约。

4 结束语

介绍了一种根据FPGA规划的宽带数字正交下变频器的完成办法,经实践上板测验证明,FPGA电路运转状况安稳牢靠。介绍了带通采样定理和正交数字下变频原理,从理论上推导了抽取器的多相滤波的数学模型,结合FPGA的完成特色,运用两次变频和一次多相滤波的办法,完成了宽带频谱的搬移,选用并行处理的办法提高了处理的实时性,经过多相滤波的高效结构削减了运算量,节约了很多的FPGA资源,下降了板卡的功耗,具有较强的工程可完成性。