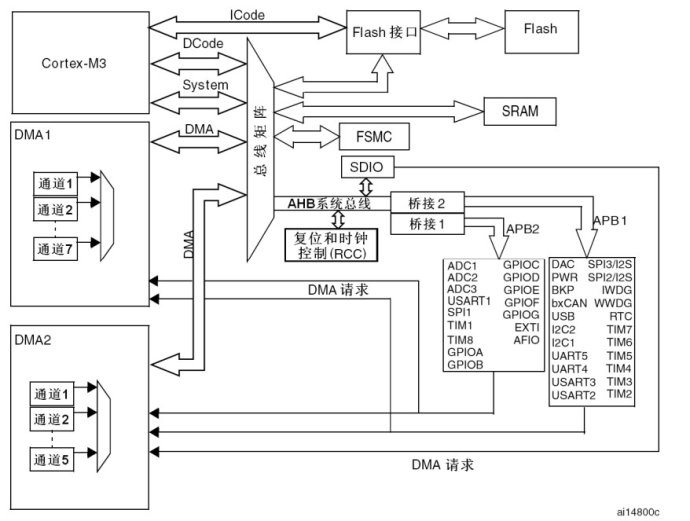

一、体系架构

四个驱动单元:

–Cortex™-M3 内核DCode总线(D-bus)和体系总线(S-bus);

–通用DMA1和通用DMA2;

四个被迫单元:

–内部SRAM;

–内部闪存存储器;

–FSMC;

–AHB到APB 的桥(AHB2APBx),它衔接一切的APB设备;

%&&&&&%ode总线

–该总线将Cortex™-M3 内核的指令总线与闪存指令接口相衔接。指令预取在此总线上完结。

DCode总线

–该总线将Cortex™-M3 内核的DCode总线与闪存存储器的数据接口相衔接(常量加载和调试拜访)。

体系总线

–此总线衔接Cortex™-M3 内核的体系总线(外设总线)到总线矩阵,总线矩阵和谐着内核和DMA间的拜访。

DMA总线

–此总线将DMA 的AHB 主控接口与总线矩阵相联,总线矩阵和谐着CPU的DCode和DMA到SRAM、闪存和外设的拜访。

总线矩阵

–总线矩阵和谐内核体系总线和DMA主控总线之间的拜访裁定,裁定使用轮换算法。在互联型产品中,总线矩阵包括5个驱动部件(CPU 的DCode 、体系总线、以太网DMA 、DMA1总线和DMA2总线)和3个从部件(闪存存储器接口(FLITF)、SRAM和AHB2APB桥)。在其它产品中总线矩阵包括4个驱动部件(CPU的DCode、体系总线、DMA1总线和DMA2总线)和4个被迫部件(闪存存储器接口(FLITF)、SRAM、FSMC和AHB2APB桥)。

AHB外设经过总线矩阵与体系总线相连,答应DMA拜访。

AHB/APB桥(APB)

–两个AHB/APB桥在AHB和2个APB 总线间供给同步衔接。APB1操作速度限于36MHz ,APB2操作于全速(最高72MHz)。