S3C2440有27根地址线ADDR[26:0],8根片选信号nGCS0-nGCS7,对应bank0-bank7,当拜访bankx的地址空间,nGCSx引脚为低电平,选中外设。

2^27=2^7 * 2^10 * 2^10 = 128Mbyte

8*128Mbyte = 1Gbyte

所以S3C2440总的寻址空间是1Gbyte。

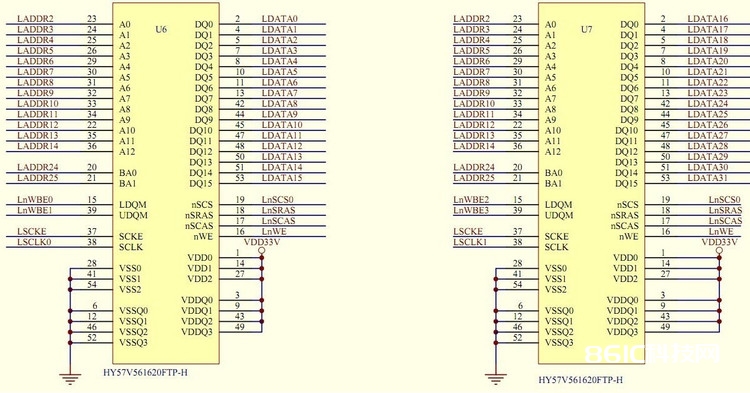

市面上很少有32位宽度的单片SDRAM,一般挑选2片16位SDRAM扩展得到32位SDRAM.

挑选的SDARM是HY57V561620F,4Mbit * 4bank *16,共16Mbyte?(后边有解说)

两块HY57V561620F并接,构成64M×32bit的SDRAM

首要了解下SDRAM的寻址原理。

SDRAM内部是一个存储阵列。能够把它幻想成一个表格。和表格的检索原理相同,先指定行,再指定列,就能够精确找到所需求的存储单元。这个表格称为逻辑BANK。现在的SDRAM根本都是4个BANK。寻址的流程便是先指定BANK地址,再指定行地址,最终指定列地址。这便是SDRAM的寻址原理。存储阵列示意图如下:

检查HY57V561620F的材料,这个SDRAM有

13根行地址线 RA0-RA12

9根列地址线 CA0-CA8

2根BANK挑选线 BA0-BA1(4个bank的挑选)

SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作进程是将读写的地址分两次输入到芯片中,每一次都由同一组地址线输入。两次送到芯片上去的地址别离称为行地址和列地址。它们被锁存到芯片内部的行地址锁存器和列地址锁存器。

/RAS是行地址锁存信号,该信号将行地址锁存在芯片内部的行地址锁存器中;

/CAS是列地址锁存信号,该信号将列地址锁存在芯片内部的列地址锁存器中。

NSCS接到bank6上,决议了SDRAM的物理地址是0x30000000

地址连线如下图:

LnSCS0脚接了nGCS6,即接在了bank6上,所以SDRAM的物理地址从0X30000000开端

为啥LADDR2接A0呢?

@CPU的寻址空间中,仍然是按8bit一个字节为单位操作的

@因为SDRAM并接成了32位,即4个字节,这样接使得SDRAM的最小单位是4个字节,便利32位的读写操作吧

为啥LADDR24/25接BA0/1?

@ BA1:BA0是SDRAM的最高位,组合挑选4个bank中的哪一个

@ LADDR0~LADDR25,一共26根地址线,可寻址(2的26次方)64MB

为啥一个bank4MB,而容量不是4mb×4bank=16MB是8×4=32MB?

@ 13根行地址线+9根列地址线 = 22根(4MB)。别的HY57V561620F一个存储单元是2个字节(本身是16位的),相当于有了23根地址线。

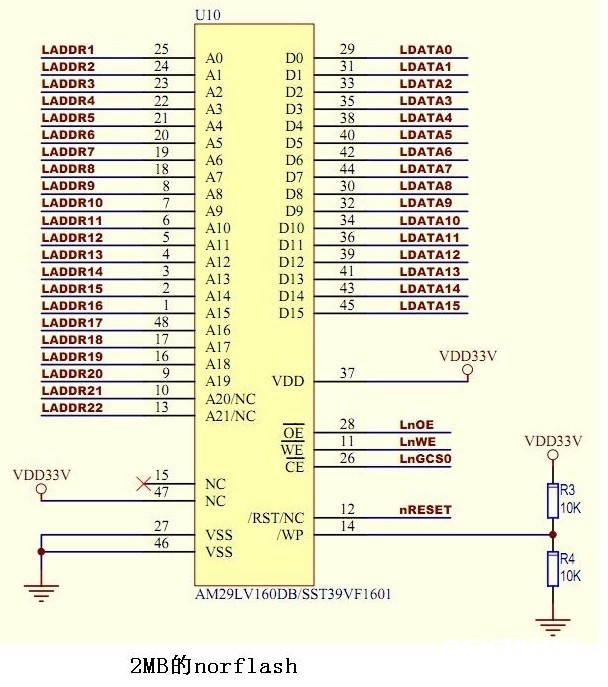

NORFLASH中A0接CPU的LADDR1,那么,norflash的最小寻址单元为2个字节(16位),事实上只要A0~A19是有用的,因为该nor本身才有2MB,2的20次方=1MB,加上nor本身是16位的(2个字节),所以1MB×2便是nor的巨细

@ 26脚接了nGCS0,即接在了bank0上,所以,nor的物理地址从0X00000000开端

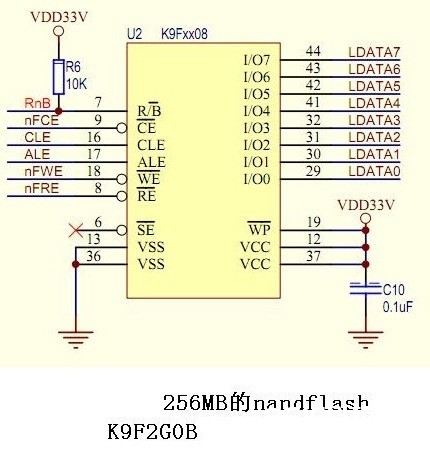

从接线上能够看出NAND有点特别,他并没有经过CPU的地址线拜访,这就答复了为啥能够接1GB的NAND,当然他也没有接bank挑选线,天然不存在物理地址了,由此我猜测NAND是由硬件本身辨认的,即OM开关挑选是NOR仍是NAND发动,这好像也验证了数据手册上这两种发动方法的映射图,NAND的发动方法可参阅前面的日志

0x4000_0000-0x4000_0fff

—–这4K字节的便是前面说的stepingstone的啦。0x4000_0fff_0x4800_0000是没用到的。

0x4800_0000-0x6000_0000

—–这空间是特别功用寄存器的.你发现,一切的寄存器都是在这个范围内的。

0x6000_0000—0Xffff_ffff

—–仍是未用到的。

理论上能够寻址的空间为(2的32次方,32根地址线)4GB,但其中有3GB的空间都预留给处理器内部的寄存器和其他设备了,留给外部可寻址的空间只要1GB,也便是0X00000000~0X3FFFFFFF,一共应该有30根地址线。这1GB的空间,2440处理器又依据所支撑的设备的特色将它分为了8份,每份空间有128MB,这每一份的空间又称为一个BANK。为便利操作,2440独登时给了每个BANK一个片选信号(nGCS7~nGCS0)。其实这8个片选信号能够看作是2440处理器内部30根地址线的最高三位所做的地址译码的成果。正因为这3根地址线所代表的地址信息已经由8个片选信号来传递了,因而2410处理器最终输出的实践地址线就只要A26~A0

nandflash因为其本身的特色,不具备运转程序的功用。但s3c2440经过称为“Steppingstone”的内部SRAM缓存,完结了能够运转存储在外部nandflash中的发动代码的功用。它的机制是:当检测到是由nandflash发动时,体系会主动把nandflash中的前4k字节的数据加载到Steppingstone中,然后把该Steppingstone映射为Bank0,因而体系会从Steppingstone开端运转程序,然后完结了s3c2440的nandflash自发动的功用。这一进程是由体系主动完结的,无需人为干涉。在体系发动今后,Steppingstone地点的SRAM就能够用作其他用处了。