摘要:规划完结了以FPGA为主操控单元,选用EZ-USB FX2微处理器为接口芯片的快速数据传输体系。文章给出了FPGA和CY7C68013之间数据传输的软硬件规划计划,侧重介绍了FPGA内部建构的FIFO原理及程序完结办法,并以FLASH存储模块为例,经过FX2与FLASH握手进程的规划,完结了数据存储器与计算机之间的数据高速传输。运用成果表明,此数据传输体系牢靠有用,具有必定的通用性,可用于其他运用USB进行数据传输的体系中。

0 导言

现代电子技术的前进使得外设的品种日益繁复,接入数量急剧添加,传统的装置数据收集卡的方法,因为存在装置不方便、扩展困难、传输质量不高级许多缺陷,逐渐满意不了数据收集进程中对杂乱外设和数据传输速率的要求。此外,在需求移动数据收集的场合,一般笔记本电脑以及绝大部分便携式数据收集设备都不再供给PCI插槽。因而选用共同、快捷的数据传输接口来代替原有方法,其紧迫性日益凸显。通用串行总线(USB)作为一个接口标准把不同类型的接口共同起来,且其外接设备具有热插拔、易扩展、传输速度快等长处,已经成为各类笔记本和便携设备数据传输的干流接口。

本规划运用支撑USB2.0协议的CY7C68013芯片,作为上位机与FPGA之间的传输接口,以FPGA为主操控单元,完结了数据的高速传输。文章给出了此数据传输体系的硬件规划计划,侧重介绍了FPGA操控模块中内部集成FIFO的结构原理和要害程序模块的完结方法。本体系规划计划结构简略、传输速度快、具有必定的可扩展性。

1 体系硬件规划

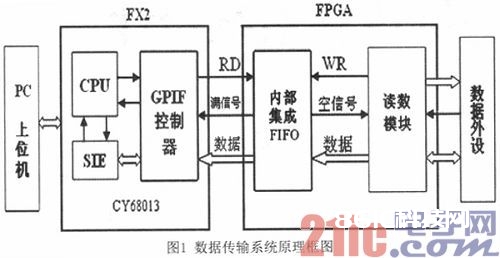

数据传输体系硬件原理框图如图1所示,主要由USB传输操控器EZ-USB FX2、FPGA主操控单元、外设模块构成。数据收集模块在中心操控单元的操控下对信号、数据等进行收集,并把数据终究转入数据外设中进行存储。上位机经传输操控模块(FX2)发送操控指令到主操控单元(FPGA)内部后,经过串并转化进行指令解码,解码后依照相应的指令要求从数据外设(FLASH)中进行数据读取。然后完结将外设存储体系中的数据快速上传到上位机中保存处理。

1.1 USB传输操控器

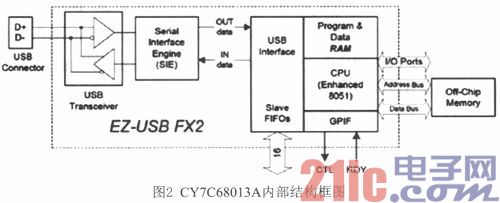

本体系USB传输接口芯片挑选Cypress公司的CY7C68013,它是Cypress公司推出的EZ-USB FX2系列产品之一,集成USB2.0的微处理器,具有增强型8051内核功能,智能串行引擎(SIE),通用可编程接口(GPIF),8.5KB的RAM和FIFO存储器,支撑12Mb/s的全速速率和1480 Mb/s的高速传输速率,最大极限地满意了USB 2.0的总线带宽。其内部结

构如图2所示。

CY7C68013因为其内部集成有独立于微处理器的USB核,其可被装备成GPIF(可编程接口)和SlaveFIFO(主从)等多种接口形式,使数据传输经过履行USB自身的协议来完结。在此进程中CPU可不参加数据传输,然后使数据的传输速率大大提高,一起也简化了固件代码的编写。本规划选用FX2的GPIF数据传输方法,时序简略、编程灵敏,能够很容易地从RAM中读取数据。

1.2 FPGA主操控单元

本规划选用Altera公司的EP1K30QC208作为主控芯片,完结对数据传输进程的操控。它包含1728个逻辑单元,本钱较低,适用于小体系编程。在此硬件体系中FPGA的效果主要有二个:一是完结对所传输数据的操控。上位机经USB传输操控模块(FX2)发送操控指令到FPGA主操控单元后,经过其内部串并转化,完结指令解码。解码后依照要求从数据外设(FLASH)中进行数据读取,并依据FIFO状况进行数据传输操控;二是内部建构一个FIFO存储器。因为本规划是对FLASH存储器进行读数操作,其数据传输是以页为单位,读数时页与页之间有一小段时刻距离,数据输出不是接连的。为完结FX2读取FLASH中的数据,需求在FPGA建构FIFO作为数据过渡,先将FLASH中的数据读到FIFO中,CY7C68013传输操控器再从FIFO中读取数据。

2 主控单元软件规划

依据本体系主操控单元的效果,FPGA要完结上文所述的主要功能,其要害在于FX2与FLASH的握手进程的规划,满意此进程的内部FIFO的建构和相关标志信号的发生。

2.1 FX2与FLASH的握手进程

FPGA主控单元先将数据存储到内部的FIFO中,然后CY7C68013再从FIFO中读取数据。因为读取和写入的速度是不同的,或许读比写快,也或许写比读快。为防止传输时数据丢掉,规划如下的握手进程:FPGA内部的“读数操控”模块不断进行判别,只需FIFO不满它就一向向FIFO中写入数据。关于外部FX2,只需判别FIFO不空它就从FIFO中读取数据。这样FIFO的读写就组成了一个闭环,确保了读数的完好精确。在数据传输握手方法确认今后或许呈现两种状况:1)FIFO的写入速度大于读取速度,这样写地址渐渐就追上读地址,此刻总的传输速度就取决于读取速度。2)FIFO的读取速度大于写入速度,这样读地址渐渐就追上写地址,此刻总的传输速度就由写入速度决议。在FPGA中编写“标志位

发生”程序模块,发生满、空信号作为FX2与FLASH传输进程中的握手信号,是确保数据传输安稳牢靠的要害。

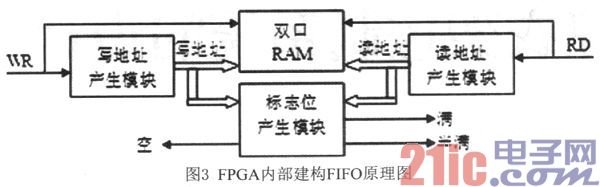

2.2 内部建构的FIFO原理及要害程序的流程

FIFO的实质是一种特别的双口RAM,大部分FPGA内部就有双口RAM资源。FIFO结构的特点是先进先出,对外它是一种没有地址操控的特别缓存。在程序编写进程中,内部FIFO要求只需接纳RD、WR使能信号,就能进行读写作业。在此进程中,整个FIFO模块对外不显现地址,只需求给出体现内部状况的满、半满和空信号即可。FX2和FPGA内部的“读数操控”模块依据这些信号对FIFO进行数据传输操控。FPGA内部建构的FIFO原理图如图3所示。

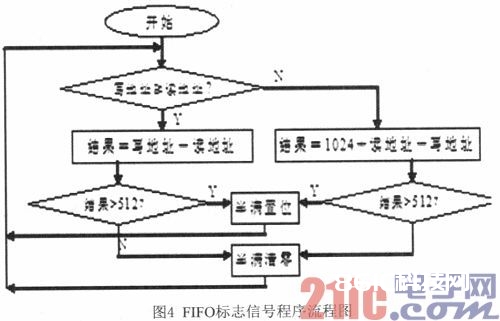

FIFO发生满、空状况标志信号由“标志位发生”程序模块发生,满、空状况信号均选用写地址和读地址相减(或读地址和写地址相减)的成果来判别双口RAM此刻的状况。此外,还能够据此得到FIFO的半满状况信号,以此可容易地标明FIFO满空深度。FIFO满、空、半满标志信号的程序流程根本共同,只不过判别比较的差值存在不同。FIFO满时地址差值为1023,空时为1,半满是差值大于512。以半满信号发生为例,标志位发生程序流程如图4所示。

为了防止时序过错,还能够恣意设定必定的满空深度。例如能够设定当地址差大于1000时即以为FIFO己满,不再向FIFO中写入数据,以防止过错的呈现。

3 结语

跟着便携式数据存储体系的遍及,依据USB的数据传输体系受到了遍及重视。本文规划的依据EZ-USB FX2微处理器的数据传输体系,完结了上位机经过USB端口对FLASH存储器的快速读取操作,并成功地运用在某一车载数据盒工程项目中。测验成果表明,体系传输进程安稳,速度较高,与上位机接口方法严格遵守USB 2.0协议,具有很强的通用性,适宜即插即用的作业场合。本体系依据FPGA的主控单元装备计划便于软件体系的晋级与调试,假如调配适宜的传感器和相应的信号调度电路,就能够完结对多种信号的收集处理,再配以适宜的存储模块完全能够构成齐备的数据收集存储体系。本规划关于一般的数据传输体系的规划及传统接口改造具有必定的学习含义。