根据进步CAN总线组网才能的考虑,提出一种新颖的CAN中继器规划办法;论述以LPC2119控制器为中心的硬件规划方案;详细分析在μC/OSII实时操作体系下的软件完结进程;针对中继器的实时性和安全性以及总线与总线之间或许存在的速度不匹配的问题,树立提高紧急使命优先级、树立相关事情标志、合理地对事情与使命进行同步的改善办法,然后有效地处理组网中最远传输间隔和最大节电数约束的问题。

引 言

CAN总线的直接通讯间隔只要10 km左右,并且因为收发器驱动才能的约束,总线上最多只能挂110个节点,给体系组网带来必定的困难。CAN中继器便是为了处理这个问题而规划的。因为中继器具有数据转发功用,不只能够扩展通讯间隔,还能够添加节点的最大数目。对CAN中继器初始化参数进行设置,能够在不同的网段内选用不同的通讯速率,还能够对报文进行过滤,减轻总线担负。

1 CAN中继器的硬件规划

1.1 微控制器LPC2119简介

CAN中继器是以ARM微控制器LPC2119为中心的软硬件体系。LPC2119是Philips公司出产的一款根据支撑实时仿真和盯梢的16/32位ARM7TDMISMCU,带有128 KB嵌入的高速Flash存储器。共同的加快结构使32位代码能够在最大时钟速率下运转。对代码规划有严格控制的运用可运用16位Thumb形式将代码规划下降超越30 %,而功能的丢掉却很小。LPC2119内部集成2个CAN控制器。它的首要特性有:单个总线上的数据传输速率高达1 Mb/s;32位寄存器和RAM拜访;兼容CAN 2.0B, ISO 118981规范;大局检验滤波器能够辨认一切的11位和29位Rx标识符;检验滤波器为挑选的规范标识符供给Full CANstyle主动接纳。

1.2 LPC2119内部CAN控制器与SJA1000比较

LPC2119内部集成的CAN控制器与Philips公司的SJA1000 CAN控制器相比较大致相同,只是在检验滤波这一环略有不同,这为习气SJA1000的开发人员选用LPC2119供给了便利。SJA1000检验滤波器由检验代码寄存器和检验屏蔽寄存器界说,要接纳报文的位形式在检验代码寄存器中界说,相应的检验屏蔽寄存器答应界说某些位为“无关”,经过形式寄存器能够挑选不同的过滤形式:单过滤形式和双过滤形式。

而对LPC2119内部集成的CAN控制器,大局检验过滤器包括一个512×32(2 KB)的RAM,经过软件处理,可在RAM中寄存1~5个标识符表格,整个RAM可包容1024个规范标识符或512的扩展标识符或两种类型混合的标识符。一起有5个地址寄存器指向检验过滤器RAM的表格:Full CAN规范地址,规范单个地址,规范地址规模,扩展单个地址或扩展地址规模。当CAN控制器的接纳端已接纳到一个完好的标识符时,它将告诉检验过滤器,检验过滤器呼应这个信号,并读出控制器编号、标识符尺度,以及来自控制器自身的标识符,然后经过检验过滤器查找RAM中的表格,以决议接纳或抛弃这一帧信息。

1 .3 CAN中继器硬件结构

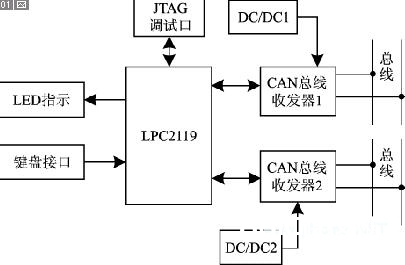

中继器的硬件结构框图如图1所示。LPC2119别离经过CAN总线收发器与两路总线相连;总线驱动器选用带阻隔的DC/DC模块独自供电,不只完结了两路CAN接口之间的电器阻隔,也完结了中继器与CAN总线的电器阻隔。除此之外,还有LED显现和键盘接口。LED用于显现中继器的作业状况,键盘用来批改总线的波特率。终究程序的调试与盯梢经过JTAG调试口完结。

图1硬件结构框图

2 体系软件规划

2.1 引进μC/OSII实时操作体系

跟着运用的杂乱化,选用传统前后台规划办法,会显得过于杂乱,实时性得不到确保,并且容易产生死锁。处理这些问题的最好办法便是选用实时操作体系。

μC/OSII完全是占先式的实时内核, 是根据优先级的, 即总是让安排妥当态中优先级最高的使命先运转, 因而实时性比非占先式的内核要好。 它包括了实时内核、使命办理、时刻办理、使命间通讯同步(信号量、邮箱、音讯行列) 和内存办理等功用; 它的绝大部分代码是用C 言语编写的, 可移植性强, 能够在绝大多数8 位、16 位、32 位以致64 位微处理器、微控制器、数字信号处理器(DSP) 上运转。

CAN中继器对体系的实时性和牢靠性要求比较高。选用μC/OSII实时操作体系能够有效地对使命进行调度;对各使命赋予不同的优先级能够确保使命及时呼应,并且选用实时操作体系,下降了程序的杂乱度,便利程序的开发。

2.2 软件规划中需考虑的问题

(1) 运用代码的容量

在前/后台体系的规划中,对存储器容量的需求只是取决于运用程序代码,而运用RTOS的状况则很不相同。RTOS 内核自身需求额定的代码空间。

总代码量=运用程序代码+内核代码

每个使命都是独立运转的,有必要给每个使命供给独自的栈空间(RAM)。在决议分配给每个使命多少栈空间时,应该尽或许使之挨近实践的需求量。栈空间的巨细不只要核算使命自身的需求(局部变量、函数调用等) ,还需求核算最多中止嵌套层数(保存寄存器、中止服务程序中的局部变量等)。内核的另一个应该具有的特性是,每个使命所需的栈空间巨细能够别离界说。一切内核都需求额定的栈空间,以确保内部变量、数据结构、行列等。假如内核支撑中止用栈别离,则总的RAM需求量的表达式为:RAM总需求=运用程序RAM 需求+内核数据区RAM需求+各使命栈需求的总和+最多中止嵌套栈需求。

除非有特别大的RAM空间能够运用,对栈的分配与运用均要特别当心。实时多使命体系比前后台体系需求更多的代码(ROM) 和数据空间(RAM) 。额定的代码空间取决于内核的巨细,而RAM的用量则取决于体系中的使命数。

(2) 实时性和安全性

CAN中继器是体系组网的关键设备之一,在稍大型的CAN总线体系中经常会用到中继器。它给体系组网带来便利的一起,也给体系添加了一些存储转发时延,因而在软件规划中有必要考虑体系的实时性,尽量缩短数据的存储转发时刻。这除了要求给体系数据转发使命分配较高的优先级之外,还应树立一种通讯机制,确保在收到一路总线上的数据时,能即时向另一路总线发送。别的,中继器是两路总线之间通讯的桥梁,为了确保两路总线之间正常的通讯,应尽量防止相似死锁、总线毛病之类的状况产生。所以体系有必要规划一个监控使命,能对这类状况作出即时反响,一起为了不丢掉还未转发的数据,有必要为每一路总线设置一环形缓冲区,用于寄存新接纳到的数据,保护体系的安全性。