时钟是FPGA规划中最重要的信号,FPGA体系内大部分器材的动作都是在时钟的上升沿或许下降沿进行。无论是在输入,输出或是寄存器与寄存器之间,只需规划到时钟上升沿或许下降沿的采样,就会说到树立时刻(setup time) 和坚持时刻(hold TIme) 。

树立时刻(Tsu:set up TIme)是指在时钟沿到来之前数据从不安稳到安稳所需的时刻,假如树立的时刻不满意要求那么数据将不能在这个时钟上升沿被安稳的打入触发器;坚持时刻(Th:hold TIme)是指数据安稳后坚持的时刻,假如坚持时刻不满意要求那么数据相同也不能被安稳的打入触发器。

树立时刻和坚持时刻这两个目标阐明器材自身不是抱负的(有时延等),正是这个不抱负的特性,约束了FPGA的时钟作业频率。

首要咱们都知道setup TIme 和holdup time是由器材决议的,并不是说能够跟着你FPGA规划的改动而改动。那么FPGA时钟频率是怎样核算的呢,在不考虑时钟延时颤动等条件下,一个信号从触发器的D端到Q端的延时假设是Tcd,从Q端出来之后会通过组合电路延时,这儿留意即便没有组合电路,就单单通过导线也是有延时的,这个延时称作Tdelay,通过这个延时之后,信号将要去下一个触发器,并且必需求满意触发器的树立时刻tsetup,不然时钟无法采样到安稳的数据。

所以这三个时刻加起来应该比时钟周期要小,不然数据无法打入下一个触发器,那就会进入亚稳态。Tcd+Tdelay+Tsetup

至于FPGA时钟频率与holdup time的联系,详细做规划的时分仍是需求满意Tcd+Tdelay+Tsetup

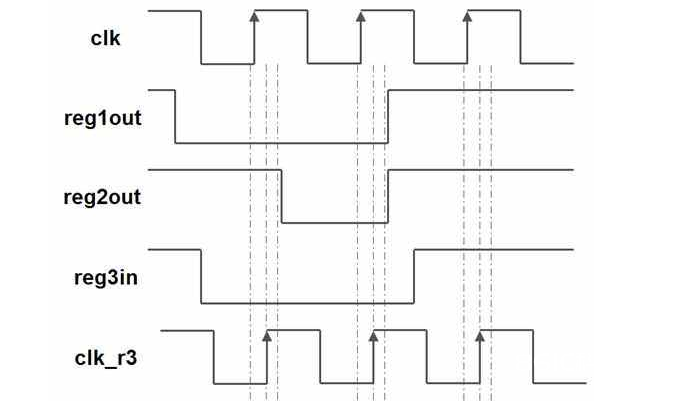

树立时刻与坚持时刻的简略示意图如下图1所示,在图1中咱们看到clk_r3的前后各有一条虚线,前一条虚线(最左面的虚线,左面代表呈现时刻早,与modelsim仿真时信号顺次从左往右呈现)到clk_r3上升沿的这段时刻即为树立时刻,clk_r3上升沿到后一条虚线(最右边的虚线)的这段时刻即为坚持时刻。

前面临树立时刻和坚持时刻下定义时说到过,在这段时刻内不能够有数据的改变,数据有必要坚持安稳。而在这个波形中,也的确没有看到在树立时刻和坚持时刻内,reg3in的数据有任何的改变,因而咱们能够安稳的将reg3in的数据锁存到reg3的输出reg3out中。

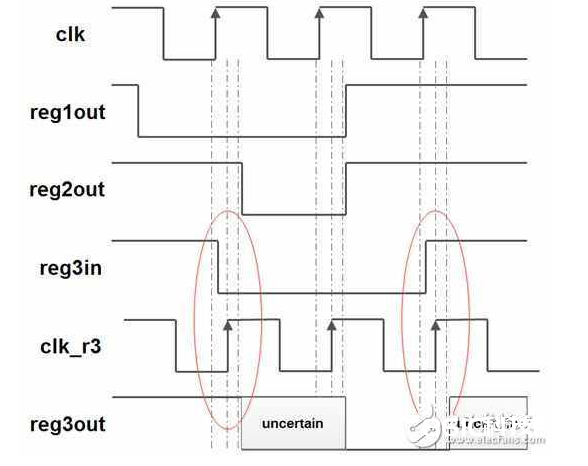

相同的一些信号,但咱们发现reg3in在clk_r3的树立时刻内发生了改变,这带来的结果便是clk_r3上升沿锁存到的reg3in数据不确认,那么随后的reg3out值也会处于一个不确认状况。比方第一个时钟周期,本来reg3in应该是安稳的低电平,可是因为整个途径上的延时时刻(Tcd+Tdelay)过长,导致了reg3in在clk_r3的树立时刻内数据还未能安稳下来,在树立时刻内信号呈现了电平从高到低的改变,即不安稳的状况,那么导致的结果便是reg3out的终究输出不是确认的状况,很可能是忽高忽低的亚稳态,而不是本来希望的低电平。

咱们再来看看坚持时刻违规的状况,这次是数据传输得太快了(不满意Tcd+Tdelay>Tholdup,也便是Tcd+Tdelay时延太小),本来应该下一个时钟周期抵达clk_r3的数据居然在clk_r3的前一个时钟周期的坚持时刻还未曩昔就来到了。因而,它呈现的终究损害也是后端输出的reg3out处于不确认的状况。