HMC7044相关信息来自ADI官网,详细参数以官网发布为准,HMC7044供给信息可在查IC网查找相关供给商。

产品概况

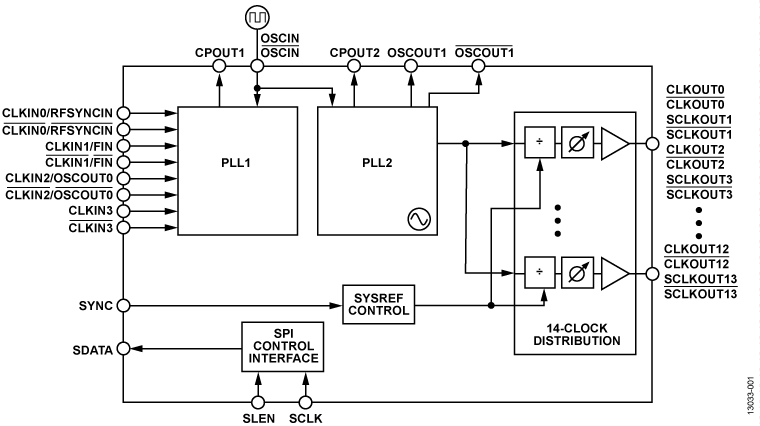

HMC7044是一款高性能双环路整数N分频颤动衰减器,能够挑选参阅并生成超低相位噪声的频率,支撑配有并行或串行(JESD204B型)接口的高速数据转换器。 HMC7044具有两个可经过SPI挑选的整数形式PLL和交叠的片内VCO,调谐规模别离达2.5 GHz和3 GHz。 该器材旨在满意GSM和LTE基站规划的要求,并经过多种时钟办理和分配特性来简化基带和无线电卡时钟树的规划。 HMC7044供给14路低噪声且可装备的输出,能够灵敏地与许多不同器材接口,包含数据转换器、现场可编程门阵列(FPGA)和混频器本振(LO)。

HMC7044的DCLK和SYSREF时钟输出可装备来支撑CML、LVDS、LVPECL和LVCMOS等信号规范,不同的偏置设置则可抵消改变的板插入损耗。

使用

- JESD204B时钟发生

- 蜂窝基础设施(多载波GSM、LTE、W-CDMA)

- 数据转换器时钟

- 微波基带卡

- 相控阵参阅分配

优势和特色

- 超低rms颤动: 典型值:44 fs(12 kHz至20 MHz,2457.6 MHz)

- 噪底: −156 dBc/Hz (2457.6 MHz)

- 低相位噪声: −141.7 dBc/Hz(800 kHz时,983.04 MHz输出)

- PLL2最多供给14路LVDS、LVPECL或CML型器材时钟(DCLK)

CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUT最高频率达3200 MHz - JESD204B兼容体系参阅(SYSREF)脉冲

- 25 ps模仿推迟和½ VCO周期数字推迟,14个时钟输出通道各自都能对推迟进行编程

- 相位噪声与功耗的联系可经过SPI编程

- SYSREF有用中止可简化JESD204B同步

- 窄带、双核VCO

- 最多2个缓冲压控振荡器(VCXO)输出

- LVDS、LVPECL、CMOS和CML形式下最多4个输入时钟

- 频率坚持形式可坚持输出频率

- 信号丢掉(LOS)检测和无中止参阅切换

- 4个GPIO报警/状况指示器,可确认体系健康程度

- 支撑最高6000 MHz的外部VCO输入

- 片内稳压器供给超卓的PSRR

- 68引脚、10 mm × 10 mm LFCSP封装

HMC7044电路图

HMC7044中文PDF下载地址

HMC7044下载链接地址:https://www.analog.com/media/cn/technical-documentation/data-sheets/HMC7044_cn.pdf