一、AD9850简介

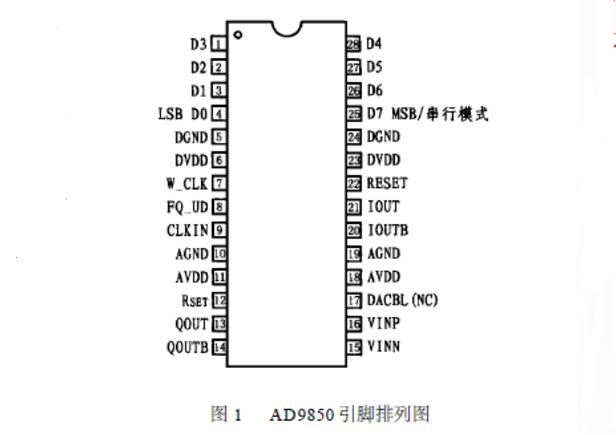

AD9850是美国AD公司选用先进的DDS技能,1996年推出的高集成度DDS频率合成器,选用CMOS工艺,其功耗在3.3V供电时仅为155mW,扩展工业级温度规模为-40~80℃,选用28脚SSOP外表封装方式。它内部包含可编程DDS体系、高性能DAC及高速比较器,能完成全数字编程操控的频率合成器和时钟发生器。接上精细时钟源,AD9850可发生一个频谱纯洁、频率和相位都可编程操控的模仿正弦波输出。此正弦波能够直接作为信号源输出或许送入AD9850的高速比较器然后得到方波输出。AD9850接口操控简略,能够用8位并行口或串行口直接输入频率、相位等操控数据。32位频率操控字,在125MHz时钟下,输出频率分辨率为0.029Hz,频率规模为0.1Hz~40MHz,幅值规模为0.2~1V。其引脚摆放如图1所示,各引脚界说如下:

D0~D7(4-1,28-25):操控字并行输入,给内部寄存器装入40位操控数据,其间D7可做串行输入

DGND(5、24):数字地

DVDD(6、23):为内部数字电路供给电源(3.3V或5V)

W-CLK(7):操控字装入时钟,用于加载并行/串行的频率/相位操控字,上升沿有用FQ-UD(8):频率更新操控信号,时钟上升沿承认输入数据有用

FQ-UD(8):频率更新操控信号,时钟上升沿承认输入数据有用FREFCLOCK(9):外部参阅时钟(有源晶振)输入,最高125MHz

AGND(10、19):模仿地

AVDD(11、18):为内部模仿电路供给电源(5V),可与数字电源共用

Rset(12):外接电阻,决议器材输出电流巨细,典型值为3.9K

QOUT(13):内部比较器正向输出端(方波)

QOUT(14):内部比较器反向输出端(方波)VINN(15):内部比较器的负向输入端

VINP(16):内部比较器的正向输入端

DACBL(17):内部DAC外接参阅电压端,可悬空

IOUTB(20):“互补”DAC输出

IOUT(21):内部DAC输出,抢先电流输出端,一般用电阻接地以转换为正弦电压

RESET(22):复位端

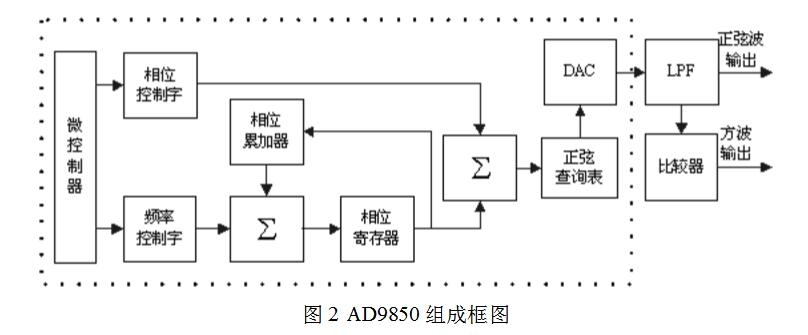

可编程DDS体系的中心是相位累加器,它由一个加法器和一个N位相位寄存器组成,N一般位24~32。每来一个外部参阅时钟,相位寄存器便以步长M递加。相位寄存器的输出与相位操控字相加后可输入到正弦查询表地址上。正弦查询表包含一个正弦波周期的数字起伏信息,每一个地址对应正弦波中0°~360°规模的一个相位点。查询表把输入地址的相位信息映射成正弦波起伏信号,然后驱动数模转换器(DAC)以输出模仿量,如图2所示。

二、AD9850原理

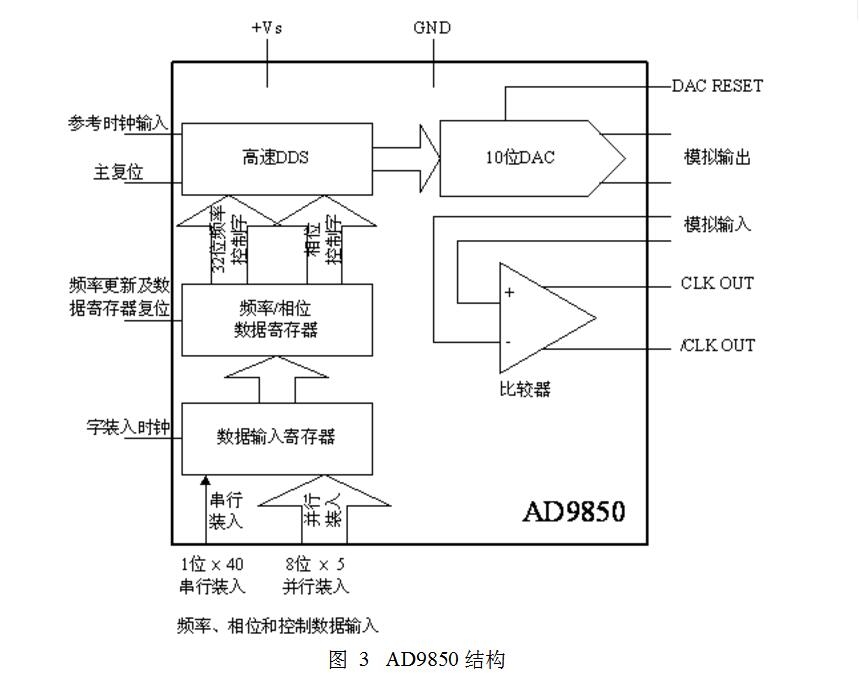

其内部原理结构如图3所示。

由此可见可见,AD9850首要组成有三部分:一是高度DDS内核,是AD9850的中心,包含相位寄存器、频率寄存器、相位累加器、波形ROM;二是接口电路,即输入寄存器,用于接纳单片机送来的40bit数据;三是模仿电路部分,即DA转换器及比较器。