手上有一块黑金AX309的板子,Jtag口的排针距离是2.0mm,而我zturn board上的下载线距离是2.54mm,贼为难。然后焊了一个转接板处理了,可是比较费事。最要害的是现在呈现了在ISE上找不到设备的状况,不知道是我焊接的不结实仍是我带电插拔把JTAG口烧坏(带电插拔JTAG口会损坏FPGA芯片的JTAG口管脚)。

按道理现在板子高档了,应该都会有维护电路的吧,可是仍是要慎重啊。

正确的插线上电次序:

1.封闭FPGA开发板电源;

2.将JTAG仿真的器经过JTAG排线缆接到FPGA开发板上;

3.在仿真器的USB口上刺进USB线缆(另一端需求插在电脑上)

4.翻开FPGA开发板上的电源开关

要害是最后上电。

正确的断电拔线次序:

1.封闭FPGA开发板的电源;

2.拔下下载器上的USB线;

3.拔掉FPGA开发板上的JTAG衔接。

要害是先断电。

怎么查看JTAG口的FPGA管脚是否被击穿?

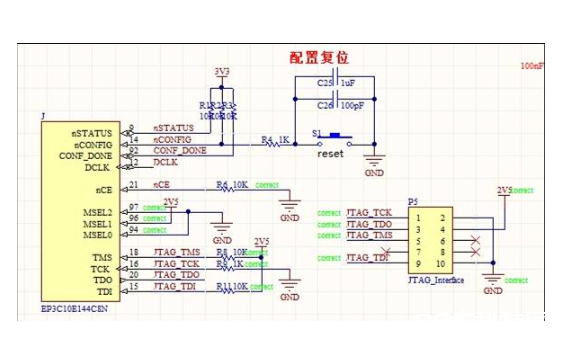

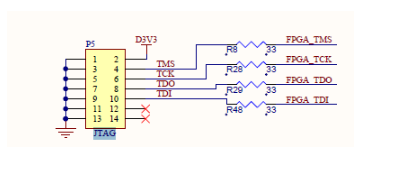

因为平时会手贱,我或许一不留神就“带电操作了”。一次两次或许幸运没事,但常在河边走哪有不湿鞋的,这一次怕是风险了。在扫除下载线自身的问题后,假如不能拜访FPGA的JTAG口很有或许是FPGA芯片上的JTAG口管脚损坏了,查看也很简单,只需用用万用表查看JTAG口中的TCK、TMS、TDO和TDI是否和GND短路,即接地了。假如任何一个信号与对地信号短路都表明JTAG信号管脚损坏。

原因剖析:

关于一些低端芯片,为节约本钱,简化规划,FPGAIO单元都没有维护电路,假如 带电插拔会有必定概率导致JTAG口上的静电和浪涌,终究导致FPGA管脚的击穿(FPGA的IO口假如加上二极管钳位维护电路 就问题不大了)。

FPGA程序烧写方法——AS、PS JTAG

FPGA器材有三类装备下载方法:

1.主动装备方法(AS)

2.被迫装备方法(PS)

3.JTAG

AS形式(Active Serial configraTIon mode):FPGA每次上电时作为操控器,由FPGA 器材引导装备操作进程,它操控着外部存储器和初始化进程,向装备器材主动宣布读取数据信号,从而把EPCS**的数据读入FPGA中,完结对FPGA的编程。

PS形式(Passive Serial configaraTIon mode):由外部计算机或许操控器操控装备过 程,经过加强型装备器材(EPC16,EPC8)等装备器材来完结。EPCS作为操控器材,把FPGA当作存储器,把数据 写入FPGA中,完结对FPGA编程,该形式能够完结对FPGA的在线编程。

JTAG形式:JTAG是直接烧写到FPGA里边的,因为是烧写到SRAM中,因而断电后需求从头烧写,AS是烧写到FPGA的装备芯片中(比方能够 bit先文件烧写到FPGA板上的Flash上进行保存,每次上电后FPGA将主动去读写Flash对FPGA进行烧写)。