二分频电路

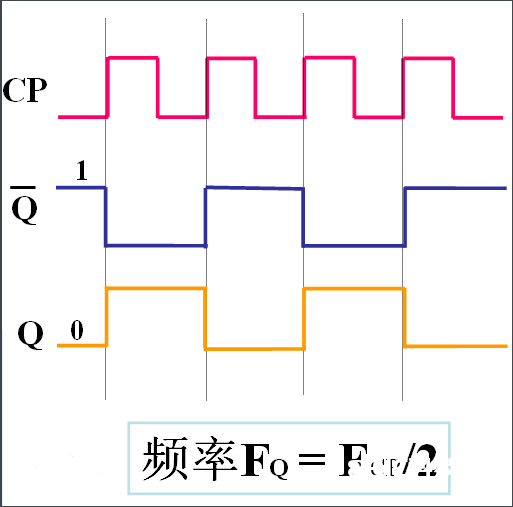

分频便是用同一个时钟信号经过必定的电路结构转变成不同频率的时钟信号。而二分频便是经过有分频效果的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

比如用一个脉冲时钟触发一个计数器,计数器每计2个数就清零一次并输出1个脉冲,那么这个电路就完成了二分频功用。

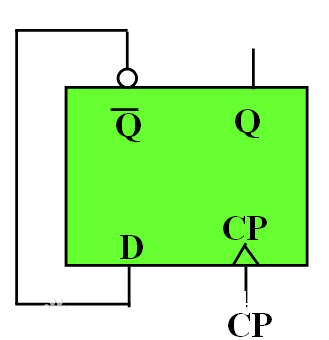

用D触发器完成

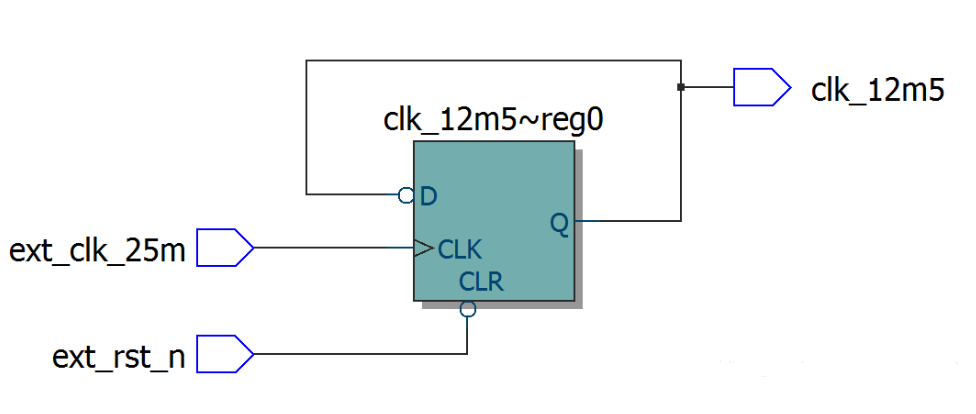

电路衔接图如图1:

时序图如图2:

二分频电路及代码

module cy4(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有用

output reg clk_12m5 //二分频时钟信号

);

always @(posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) clk_12m5 《= 1‘b0;

else clk_12m5 《= ~clk_12m5;

endmodule