实例的内容及方针

1.实例的首要内容

本节经过Verilog HDL言语编写一个具有“百分秒、秒、分”计时功用的数字跑表,能够完结一个小时以内准确至百分之一秒的计时。

数字跑表的显现能够经过编写数码管显现程序来完结,本实例只给出数字跑表的完结进程。读者还能够经过添加小时的计时功用,完结完好的跑表功用。

2.实例方针

本实例首要完结了计数及进位的规划,经过几个always模块的规划完结一个特定用处的模块——数字跑表。经过本实例,读者应到达下面的一些实例方针。

• 开端把握Verilog言语的规划办法。

• 完结一个数字跑表的规划。

原理简介

本数字跑表首要要从最低位的百分秒计数器开端,依照体系时钟进行计数。计数至100后向秒计数器进位,秒计数器以百分秒计数器的进位位为时钟进行计数。计数至60后向分计数器进位,分计数器以秒计数器的进位位为时钟进行计数,读者能够自行添加小时计数器。

数字跑表奇妙地运用进位位作为计数时钟来削减计数的位数。假如一致运用体系时钟作为计数时钟,那秒计数器将是一个6000进制的计数器,而分计数器将是一个3600000进制的计数器。这样将极大的糟蹋FPGA的逻辑资源。而运用进位位作为计数时钟,只需要一个100进制的计数器和两个60进制的计数器。

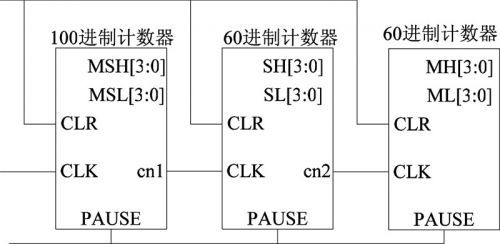

如图是本实例的数字跑表模块图。

在实践的规划中,为了使计数器愈加简略,计数器运用高低位两个计数器完结。100进制计数器分别是高位10进制计数器,低位10进制计数器;60进制计数分别是高位6进制计数器,低位10进制计数器。这样整个数字跑表运用6个计数器完结。

一起因为10进制计数器重复运用了5次,能够运用独立的模块完结10进制计数器,这样就能够经过模块复用来节约整个模块运用的资源。

数字跑表供给了清零位CLR和暂停位PAUSE,百分秒的时钟信号能够经过体系时钟分频供给。分频至1/100s,即可完结实在的时刻计数。具体的时钟分频规划读者可参阅相关的材料完结,在本实例中不再供给。