1 导言

ARCNET协议使用于高速动车组列车通讯网络时,发生中心操控单元处理器PXA270与专用协议操控器材COM20020相连的时序不匹配问题,若用通用数字电路模块进行时序转化,PXA270需占用PXA270专门的资源(CPU时刻片)对 COM20020的寄存器、数据包缓冲区进行低速读写拜访(对COM20020的相邻两次读操作相隔至少300 ns),这样将添加处理器的担负。依据这种现状,提出一种依据FPGA的PXA270外设时序转化接口规划方案,以FPGA为桥梁进行时序转化,并添加存储器直接拜访DMA(Direct Memory Aeeess)功用,即FPGA主动完结数据包的收发作业,PXA270则只需高速读写拜访FPGA中的同步双口RAM。

2 时序转化接口全体规划

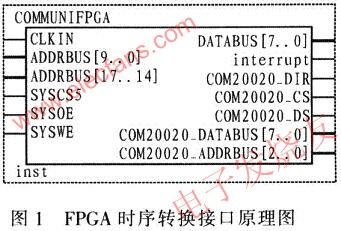

2.1 FPGA对外接白

选用FPGA衔接PXA270处理器与外设以处理PXA270处理器与外设直接衔接时的时序不匹配问题。如图1所示,FPGA从PXA270处理器取得地址总线(ADDRBUS[17..14], ADDRBUS[9..0]),片选信号(SYSCS5),读答应(SYSOE),写答应(SYSWE),并供给双向数据端口DATABUS[7..0] (可依据实践使用修正为32位或16位等),中止(interrupt);一起,FPGA向COM20020供给特定的总线接口,包含 COM20020_DS,COM20020_CS,COM20020_DIR,COM20020_DATABUS [7..0],COM20020_ADDRBUS[2..0]等。

2.2 内部功用完结

PXA270和外设之间的衔接是将FPGA中的双口RAM作为数据中转站,以此直接相连。该规划由以下4个功用模块组成。

(1)PXA270对外设指定寄存器单次写操作PXA270先将所要写的数据送人双口RAM,然后PXA270向FPGA的指令寄存器写入对该外设指定寄存器的单次写指令,然后FP-GA依据接纳到的指令将RAM中的数据输出到外设数据总线,一起给出对外设的写时序。

(2)PXA270对外设指定寄存器单次读操作PXA270先向FPGA的指令寄存器写入对该外设指定寄存器的单次读指令,此刻,FPGA给出对外设的读时序,并驱动RAM的地址总线、写时钟等信号,将外设数据总线上的数据传送到RAM中。再延时1μs,PXA270从RAM中读出数据。

(3)PXA270对外设批数据写操作与单次写操作不同的是,PXA270需先将所要写入的数据存储到RAM的接连空间,然后向FPGA的指令寄存器写入批数据写操作指令,FP-GA依据接纳到的指令将RAM中的数据分次送至外设数据总线,且需保证向COM20020的写时序与之同步。

(4)PXA270对外设批数据读操作 由FPGA给出对外设的接连屡次读时序将外设中的数据送人RAM,完结存储作业。PXA270等待批数据读完结中止发生后对RAM进行接连读。

3 功用模块规划

3.1 时序发生模块规划

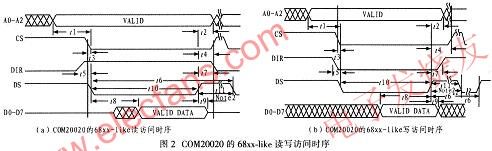

COM20020有80xx-like和68xx-like两种总线拜访方法。这儿中完结68xx-like拜访方法,图2为其读写拜访时序。

读写时序的一起要求为:片选信号CS有必要先于DS至少5 ns,而且只答应在DS无效之后CS才干康复为高电平;读写方向信号DIR应在DS有用前至少10 ns树立;DS高电平宽度不小于20 ns。两者的不同要求:写时序的地址总线先于操作脉冲DS至少15 ns树立,DS低电平不小于20 ns,数据总线有用数据有必要在DS变高之前至少30 ns树立,坚持至DS变高后至少10 ns;而读时序的地址总线先于片选信号至少15 ns树立,DS低电平不小于60 ns,DS变低到数据总线数据有用的距离最大为40 ns,DS变高到数据总线高阻抗的距离最大为20 ns,这是COM20020作为数据输出方给拜访设备供给的特性。针对以上读写时序的要求,详细规划如下:DIR在一次操作中只要高或低电平一种或许,经过指令寄存器在操作前事先给出,然后给出使能信号,DS在CS有用之后变低,而在CS无效之前变高,以便数据牢靠锁存。

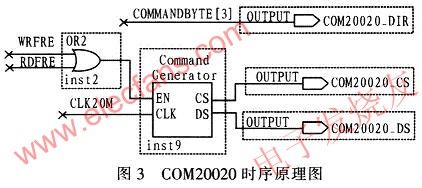

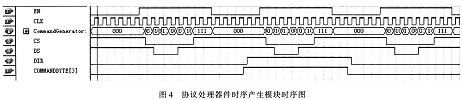

图3为COM20020的时序原理图,从时序剖析可得出如下规划方案:DIR用于指示操作是读仍是写,DIR=‘1’为读,不然为写。在操作前先对DIR 赋值;在EN有用时挑选CS,CLK的下一次上升沿变为有用。这样是给写操刁难COM20020数据总线预备数据之用,不影响读操作;DS挑选在CS有用的下一个CLK上升沿变为有用,但在CS无效前两个时钟周期给出上升沿,以满意“片选信号CS有必要先于DS至少5 ns,而且只能在DS无效之后康复为高电平”,而且DS中心应有至少60ns的时钟宽度,因此坚持3个CLK周期有用。图4为CommandGenerator时序仿真图。选用计数器进行时序同步。以下给出VHDL源代码。

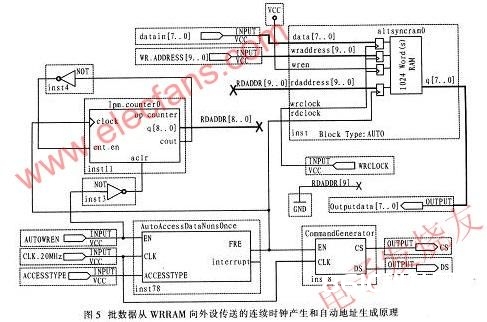

图5为批数据从WRRAM向外设传送的接连时钟发生和主动地址生成原理图。其间,lpm_counter0为带有异步清零和进位信号的增计数; AutoAccessDataNumsOnce在EN=’1’时,发生一次批传送时钟,依据COM20020的长短数据包传送要求,在CCESSTYPE =‘1’时传送长数据包(512 B),不然传送短数据包(256 B)。FRE信号一起供给WRRAM的rdclock和lpm_counter0的clock信号。

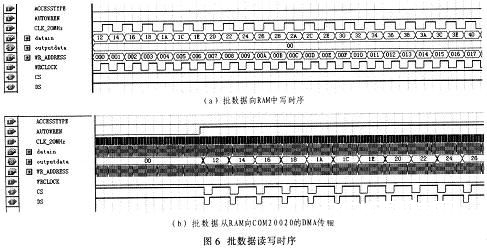

图6为一次批数据向RAM中写,然后发动DMA传输,将数据从RAM送至COM20020的时序仿真。在WRCLOCK上升沿时,RAM将datain总线上的数据存储到WR_AD-DRESS所指向的字节地址空间,WRCLOCK信号是由PXA270的WE信号与分配给RAM的片选信号(高电平有用)相与而得。对RAM进行模拟写时有必要保证AUTOWREN无效(低电平);在查验数据DMA传输的RAM输出环节,WRCLOCK应不再呈现上升沿信号,以防RAM一起读写形成输出不定值。此外,每个数据从outputdata端口输出时,CS、DS在必定延时后(1个CLK时钟周期)给时序发生留满足时刻。需阐明:COM20020内部有2 K字节的RAM空间,用于寄存待发送或已接纳的数据包,在向RAM中写数据包前,指定该数据包的寄存方位,然后将COM20020中的指针主动移动方位 1,则只需接连的向该RAM中写数据,而不用给出地址信号。

3.3 对外设指定寄存器操作

对外设指定寄存器操作比批数据传送完结简略,只需将操作次数降为1次,并对 COM20020的A2~A0供给相应的地址即可。指定寄存器操作将数据存储在RAM的高512字节空间,而且只占用其间低8个字节,在PXA270编程时,需保证PXA270送入RAM的地址与指令寄存器中的RAM存储地址COMMANDBYTE[2..0]相对应。

4 定论

本规划处理ARCNET协议专用器材使用于列车通讯网络中的时序匹配问题,完结了PXA270处理器与COM20020的时序转化。此外,对扩展其他总线拜访类型供给了参阅结构,可经过修正CommandGenerator中COM20020时序,完结不同外设总线拜访类型的扩展;修正 AutoAccessDataNun-sOnce中的ACCESSTYPE,可装备批数据操作的数据品种。