本文首要介绍了高速串行链路规划中AC耦合电容阻抗优化的重要性,然后论述怎么运用Xpeedic姑苏芯禾科技公司旗下软件ViaExpert对AC耦合电容规划进行前仿真,然后辅导后续PCB规划,终究PCB完结后进行后仿真,完结仿真的闭环规划。

1 导言

跟着高速串行总线的速率越来越高,链路的阻抗也随之成为SI工程师重视的焦点。由于高速串行总线链路中仅有的无源器材便是AC耦合电容,所以在咱们对传输线阻抗以及过孔或许衔接器的PIN的阻抗优化之后,剩余的也便是AC耦合电容的阻抗的优化,当然25Gbps链路为了进一步减小AC耦合通道阻抗不接连性的影响,IC厂家直接把AC耦合电容规划在接纳端芯片这儿,所以关于正在规划10Gbps链路的运用,AC耦合电容成为SI工程师的必修课了。

AC耦合电容的阻抗仿真,由于需求考虑到焊盘和GND或许POWER平面的容性耦合,所以惯例在HFSS中建模会比较消耗时刻,现在芯禾科技推出的ViaExpert建模东西能够针对各种叠层和电容封装进行AC耦合电容阻抗优化前仿真,后续布线阶段也能够导入Brd文件提取出AC耦合电容的焊盘尺度和掏空的层数和巨细,终究仿真出你所能承受的阻抗规划。

2 AC耦合电容的掏空规划

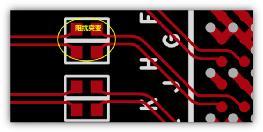

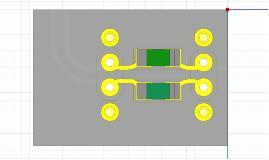

AC耦合电容焊盘比较链路的走线会比较宽,这样关于高速信号传输来说便是一处阻抗不接连点(如图1),为确保阻抗的共同性,AC耦合电容的下方需求做多层的掏空,可是由于PCB规划的第3层或许倒数第3层通常是POWER层,挖空后可能会导致BGA IO口模仿电源的压降问题;现在许多电源模块都具有Remote Sense功用,能够补偿PCB压降问题,所以AC耦合电容焊盘下方做多层掏空也是能够的。

在此布景下,咱们就需求一种仿真东西能够对掏空巨细和掏空层数做阻抗优化仿真,经过调整AC耦合电容焊盘下方的挖空巨细以及挖空的层数来确认单板依据某种叠层下的焊盘阻抗是否比较挨近差分传输线的阻抗,终究给出PCB规划的优化规矩。后续我将介绍怎么运用芯禾科技推出的ViaExpert软件进行AC耦合电容阻抗优化仿真的规划。

图1 高速串行链路中AC耦合电容的规划

3 AC耦合电容阻抗前仿真优化

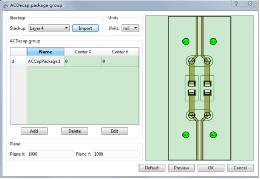

在芯禾科技发布的最新ViaExpert版别中,有专门针对AC耦合电容阻抗仿真的优化流程,软件界面如下图2所示。叠层能够运用软件默认设置也能够由用户PCB叠层,经过Import按钮导入。AC耦合电容这儿能够支撑一对差分也能够支撑多对差分进行AC耦合电容的串扰仿真,这儿咱们只以单对差分为例进行仿真。

图2 AC耦合电容建模初始界面

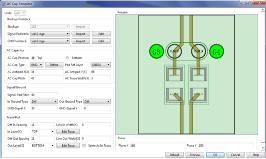

上图确认好叠层和AC耦合电容的对数之后咱们就能够对单对AC耦合电容的出线及信号孔和地孔做更详细的设置,详细设置信息如下图3所示。

图3 AC耦合电容建模设置

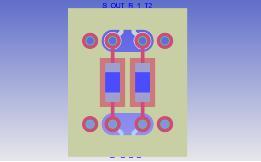

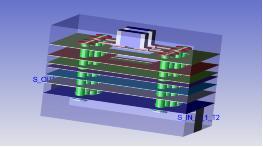

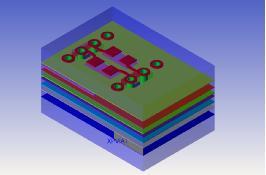

这儿咱们以0402的AC耦合电容为例进行仿真,一端Botm层经过换层过孔衔接Top面的AC耦合电容,别的一端经过过孔再衔接到Art12层,这儿咱们别离仿真3种状况;电容掏空到GND02层,X方向掏34mil,Y方向掏66mil(Case1)。模型建好后的3D效果图如图4所示。

图4 AC耦合电容3D效果图(Case1)

电容掏空到GND02层,X方向掏28mil,Y方向掏58mil(Case2),如图5所示。

图5 AC耦合电容3D效果图(Case2)

电容掏空到POWER04层,X方向掏34mil,Y方向掏66mil(Case3),如图6所示。

图6 AC耦合电容3D效果图(Case3)

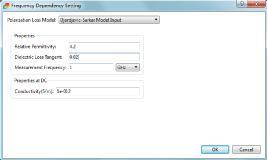

模型生成好后,电容出线的两头会主动生成Wave Port,所以不需求你手动去设置Port,这儿还有一点便是资料的参数以及孔径需求你去设置,资料参数设置由于是前仿真,所以用Djordjevic-Sarkar Model Input简略的频变模型(图7),只需求设置一个频点的Dk和Df值就能够求解宽带的频变曲线。详细设置界面如下所示,这儿咱们板材选用FR-4,Dk和Df的值挑选1GHz频点。

图7 Djordjevic-Sarkar Model Input

Case1和Case2参数别离设置好之后,咱们就能够开端仿真,仿真频率规模设为10MHz-20GHz频段。详细设置如下图8所示,芯禾科技在最新的版别傍边加入了Dense Mesh功用,能够在对结构杂乱区域添加Mesh的数量,客户能够经过勾选项自行挑选。

图8 仿真引擎设置

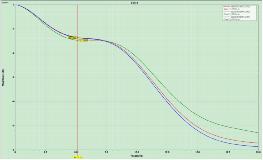

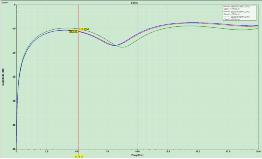

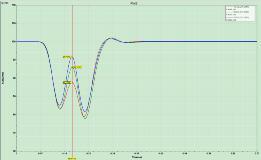

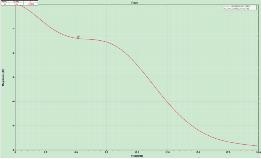

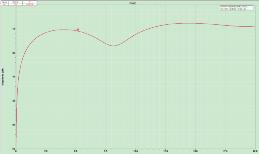

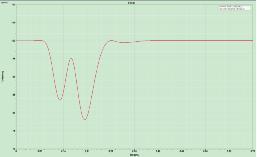

下面是Case1,Case2,Case3三种状况下AC耦合电容插入损耗,回波损耗以及差分阻抗曲线,别离如图9,图10及图11所示。这儿运用的是Xpeedic公司的SnpExpert对S参数进行比较。

图9 3种Case的插入损耗曲线

图10 3种Case的回波损耗曲线

图11 3种Case的差分阻抗曲线

从以上3种状况的仿真成果能够看出,掏空2层的阻抗是最挨近100ohm的,所以在5.16GHz基频处的插入损耗和回波损耗也是最优异的,可是和掏空1层的成果不同不是太大,Case2状况是最差的,由于掏空区域变小了,差分阻抗变低了。所今后续咱们在PCB规划阶段就能够依据以上前仿真成果进行辅导,关于通流比较严重的状况,咱们只掏空GND02层的地,关于POWER03或许ART03空间宽余的状况下,能够掏2层处理。

4 AC耦合电容阻抗后仿真验证

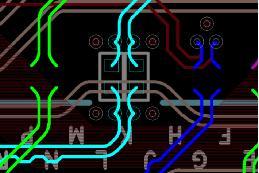

依据上节3种Case状况下的仿真成果和PCB规划的实践状况,AC耦合电容只掏空GND02层,掏空尺度为X方向掏34mil,Y方向掏66mil。由于ViaExpert能够直接导入Brd文件,所以在PCB规划完结后在ViaExpert里边直接对Brd进行解析,提取出板上的AC耦合电容和出线。PCB实践AC耦合电容的规划以及导入到ViaExpert中提取完结的3D效果图别离如图12和图13所示。

图12 实践AC耦合电容出线

图13 实践AC耦合电容3D效果图

由于ViaExpert里边提取Brd无法取得电容相应的模型,所今后仿真需求把模型导入到HFSS中,然后加上AC耦合电容的Model,终究如图14所示。

图14 实践AC耦合电容3D效果图

仿真成果如下图15,图16,图17所示。根本和前仿真成果共同

图15 实践AC耦合电容后仿真插入损耗

图16 实践AC耦合电容后仿真回波损耗

图17 实践AC耦合电容后仿真差分阻抗

5 定论

本文介绍了怎么运用Xpeedic公司旗下的ViaExpert软件对高速串行链路AC耦合%&&&&&%的前仿真差分阻抗优化以及PCB后仿真建模,前仿真得出规划方向后辅导PCB规划,终究后仿真确认规划是否满足要求,终究确保高速串行链路规划的一板成功。