现在大多数仪器选用封闭式FPGA(现场可编程门阵列)和固定的固件完结仪器的功用。假如你曾见过示波器的拆解,你或许见过里边的FPGA。FPGA能够添加测验仪器的处理才能,假如你曾运用过仪器的敞开式FPGA,你就会知道能够将自界说的测验功用编程进仪器中。

仪器供货商早就了解FPGA的优点,并且一直在充分发挥FPGA共同的处理才能优势来丰厚的功用,比方:仪器

● 能够在示波器上完结预触发捕获

● 能够运用信号处理功用在矢量信号分析仪上产生I和Q数据

● 能够在高速数字仪器上实时进行图画产生和矢量比较

测验设备制造商现在开端向用户敞开FPGA以供给更多特别运用的优化。为了协助了解为何这是一个好的改变,下面列出了在测验运用中运用FPGA的一些要害特性:

● 确定性,实时处理

● 真实并行的履行

● 可重装备

● 低延时

更进一步讲,运用敞开式FPGA能够完结哪些曾经不能完结的功用呢?为了描绘这些可能性,下面将介绍一些运用敞开式FPGA的常见测验运用。

测验体系加快

在大批量出产线的终究产品测验中,每一秒的测验时刻都很名贵。当产品测验速度与出产速度相匹配时,出产线的功率便是最高的。当两者速度不匹配时,就必须选用立异的技能来缩短测验时刻。传统办法需求运用多台分隔的台式仪器,它们经过以太网、USB或GPIB衔接到一台PC主机。这种测验的速度相对较慢,由于待测设备的操控、丈量以及经过数据总线的处理是分隔进行的。别的一种办法是运用敞开式FPGA来加快这个进程,如图1所示。

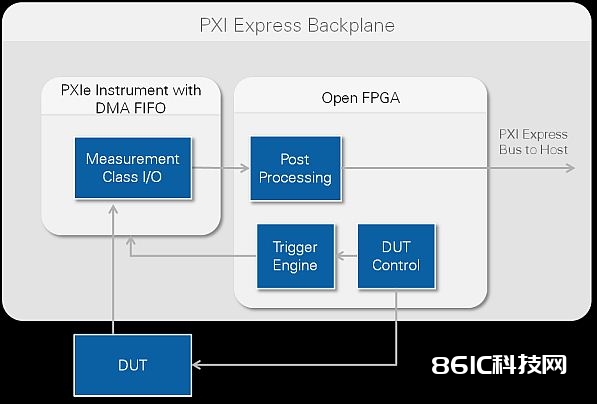

图1:在测验仪器中,敞开式FPGA能够添加比方触发和后处理等功用。

与运用外部通讯总线不同,FPGA能够运用高速总线(如PXIe)衔接仪器,并经过其装备端口(如I2C、SPI或别的的操控总线)衔招待测设备(DUT)。这种运用中的FPGA能够操控待测设备,触发其它仪器开端捕获样本,乃至将这些样本处理成对主机来说有意义的成果。

低时延是加快这类运用的一个要害因素。FPGA没有操作体系,但一切的逻辑都是用硬件完结,并且这些硬件作业的时钟速率很高。这意味着呼应只需花一个时钟周期捕获、一个时钟周期处理和一个时钟周期输出成果。当时钟速率为200MHz(时钟周期为4ns)时,完好的呼应时刻只需12ns。由于FPGA确实定性特色,12ns的呼应时刻不是只要一次,而是每次都是。因而FPGA不只能够避免与运用主机有关的延时,并且能够最大极限地减小主机处理时的非确定性延时。

协议的处理

今日,并不是一切数字和MEMS设备都能用已知成果矢量进行测验。就拿脉冲密度麦克风(PDM)来说,假如给它一个鼓励信号,你不能希望每次测验得到的比特流是完全相同的,这是由于PDM是模仿设备。为了从这些类型的待测设备取得有意义的成果,在比较成果之前你首要需求用其特定的协议对数字流进行解码。凭借敞开式FPGA,你能够在FPGA上装备你的测验体系来完结PDM协议,不用再传至CPU进行解说。进一步拓宽这个概念,今日你能够装备这个FPGA完结PDM协议,明日你又能够重新装备相同这个FPGA完结不同的协议,比方用于测验数字温度传感器、加快度计或MEMS设备的协议。

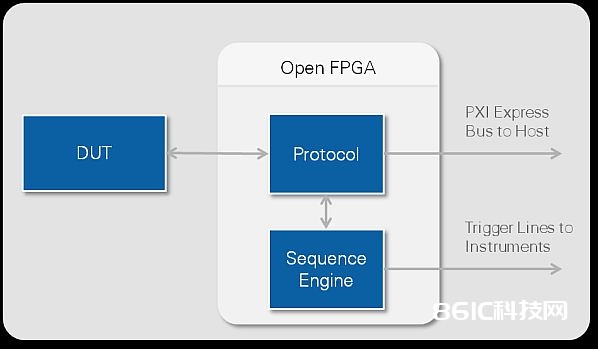

在图2中,协议不是在CPU上完结,而是在FPGA上完结。正由于此,测验体系现在本身就能够支撑快速握手脚本,习惯准确等候周期等协议行为,并依据通讯内容做出决议计划。这种办法不只能让你从待测设备接纳更高层数据,比方在PDM麦克风场合中解码的模仿数据,并且答应你用更高层指令编写测验脚本。

图2:FPGA能够用来处理协议,知晓总线运用的协议内容。