摘要:DEI1016是一种可支撑ARINC429航空总线协议的串行接纳、发送器材。文中介绍了DEI1016的主要功用和作业原理,给出了DEI1016的数据收发进程,一起要点介绍了DEI1016与AT89C52单片机接口电路的规划办法。 关键词:DEI1016;接纳;发送;接口规划;AT89C52 1 DEI1016的主要功用 DEI1016是Device Engineering Incorporated 出产的一种可支撑ARINC429航空总线协议的串行接纳、发送器材。该器材的主要功用如下: ●串行数据字长为32或25位; ●串行数据速率为100kbps或12.5kbps; ●具有独立的收、发电路; ●两个独立的接纳器可直接与ARINC429总线接口; ●具有串/并接纳数据转化,和并/串发送数据转化功用; ●对接纳的数据可进行奇偶状况校验;并可对发送数据奇偶状况进行设置; ●可主动发生字与字之间的距离; ●选用单一+5V供电。

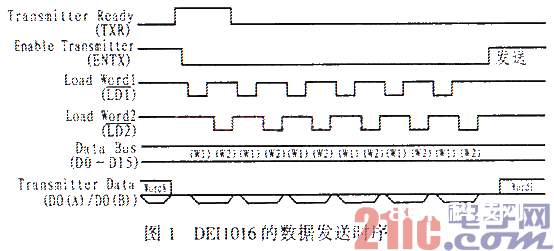

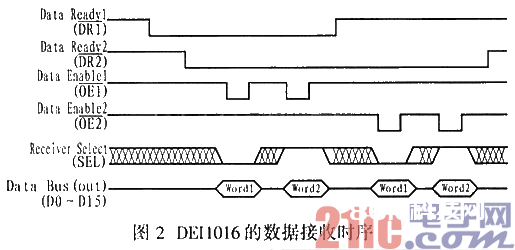

2 DEI1016的作业原理 DEI1016的引脚功用及特色曾经已有介绍,现仅对该器材的作业原理作以描绘。 2.1 DEI1016的复位及初始化 电路上电后,首先在MR引脚施加200μs的低电平脉冲以使DEI1016复位,然后把操控字写到16位数据总线上,这样,在LDCW引脚施加低电平便可把操控字写入到操控字寄存器,此后便可接纳和发送数据。 2.2 DEI1016的数据发送进程 DEI1016的数据发送时序如图1所示。发送数据时,首先应查询TXR引脚是否为高电平,若是高电平,标明发送存储器已空;此刻置ENTX引脚为低电平可中止发送数据,并把要发送的数据写到16位数据总线上。之后,若要发送数据字1,则置LD1为低,LD2为高;若发送数据字2,则置LD1为高,LD2为低此刻再查询TXR引脚是否为低电平,若为低电平,标明发送数据已装载到存储器中,此刻再置ENTX引脚为高电平即可发送数据。DEI1016的发送存储器最多可装载8个32位字长的数据,DEI1016选用的是先进先出的发送次序。 2.3 DEI1016的数据接纳进程 DEI1016的数据接纳时序如图2所示。当接纳器1接纳到数据后,体系会置DR1为低电平;而当接纳器2接纳到数据后,体系将置DR2为低电平。欲使接纳器1将接纳数据的字1送至16位数据总线上,应先置SEL为低电平,再置OE1为低电平且置OE2为高。然后再置SEL为高电平,便可将字2送至16位数据总线。要使接纳器2的数据送至16位数据总线上,则置OE2为低电平,OE1为高电平即可。 表1 74LS373功用表 输出操控OE 使能G 输入D 输出Q L H H H L H L L L L X Qo H X X Z 3 AT89C52与DEI1016的接口规划 AT89C52(U1)8位微控器与DEI1016的16位数据总线进行数据交换时,必须先运用锁存器来锁存数据。其接口电路框图见图3。发送数据时,U1先把要发送的数据分红低8位和高8位送出,并进入U3、U4锁存,此后再把16位数据一起送至DEI1016U2的数据总线上。U3、U4、U5、U6均选用74LS373芯片,它们的内部均由D锁存器和三态输出门组成,其功用表如表1所列。当OE为低电平,且G为高电平时,输出Q与输入D之间为直通方法。而当OE为高电平,且G由高电平跳变为低电平后,D端输入数据被D锁存器锁存,之后即便D端(P0口)输入数据再发生变化,也不会影响已锁存的数据。假如OE为低电平,体系将输出原先锁存的数据。为了锁存低8位数据,需要由U1的WR和地址选通信号Y7(由译码器U7译出)经或非门U8去操控U3的G端。实际上,只要U1在履行写操作时, WR和Y7才一起为低电平,而此刻低8位数据才干被U3暂时锁存。高8位数据的锁存与此相似M,U1的P3.4由高变低可翻开U3、U4的输出门,从而使U3、U4把数据送至U2的数据总线,当U1的P1.3或P1.4由高变低以把16位数据装入发送存储器后,P3.4会由低变高,此刻U3、U4输出为高阻抗状况,但不会影响U2的数据输出状况。其发送程序如下: mov dptr,#e000h mov a,#d1l ;取字1的低8位 movx @dptr,a ;把字1的低8位锁入U3 mov dptr,#c000h mov a,#d1h ;取字1的高8位 movx @dptr,a ;把字1的高8位锁入U4 clr p3.4 ;翻开U3、U4的输出 nop clr p1.3 ;字1数据装入DEI1016 nop setb p3.4 ;封闭U3、U4的输出 setb p1.3 mov dptr,#e000h mov a,#d2l ;取字2的低8位 movx @dptr,a ;把字2的低8位锁入U3 mov dptr,#c000h mov a,#d2h ;取字2的高8位 movx @dptr,a ;把字2的高8位锁入U3 clr p3.4 ;翻开U3、U4的输出 nop clr p1.4 ;字2数据装入DEI1016 nop setb p3.4 setb p1.4

用U1接纳数据,应将DR1、DR2及TXR经与门U13接至U1的INT0,在INT0口发生中止后,U1便履行读操作,并经过RD和Y5操控U14、U15以读入DR1、DR2及TXR的状况。U2接纳到数据或发送数据结束后,即向U1的INT0口请求中止,并在中止程序中判别DR1、DR2及TXR的状况。TXR为低标明发送结束,而DR1或DR2为低则标明已收到数据。此刻可置P1.2(SEL)为低电平,一起也置P1.0(接DEI1016的OE1)或P1.1 接DEI1016的OE2为低电平,以使字1的数据出现在数据总线上,而使P1.0、P1.1经U11异或后输出以使U5、U6的G端为高电平,从而把数据锁入U5、U6。因为RD别离与Y7、Y6相或后的输出是与U5、U6的OE门相连接的,因而,U1 履行读操作时,应先后翻开U5、U6的OE门来把数据读入。其接纳程序如下:(以接纳器1为例)。 clr p1.2 ;置DEI1016的SEL=0,读字1 clr p1.0 ;置DEI1016的/OE1=0 setb p1.1 ;置DEI1016的/OE2=1 nop mov dptr,#e000h movx a,@dptr ;把字1的低8位读入 mov 10h,a mov dptr,#c000h movx a,@dptr ;把字1的高8位读入 mov 11h,a setb p1.2 ;置DEI1016的SEL=1,读字2 nop mov dptr,#e000h movx a,@dptr ;把字2的低8位读入 mov 12h,a mov dptr,#c000h movx a,@dptr ;把字2的高8位读入 mov 13h,a setb p1.0 ;置DEI1016的/OE1=1 setb p1.1 ;置DEI1016的/OE2=1 setb p1.2 ;置DEI1016的SEL=1 图3 DEI1016的两路接纳或许发生一起接纳的现象。即在上述两路共用一个中止源时,假如某一路请求中止已进入接纳程序,那么另一路一起接纳的数据就或许被屏蔽。解决办法是:进入中止程序后,在接纳数据进程中再查询另一路DR的状况。当然,假如每路独自运用一个中止源,作用将会更好。 4 结束语 实际上,上述AT89C52与DEI1016的接口电路经改善也能够应用到其它16位数据总线接口的电路中,而假如用ISP器材代替锁存器及其门电路,还可大大减小电路板的面积。