跳频通讯作为扩频通讯的一种,具有抗搅扰、抗截获以及多址组网等长处,在现代军事通讯尤其是战术抗搅扰电台中取得了广泛的运用。近年来,跳频通讯技能在民用通讯体系中的运用也越来越广泛,例如GSM、无线局域网、Bluetooth等运用了跳频技能,矿井救援通讯体系运用了跳频通讯的组网才能应对灾变现场的杂乱环境,语音电台也常常运用跳频通讯来确保语音信号安全可靠地传输。

本文首要对跳频通讯体系抗搅扰功能进行理论剖析,运用Matlab/Simulink仿真东西建立跳频通讯体系模型,仿真取得体系抗全频带搅扰和抗盯梢式搅扰功能。接着规划并完成了一个跳频语音通讯体系,其依据FPGA和Silicon Labs公司的通用射频收发芯片Si4463。文中偏重描绘了跳频语音通讯体系全体规划架构,通用射频芯片Si4463的首要功能参数、外围电路以及芯片装备流程,并给出体系完成后的首要方针测验成果。本文规划的跳频语音通讯体系,能够满意杂乱环境下安全可靠的民用语音通讯需求;一起,体系选用一种简化的依据TOD的跳频同步计划,直接运用本地计数器替代准确时刻发生模块(例如GPS模块),下降跳频同步杂乱性,节省硬件资源和本钱。

1 跳频抗搅扰功能仿真剖析

跳频通讯的抗搅扰才能通常用跳频处理增益来表明,而关于不同的搅扰办法,跳频通讯体系的跳频处理增益也不同。

1)关于全频带搅扰来说,跳频处理增益为:

其间,Bs为单频点信号带宽,Bw为跳频信号总带宽。进步跳频信号总带宽并减小单频点信号带宽,能够有用进步抗全频带搅扰才能。

2)关于单频带搅扰来说,跳频处理增益为:

GFH=10lgN (2)

其间,N为跳一再点数。因而,添加跳一再点数,能够有用进步跳频通讯抗搅扰才能。

3)关于盯梢式搅扰,跳频处理增益为:

其间,TH为跳频驻留时刻,Tt为频率盯梢占用时刻。跳频驻留时刻越短,频率盯梢时刻越长,则跳频处理增益越大。因而,进步跳频通讯的跳速,能够有用进步抗搅扰才能。

1.1 抗全频带搅扰功能剖析

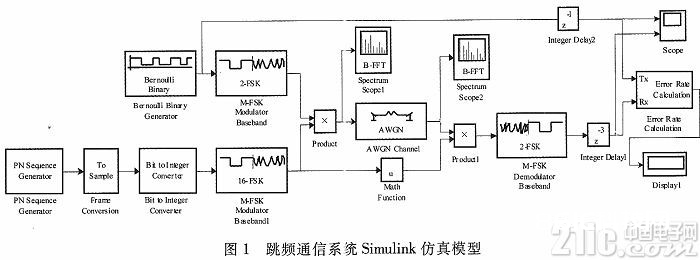

为了剖析跳频通讯体系抗搅扰才能,运用Matlab/Simulink仿真东西建立跳频通讯体系仿真模型(图1),要点仿真跳频体系处于全频带搅扰下的误码率和信道中信噪比的联系。

关于选用BFSK调制办法的跳频通讯体系施行全频带搅扰,其误码率为:

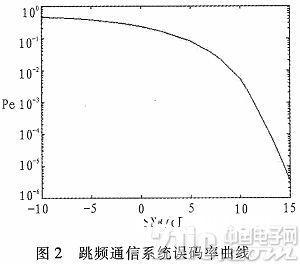

其间,Eb为信号每比特功率,No为白噪声功率谱密度,NJ为搅扰噪声功率谱密度。图2给出了全频带搅扰下跳频通讯体系的误码率曲线。

图2可见,在搅扰噪声功率较小,信噪比较大时,全频带噪声搅扰对跳频通讯体系的搅扰并不显着,在信噪比为15 dB时,体系误码率为10-6数量级,体系语音通讯根本不受影响。跟着信噪比的减小,当信噪比为0d B时,体系误码率上升到23%,通讯遭到严峻搅扰。关于全频带搅扰,因为搅扰噪声散布在很宽的带宽规模内,所以搅扰噪声功率谱密度一般较小。假定想对体系通讯完成显着搅扰作用,则信噪比至少在0 dB以下,这对全频带噪声搅扰功率要求很高,所以跳频通讯体系对全频带噪声搅扰能够起到明显的抗搅扰作用。

1.2 抗盯梢式搅扰功能剖析

关于盯梢式搅扰,能够经过进步跳速进步抗搅扰才能。

假定发射端到接纳端的间隔为d1,盯梢式搅扰源距发射端和接纳端分别为d2和d3,明显d1

其间,c为光速。

假定搅扰信号和有用信号的途径差为30 km,则△t=100μs。若跳频通讯体系跳速为10 000 hop/s,其跳隙时长为100μs,在同频搅扰来届时,通讯频率现已跳到下一个频点,此搅扰源对跳频体系根本无效。相同以美国的JTIDS(Joint Tactieal Information Distribution Sys tem)体系为例,其跳速最高可达76 923 hop/s,只需搅扰源和有用信号的途径差大于3.9 km,则盯梢式搅扰对其无效。

实践体系中,关于盯梢式搅扰源,其转发同频搅扰必定需求必定的呼应时刻,考虑该呼应时刻,跳频体系抗盯梢式搅扰作用更好。

2 依据TOD的跳频同步原理

2.1 依据TOD的跳频同步办法

因为跳频通讯的频率需求不断跳变,所以通讯两边怎么坚持同步是跳频体系最要害的问题。选用依据时刻信息(Time of Day,TOD)的跳频同步办法是依据准确时钟法、同步头法、自同步法提出的一种归纳的同步办法。TOD便是跳频体系的实时时钟信息,实时时钟信息包含年、月、日、时、分、秒、毫秒、微秒等。

依据TOD的跳频同步办法经过将带着有时刻信息的同步头置于跳频信号的最前面,接纳端从同步头中捕获到同步信息后,调整本地跳频序列发生器,从而使收发两边完成同步。收发两边的伪随机码和发生跳频图画的办法是共同的,不同的仅仅时刻信息TOD。TOD以每一跳的时刻为单位,因为收发端的时钟精度不可能共同,经过一段时刻后两者的TOD就会有差异。因而,发射端需求定时发送的同步信息,接纳端能够从同步信息中提取发射端的TOD,然后批改自己的TOD。这种办法同步时刻快,同步概率大,随机功能好,能够满意跳频通讯的各种要求。

2.2 一种简化的依据TOD的跳频同步办法

传统的依据TOD的跳频同步办法,需求专门的肯定准确时刻生成模块(例如GPS模块),用于发生TOD。

本文提出一种简化的跳频同步办法,直接经过体系内部的计数器取得相对时刻值作为TOD,下降体系跳频同步杂乱性,节省硬件资源和本钱。

体系发射端和接纳端均具有一个分级计数器,用于生本钱地TOD,经过反应移位寄存器生成频点,并构成跳频图画。分级计数器包含时钟计数器、时隙计数器和帧计数器。时钟计数器用于记载每个时隙内的时钟个数;时隙计数器依据时钟计数器的进位符号进行计数,记载每一帧内的时隙个数;帧计数器用于记载帧号,作为本地TOD值。

体系数据帧被划分为若干个时隙进行发送,包含1个同步时隙和若干个事务时隙。同步时隙数据包中寄存发射端TOD,事务时隙数据包中寄存需求传输的有用语音数据。同步时隙期间,接纳端接纳到来自发射端的TOD,对本地TOD进行校对,对分级计数器进行清零,并运用接纳到的TOD值作为反应移位寄存器的初始值。在事务时隙期间,发射端和接纳端经过各自的反应移位寄存器移位更新频点,确保收发两头的跳频图画共同,完成跳频同步。

3 跳频语音通讯体系规划与完成

3.1 体系整体结构

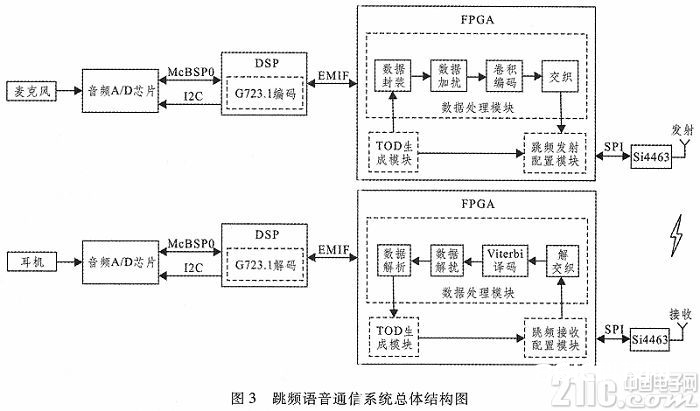

为完成跳频语音通讯,规划一种依据FPGA和Si4463的跳频语音通讯体系,图3给出了体系整体结构。

在发射端,首要经过麦克风输入语音信号,然后运用音频A/D芯片将模仿语音信号转化为数字信号,接着运用DSP对语音信号进行依据G723.1语音编码规范的编码,然后在FPGA中对数据依照帧结构进行组包、加扰、卷积编码、交错等一系列处理后经过射频芯片跳频发射出去。

在接纳端,将射频芯片接纳到的数据包先进行解交错、Viterbi译码宽和扰处理,然后依照帧结构将数据解析出来。语音数据包经过DSP进行G723.1语音解码,并经过音频D/A芯片转化为语音后经过耳机输出。

体系选用了一种简化的依据TOD的跳频同步办法,在发射端和接纳端,均经过FPGA中分级计数器生成TOD,完成跳频同步。

3.2 Si4463电路规划

体系运用Silicon Labs公司最新的高功能低功耗射频收发芯片Si4463,其首要功能参数如下:

1)频率规模:119~1 050 MHz;

2)接纳灵敏度:-126dBm@500bps,-106dBm@100kbps,-88dBm@1Mbps;

3)调制办法:(G)FSK、4(G)FSK、(G)MSK、OOK;

4)最大输出功率:20 dBm;

5)低功耗:13mA@RX,18mA@TX(10dBm);

6)数据速率:100 bps~1 Mbps;

7)供电电压:1.8~3.3 V。

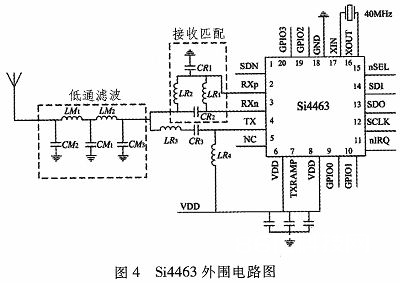

图4给出Si4463外围电路图。

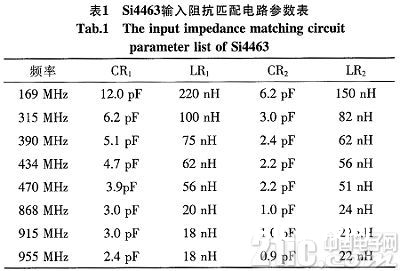

Si4463输入端在不同频率时出现不同的阻抗特性,为了下降输入驻波,需求运用匹配电路进行输入阻抗匹配。不同频率运用时匹配电路取值不同,实践运用能够运用矢量网络剖析仪进行阻抗特性测验并进行匹配,也能够参阅以下典型频率时阻抗匹配电路取值。

3.3 Si4463收发装备流程

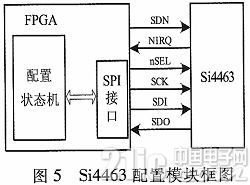

图3可见,数据经过FPGA处理今后经过Si4463选用跳频的办法发射出去。FPGA经过SPI接口对Si4463进行装备,运用一个有限状态机模仿装备指令的次序履行,图5给出了装备模块框图。

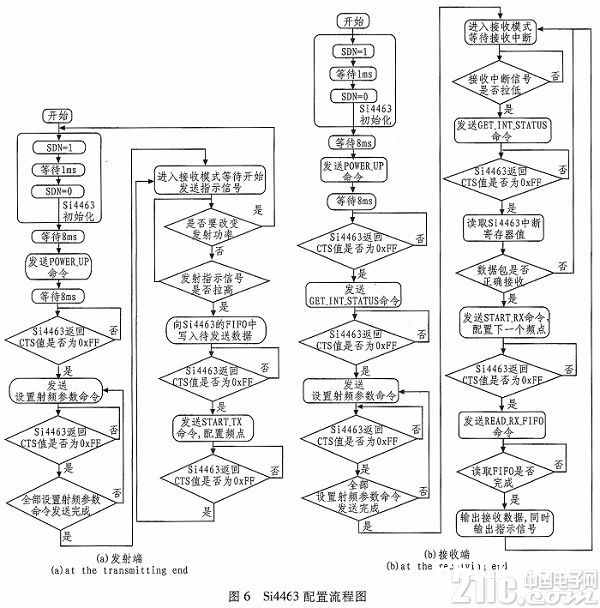

Si4463装备的详细流程见图6(a)、(b)所示。依照Si4463正常的作业流程,在接纳数据循环中,接纳端应该先将本次接纳到的数据包从Si4463的FIFO中读出,然后再对Si4463装备下一个频点。为了最大极限地进步跳速,在体系接纳到一包数据今后,先对Si4463装备下一个频点,然后再从Si4463的FIFO中读出这包数据。这样能够让体系读取本包数据和接纳下一包数据两个进程并行进行,缩短时刻,进步跳速。

3.4 体系测验成果

体系规划并完成后,进行了射一再谱、跳速及接纳灵敏度等功能方针测验,以及实践环境的语音通讯测验。实测取得体系首要参数如下:

1)作业频段:434 MHz,可装备;

2)调制办法:GFSK;

3)跳一再点数:16;

4)跳频总带宽:≥5 MHz;

5)跳频速率:≥150 hop/s;

6)接纳灵敏度:≤-104 dBm@75 kbps。

测验成果显现,所规划的跳频语音通讯体系功能方针与Si4463给出的方针适当;在实践环境测验中,语音通讯功能优越,体系抗于扰功能杰出,达到了体系规划各项方针要求,能够满意语音通讯需求。

4 结束语

本文规划了一个跳频语音通讯体系,选用了一种简化的依据TOD的跳频同步办法,并依据FPGA和Si4463完成。实测成果表明,该跳频语音通讯体系首要方针契合射频收发芯片Si4463功能参数,且在实践环境测验中,语音通讯功能优越,达到了体系规划方针。本文规划的跳频通讯语音体系能够满意杂乱电磁环境下的语音通讯需求。