美国国家仪器公司将工程的视觉处理移植到FPGA上完结,可获得更高的处理功用

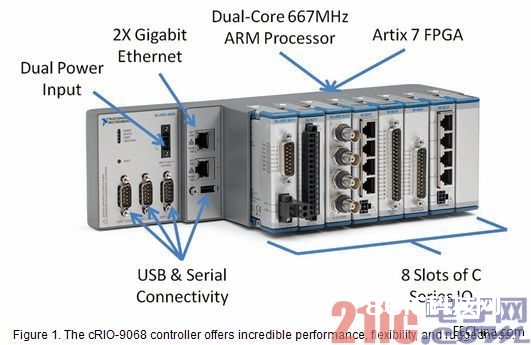

Jeff Bier 是嵌入式视觉联盟的创始人,本月在德克萨斯州奥斯汀举行的NI WEEK大会上,Jeff重视了国家仪器公司的一个演示体系,这个体系是国家仪器公司2014年度关于视觉辅佐方面的新产品。这个视觉辅佐组件的国家仪器公司视觉开发模块的一个部分,能够完结快速规划和一些机器视觉运用的开发。2014年期间,国家仪器公司现已将许多现已完结的视觉处理算法移植到了他自己的硬件渠道上,曾经这些视觉处理算法是运用FPGA硬件渠道完结的。国家仪器公司首要的渠道是CompactRIO-9068软件规划操控体系,这个体系是根据赛灵思Zynq Z-7000 ALL Programmable SoC而规划的。将视觉处理算法用Zynq SoC的可编程逻辑(FPGA)部分来完结不只提高了视觉处理的功用,而且能够让Zynq SoC上的两个ARM Cortex-A9处理器有更多的资源去处理其他使命。

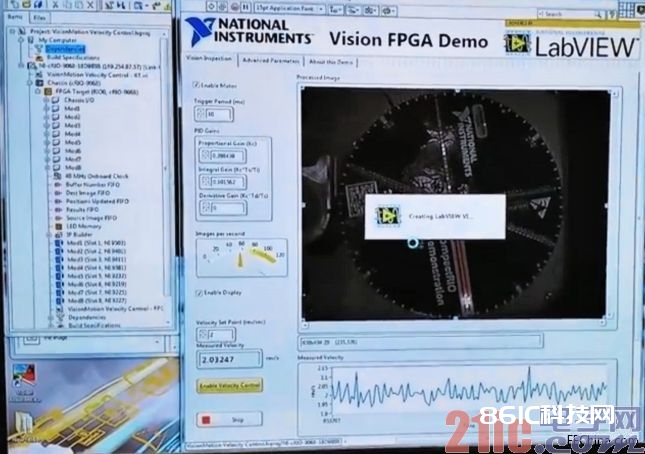

国家仪器公司在NI Week大会上演示的体系模块在Zynq SoC的FPGA部分完结了一个PID操控器 ,用于实时操控整个演示模块的步进电机。这样答应视觉处理进程契合操控算法,最大化的提高体系功用。

国家仪器公司的视觉辅佐组件能够生成规范的LabView代码,而且凭借了LabView FPGA 模块,是对Labview规划环境的扩展。LabVIEW软件的FPGA 模块运用Vivado规划软件作为基础,生成对FPGA芯片装备的文件。LabVIEW FPGA完结对图形化的LabVIEW代码,并将归纳结合下载到CompactRIO-9068操控体系的FPGA硬件部分,对FPGA进行装备。

开发人员凭借NI公司的视觉辅佐组件能够快速完结根据FPGA的视觉运用的原型规划,这个辅佐组件包含了视觉开发模块。视觉开发辅佐组件是一个根据可装备的原型开发工具,答应开发这迭代优化他们的图画处理算法,能够让他们看到设置参数的改动会对图画有什么样的影响。当算法工程完结后,视觉辅佐组件会主动生成一个完好的LabVIEW工程,包含虚拟的处理器内核,虚拟的FPGA部分和其他一些功用,例如在处理器和FPGA之间经过编解码完结图画的传输。经过视觉辅佐组件生成的FPGA代码相同进行了优化,支撑并行履行。开发人员能够运用LabVIEW FPGA 的IP Builder修正图画处理算法,这个功用是国家仪器公司(NI)的LabVIEW软件的FPGA 模块所支撑功用的一部分。

除了能够加快开发流程和代码生成功率,视觉辅佐组件也能够估量FPGA资源的运用情况,运用信息包含FPGA芯片资源(例如slice(分片),LUTs(查找表),DSPs和Block RAM)的运用百分比,它能够反映出整个图画处理运用的资源运用信息,也能够反映出每个独立的图画处理算法的芯片资源运用情况,能够让开发人员在整个运用的开发进程中了解每个使命模块的资源运用情况,完结资源的合理安排。