摘要:在医学超声成像算法中,最经典和最广泛运用的是推迟叠加算法。推迟叠加算法在超声成像、雷达信号发射、接纳以及天线信号波束构成等方面有着广泛的运用。尽管该算法并不是典型的性能需求型算法,但是在医学成像云核算服务的新需求下,需求进步该算法的核算速度,以战胜云核算中网络传输速度相对较慢的束缚。但是,以中央处理器作为首要核算资源的传统云核算结构无法满意医学超声图画快速生成的性能需求,因而,本文中运用以现场可编程逻辑门阵列作为异构加快资源的SuperVessel云渠道作为并行推迟叠加算法的完结渠道。当包括现场可编程逻辑门阵列和中央处理器之间的数据传输时刻在内时,SuperVessel云渠道上该算法异构完结的运转速度相较于中央处理器中该算法的运转速度进步了约22倍。

导言

推迟叠加算法是医学超声成像算法中最经典和最广泛运用的根本算法,在很多运用场景中有着广泛的运用,例如医学超声成像[1]、雷达信号的发射和接纳[2]以及天线信号波束构成[3]等。一起,该算法能够在很多不同的设备中完结,例如在临床和便携嵌入式医学超声实时成像设备中均有推迟叠加算法的完结。但是,当咱们考虑医学成像云核算服务的全新运用场景时,传统核算设备的核算速度并不能满意实时成像的核算需求。因而,有必要研制更快的、更有用的推迟叠加算法云完结。

传统的推迟叠加算法完结一般是选用依据中央处理器结构的串行核算形式完结。关于某些运用来说,中央处理器的核算速度能够满意其核算需求,但是关于医学成像云服务运用来说,中央处理器的核算速度仍是相对太慢。另一方面,运用现场可编程逻辑门阵列(Field-Programmable Gate Array,FPGA)能够满意并行完结的核算需求,而SuperVessel渠道正是第一个将FPGA加快融入到云核算中的核算渠道,因而,适合在该渠道上完结和评测并行推迟叠加算法。

本文将详细描绘SuperVessel云渠道[4]上运用FPGA加快的并行推迟叠加算法的规划和试验评测。

1 推迟叠加算法及其并行完结计划

1.1 推迟叠加算法

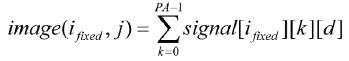

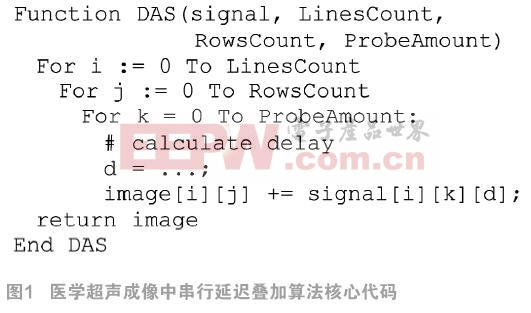

图1中的代码为医学超声成像中串行推迟叠加算法的中心代码。在该算法中,首要核算接纳到的回声超声信号的推迟量,进而将推迟后的回声信号叠加,得到增强的回声信号输出,即超声成像图画中一个像素点的亮度值。

推迟叠加算法包括三个循环,如图1中所示。该算法的时刻杂乱度为:

![]() (1)

(1)

其间变量LC(Line Count)表明输出图画中笔直的图画线条数,变量RC(Rows Count)表明输出图画中的行数,变量PA(Probe Amount)表明接纳回声超声信号的探头阵元数量。

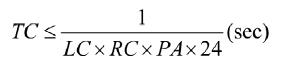

在本文的规划和试验中,LC设定为64,RC设定为1024,PA设定为64,所以每生成一幅超声图画需求核算4194304次推迟量核算和叠加核算。此外,在实时成像的情况下,要求构成流通的实时成像视频需求每秒24帧图画的帧率。因而,界说TC为上述每一次推迟量核算和叠加核算共需求耗费的时刻,则:

![]() (2)

(2)

对上式进行移项,可得:

(3)

(3)

在本文的规划和试验中,为了完结实时成像,依据公式(3)演算出TC的最大值为9.93×10-9秒。此外,跟着输入数据集的增大,实时成像的完结难度也相应进步,因而,需求考虑并行完结计划。

1.2 推迟叠加算法的并行完结

如图1所示,串行推迟叠加算法的中心代码中,中心操作是对推迟后输入数据的叠加。针关于终究生成图画中的一个特定像素点(i, j),存在PA次输入数据信号的叠加,叠加的公式如下:

![]() (4)

(4)

其间,i、j和k别离是LC、RC和PA的累加变量,而d是推迟量的数值,能够经过特定i、j和k变量的相关核算得到。当变量i为一个特定值ifixed时,终究图画中第ifixed列上像素点的亮度值能够经过如下公式核算:

(5)

(5)

经过对推迟叠加算法进行剖析,得出核算不同图画线上的image(ifixed, j)时并不存在相互间的数据依靠。因而,推迟叠加算法的核算进程能够并行化完结。

2 SuperVessel云渠道上的算法完结

本文运用SuperVessel云渠道完结的并行推迟叠加算法需求满意以下核算需求:1、在一个时钟周期内核算特定像素点image(i, j)的值;2、完结满意准确的浮点数核算;3、FPGA上全流水线化核算。

本文运用CAPI FPGA完结并行推迟叠加算法的规划框图如图2所示。该规划包括五个首要部分:输入数据别离器、RowsCount循环生成器、推迟信号挑选器、叠加器和数据输出控制器。以下是这五个部分规划原理和完结形式的详细描绘:

输入数据别离器: CAPI传输总线的带宽是256位,而每一个推迟信号挑选器仅需求32位的带宽,以供传输规范的单精度浮点数。由图2能够看出该规划中包括64个推迟信号挑选器,因而,需求将CAPI总线的256位输入数据别离,并且规划好输入数据读取的次序。输入数据读取进程的规划如下:

第一步:在T时钟周期内,第0个至第7个推迟信号挑选器读取一个CAPI输入信号数据;在(T+1)时钟周期内,第8个至第15个推迟信号挑选器读取下一个CAPI输入信号数据;以此类推,直到在(T+7)时钟周期内,第56个至第63个推迟信号挑选器读取下一个CAPI输入信号数据。

第二步:重复第一步所描绘的进程,直到生成一幅图画中某一列像素点所需求的一切输入信号数据读取完毕。

第三步:当图画中某一列的一切像素点数值均核算完结,则回到第一步读取生成图画中下一列像素点所需求的输入信号数据进程。

RowsCount循环生成器:当图画中某一列像素点核算所需求的一切输入信号数据读取完毕时,循环生成器将开端生成RC循环变量j的值。变量j的初始值为0,在每一个时钟周期内自增1,直到最大值1023。

推迟信号挑选器:推迟信号挑选器将核算对应像素点不同数据通道上的推迟量,并挑选对应的输入信号数据。完结部分包括了一个推迟量核算器和一个BRAM存储器,BRAM存储器用于存储某个数据输入接纳通道,接纳通道接纳到的输入信号数据。

叠加器:在并行推迟叠加算法的CAPI FPGA规划中共有64个推迟信号挑选器,而这64个推迟信号挑选器的输出值之和,即为image(i, j)的终究成果。核算两个推迟信号挑选器输出值之和需求一个加法器,对应地,核算64个推迟信号挑选器输出值之和需求63个加法器。为了使加法器规划流水线化,叠加器模块将加法器分为6个阶段层次,每层别离运用32、16、8、4、2、1个加法器。

输出数据控制器:因为CAPI总线供给的带宽是256位,而本文所描绘的规划每一个时钟周期内输出数据是一个32位的浮点数。因而,输出的数据能够先存放于FPGA中,每8个时钟周期经过CAPI总线接口向CPU输出一次数据。

除了上述的五个首要完结模块外,本规划计划中也运用了下面两个规划模块:

浮点数核算单元:本规划运用了Xilinx Vivado软件中供给的浮点数IP核作为浮点数核算单元模块。该类IP核遵从了IEEE-754的规范,因而,本文规划中的浮点数核算成果相较于CPU完结的浮点数核算成果而言,差错很小。另一方面,该类IP核是全流水线化的,这也进一步进步了规划的吞吐量。

状况控制器:在图画像素点数值核算的进程中有两个状况阶段:第一个阶段是输入信号数据的读取进程,第二个阶段是推迟量的核算和推迟后输入信号数据的叠加进程。状况控制器包括一个状况符号变量,以指示当时核算的状况阶段。当第一阶段的输入信号数据读取进程完毕时,BRAM的写入地址waddr的值将为2047。因而,可界说waddr==2047为第二阶段开端的符号信号。当第二阶段完毕时,将waddr的值设为0,则将触发第一阶段重新开端,进行下一轮核算。此外,当图画中一切的像素点核算完结时,输出图画的像素点数目为65536 。所以,可界说该数值为图画核算完结的标志变量,标志着算法核算完毕。

3 试验和评测成果评论

3.1 SuperVessel渠道上运用CAPI FPGA加快器的流程

在SuperVessel渠道上运用CAPI FPGA加快器来加快算法运用,需求履行以下进程:

1、运用Xilinx Vivado软件规划FPGA加快器中心模块;

2、在本地的x86机器上集成FPGA加快器中心模块和CAPI仿真结构进行仿真验证;

3、在本地机器上编译FPGA加快器中心模块和CAPI加快结构构成的加快器包,并生成对应的bitstream文件;

4、将加快器bitstream文件上传到SuperVessel云渠道上;

5、在SuperVessel云渠道上请求虚拟机资源,并相关对应的加快器bitstream文件,然后发动虚拟机运转加快器。

别的需求留意以下两点:

VPN网络:SuperVessel云渠道上请求的虚拟机资源没有对应的可直接拜访的公网IP,需求运用对应的VPN网络。运用的VPN网络在Windows、Linux、MacOS等干流操作系统中均有对应的软件支撑。

内存占用:编译进程3中所述的加快器包时需求很多本地机器内存,尤其在归纳和布线的阶段;并且CAPI FPGA加快器规划越杂乱,本地机器内存占用量就越大。在本文的试验评测中观察到,编译阶段的内存占用量最高达到了14GB。内存不足将导致编译失利,因而需求依据CAPI FPGA规划的巨细装备满意的内存资源。

3.2 仿真数据生成

本文的试验进程中为了测验运用CAPI FPGA并行加快的推迟叠加算法,运用Field II医学超声信号模拟器[5]仿真了医学超声回波输入数据。本文的医学超声图画回波输入数据仿真了128个阵元的超声探头,探头距离为0.3048mm,选用5 kHz的脉冲发射频率和40 MHz的回波接纳采样频率。此外,超声图画的成像场景仿真了线形点阵列作为成像目标的散射源。

3.3 试验成果评论

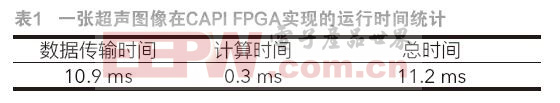

在试验中,经过网络将10份医学超声图画的输入信号数据载入SuperVessel云渠道,其间每份图画的输入信号数据对应于一张超声图画。在云渠道上经过CAPI加快架构供给的API,调用FPGA加快器,将数据从云渠道上CPU对应的DDR内存中传输到FPGA中的BRAM里;完结图画像素点数值核算后再将数据传回DDR内存。实测从数据传输开端到数据传输完毕的时刻,得到并行推迟叠加算法云核算运用运转的总时刻。并行推迟叠加算法在FPGA上的核算时刻经过统核算法履行的时钟周期来确认,因而,还可推算出数据传输所耗费的时刻。经过屡次试验求得各项时刻参数的均匀值,如表1所示。

与此一起,运用SuperVessel云渠道上CPU核算取得相同的10张医学超声图画,其每张图画核算的均匀耗时为246 ms。由此核算可得,本文规划的CAPI FPGA并行推迟叠加算法完结的加快比达到了约22倍。此外,经过试验推导出该规划的TC数值为秒,满意1.1末节提出的实时成像要求。

4 定论和展望

本文描绘了在SuperVessel云渠道上,规划和评测依据CAPI FPGA加快器技能的并行推迟叠加算法。试验评测成果表明,SuperVessel云渠道上依据CAPI FPGA加快器的并行推迟叠加算法的运转速度相较于运用CPU核算的推迟叠加算法的运转速度进步了约22倍,该速度能够满意医学成像云核算服务的需求。

现在,本文规划中的超声回波信号接纳通道数为64。通道数越大时,得到的图画越明晰,所以咱们运用相同的计划规划了96通道和128通道的成像计划,但因为资源约束的原因未能成功运转。咱们将持续优化当时的规划,下降资源占用并选用多片FPGA规划计划,进一步进步通道数量和数据处理才能。

别的,SuperVessel云渠道供给的CAPI加快技能能够运用于其他核算密集型算法加快,尤其是输入输出数据量小,而时刻杂乱度高的算法。咱们将进一步把其他医学超声成像算法规划到SuperVessel云渠道上完结。

参考文献:

[1] G. Matrone, A.S. Savoia, G. Caliano, and G. Magenes, “ The Delay Multiply and SumBeamforming Algorithm in Ultrasound B-Mode Medical Imaging,” IEEE Transactions onMedical Imaging, 2015, 34, (4), pp. 940-949.

[2] T. Sakamoto, T. Sato, P.J. Aubry, and A.G. Yarovoy, “Ultra-Wideband Radar ImagingUsing a Hybrid of Kirchhoff Migration and Stolt F-K Migration With an Inverse BoundaryScattering Transform,” IEEE Transactions on Antennas and Propagation, 2015, 63, (8),pp. 3502-3512.

[3] S.S. Tiang, M. Sadoon, T.F. Zanoon, M.F. Ain, and M.Z. Abdullah, “Radar sensingfeaturing biconical antenna and enhanced delay and sum algorithm for early stage breastcancer detection,” Progress In Electromagnetics Research B, 2013, 46, pp. 299-316.

[4] Y. Lin, and L. Shao, “SuperVessel: The Open Cloud Service for Open-POWER,” White paper, IBM corporation, 2015.

[5] J.A. Jensen, “Ultrasound fields from triangular apertures,” Journal of the Acoustical Society of America, 1996, 100, (4), pp. 2049-2056.

本文来源于我国科技期刊《电子产品世界》2016年第9期第41页,欢迎您写论文时引证,并注明出处。