FPGA/EPLD的自上而下(Top-Down)规划办法:

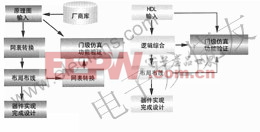

传统的规划手法是选用原理图输入的办法进行的,如图1所示。经过调用FPGA/EPLD厂商所供给的相应物理元件库,在电路原理图中制作所规划的体系,然后经过网表转化发生某一特定FPGA/EPLD厂商布局布线器所需网表,经过布局布线,完结规划。原理图制作完结后可选用门级仿真器进行功用验证。

图1:传统的规划手法与Top-Down规划东西的比较

但是,工程师的开端规划思维不是一开端就考虑选用某一FPGA/EPLD厂商的某一特定类型器材,而是从功用描绘开端的。规划工程师首先要考虑规划出能完结某一详细功用、满意自己产品体系规划要求的某一功用模块,运用某种办法(如HDL硬件描绘言语)把功用描绘出来,经过功用仿真(HDL仿真器)以验证规划思路的正确性。当所规划功用满意需求时,再考虑以何种办法(即逻辑归纳进程)完结所需求的规划,并能直接运用功用界说的描绘。实际上这便是自顶而下规划办法。

与传统电原理图输入规划办法比较,Top-Down规划办法详细有以下长处:

1、彻底符合规划人员的规划思路,从功用描绘开端,到物理完结的完结。

2、功用规划可彻底独立于物理完结

在选用传统的电原理输入办法时,FPGA/EPLD器材的选用遭到器材库的约束。因为不同厂商FPGA/EPLD的结构彻底不同,乃至同一厂商不同系列的产品也存在结构上的不同,因而,在规划一开端,工程师的规划思路就遭到终究所选用器材的束缚,大大约束了规划师的思路和器材挑选的灵活性。而选用Top-Down规划办法,功用输入选用国际标准的HDL输入办法,HDL可不含有任何器材的物理信息,因而工程师能够有更多的空间去集中精力进行功用描绘,规划师能够在规划进程的最终阶段恣意挑选或更改物理器材。

3、规划可再运用

规划效果彻底能够以一种知识产权(IP-Intellectual Property)的办法作为规划师或规划单位的规划效果,应用于不同的产品规划中,做到效果的再运用。

4、易于规划的更改

规划工程师可在极短的时刻内修正规划,对各种FPGA/EPLD结构进行规划效果规划(门耗费)和速度(时序)的比较,挑选最优计划。

5、规划、处理大规划、杂乱电路

现在的FPGA/EPLD器材正向高集成度、深亚微米工艺开展。为规划体系的小型化,低功耗、高可靠性等供给了集成的手法。规划低于一万门左右的电路,Top-Down规划办法具有很大的协助,而规划更大规划的电路,Top-Down规划办法则是必不可少的手法。

6、规划周期缩短,生产率大大提高,产品上市时刻提早,功用明显提高,产品竞争力加强。据统计,选用Top-Down规划办法的生产率可到达传统规划办法的2到4倍。

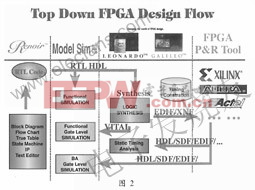

Top-Down规划流程如图2所示,其中心是选用HDL言语进行功用描绘,由逻辑归纳(Logic Synthesis)把行为(功用)描绘转化成某一特定FPGA/EPLD的工艺网表,送到厂商的布局布线器完结物理完结。在规划进程的每一个环节,仿真器的功用验证和门级仿真技术确保规划功用和时序的正确性。

FPGA/EPLD To p-Down 规划东西的黄金组合

Mentor Graphics公司供给一整套根据UNIX渠道和Windows 95/NT 渠道的FPGA/EPLD Top-Down规划东西:Renoir/ModelSim 和Exemplar,如图2所示。两种渠道的东西具有相同的用户界面,并确保数据库的彻底一致。现在,在FPGA/EPLD Top-Down规划办法全球市场上,Mentor已具有42%的市场份额,远远领先于其他任何一个厂家。

选用Top-Down规划办法进行FPGA/EPLD规划,其规划效果的好坏与否取决于三个重要的要素:描绘手法(即HDL言语)、规划办法(Style)和规划东西。描绘手法是根底,规划办法需求工程经历,而规划东西则是Top-Down规划的要害。一套完好、强壮、功用杰出的规划东西,可协助规划工工程师最大极限的发挥其规划能力。