参考资料:xilinx大学方案

试验渠道:ZYBO开发板

本次试验要做的是一个根据FPGA的简略图画处理程序, 共完成两个功用:

1.输出一个灰度图画的直方图。

2.将一个曝光缺乏的图画进行处理,使其比照度更大。

一、Vivado HLS 部分

首要咱们用Vivado HLS来编写FPGA图画处理所用的IP核。

1.制作直方图

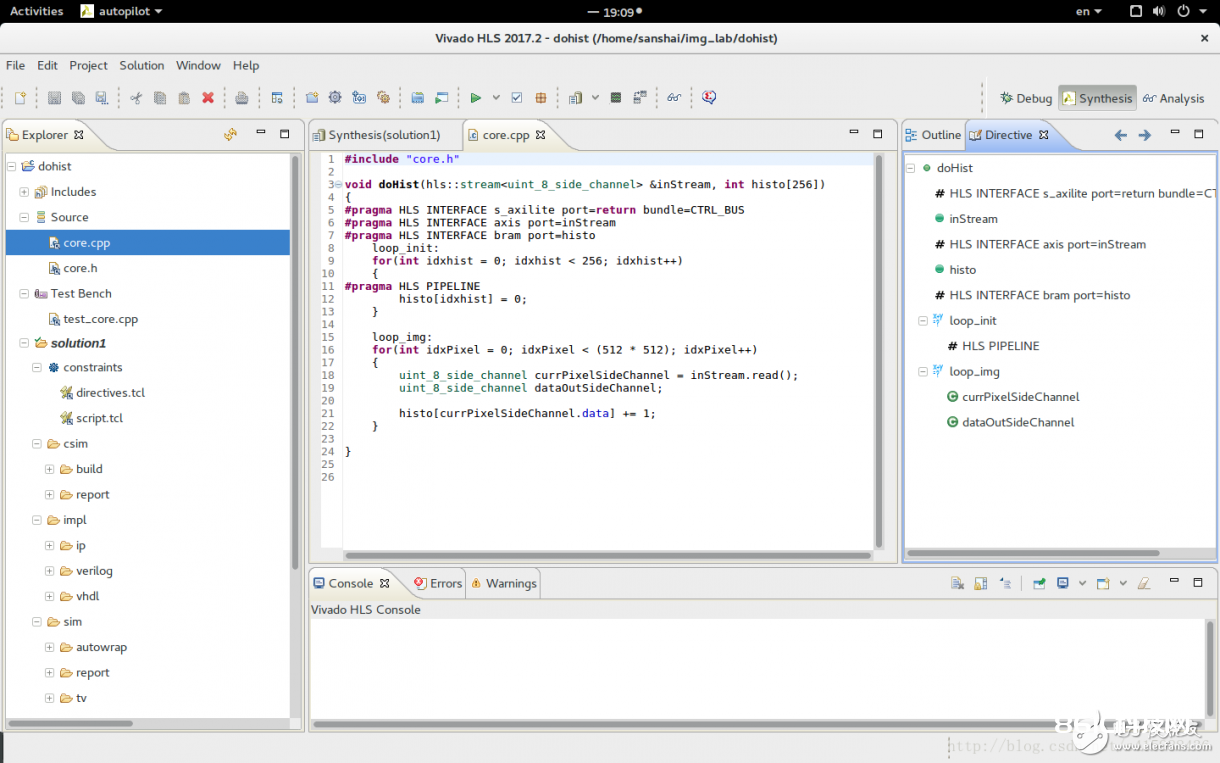

1.首要编写相应的C/C++言语程序,加入到Vivado HLS工程中,再编写相应的testbench代码进行编译测验。

代码很简略我们看一下就理解了。

注意到右侧DirecTIve窗口中的优化部分,别离表明doHist的输出接口运用AXI4-lite传输协议,inStream图画输入接口选用AXI4协议,输入数组histo存入bram中,loop_init循环进行翻开。

2.点击Run C SimulaTIon进行对C/C++源文件进行编译测验。

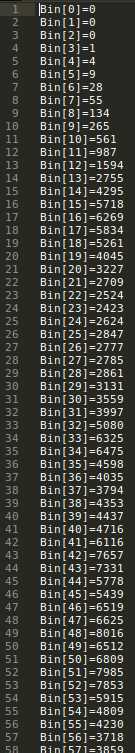

输出的部分直方图文本文件

3.将testbench输出的直方图文本与MATLAB中的直方图文件进行比照验证算法无误后,点击Run C/RTL CosimulaTIon来进行协同验证。

4.验证经过后点击Export RTL生成ip核。

如上过程所示,制作直方图的IP核现已生成成功。

2.调理比照度

过程如上所示,接口部分也相同运用AXI4协议,作用如下。

处理前

处理后

二、Vivado 归纳部分

1.将IP核布置到FPGA

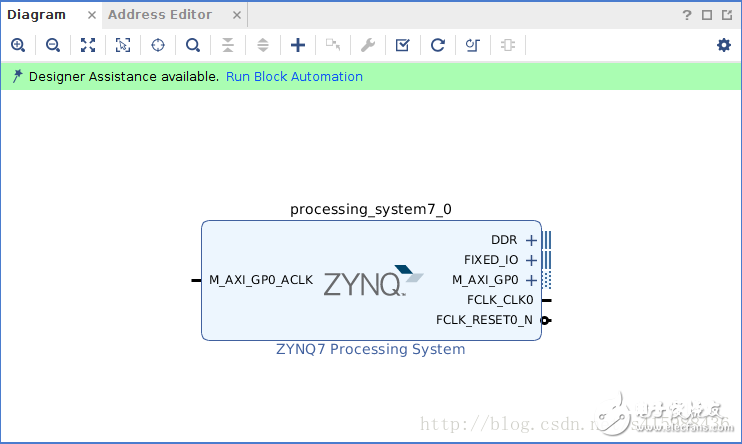

翻开Vivado界面,并树立工程,随后创立Block Design。

在Block Design界面首要需求增加zynq7 processing system,点击ADD IP查找ZYNQ增加IP核。该IP核是体系所供给的衔接ARM与FPGA的IP核,概况见: https://www.xilinx.com/products/intellectual-property/processing_system7.。.

随后点击Run Block AutomaTIon进行主动装备。

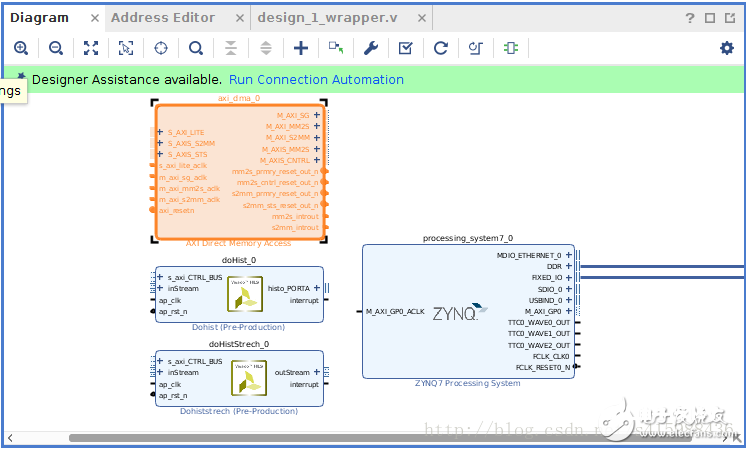

将之前HLS所生成的两个IP核导入工程中,相同的过程将doHist、doHistStrech和AXI DMA增加到diagram中。

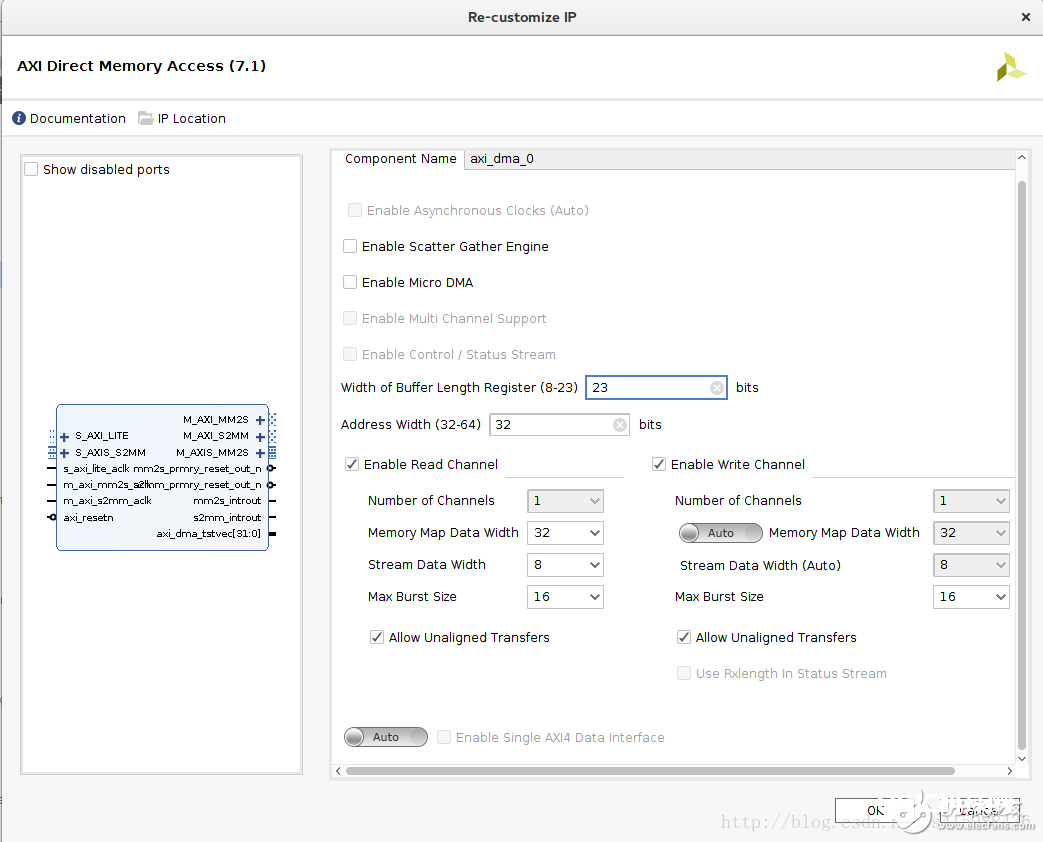

双击AXI DMA进行对IP核的装备,装备状况如图所示。

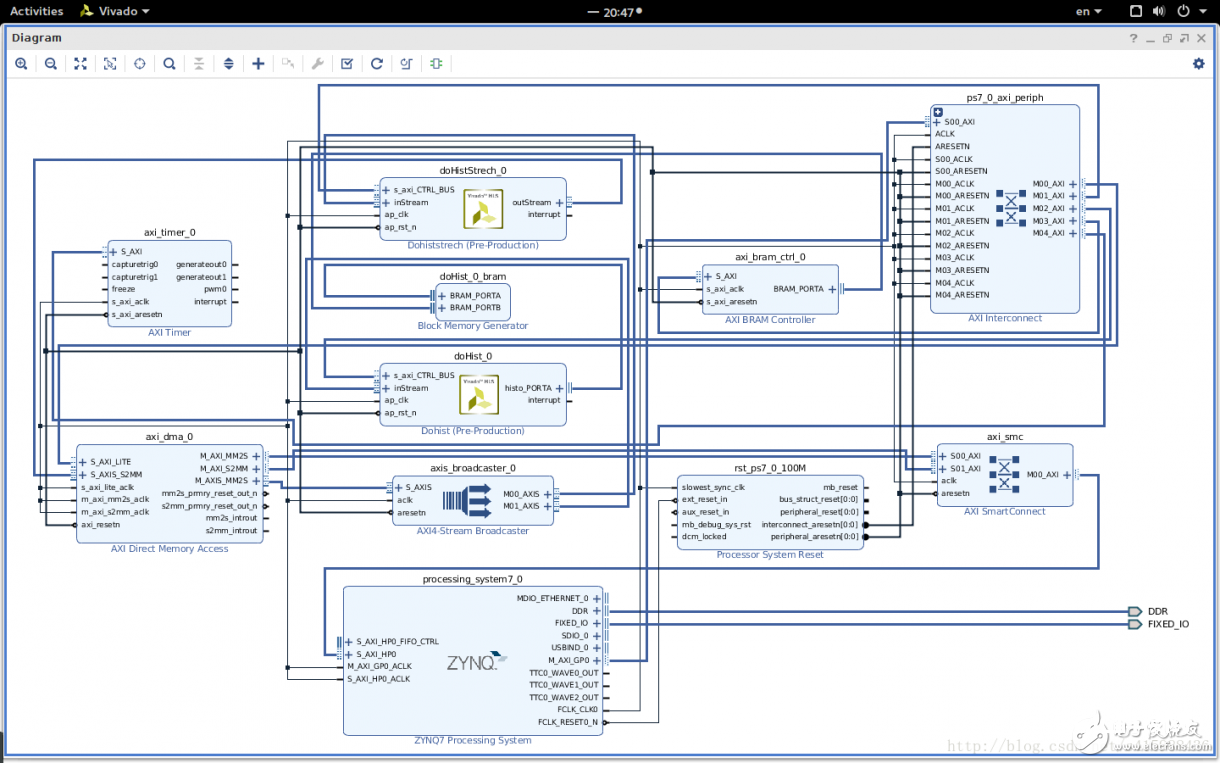

能够运用Run Connection Automation 来主动衔接。完成后的作用图如下,短少的ip核能够依照下图来增加。

完成后点击Validate Design进行验证。

随后就能够生成bitstream,下载到FPGA。

2.运用逻辑分析仪进行Debug

三、使用ARM来测验FPGA的加快作用

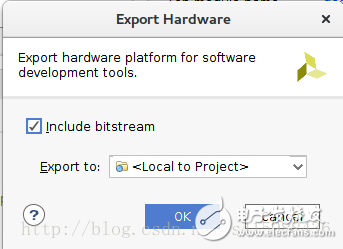

1.下载完成后点击File-》Export-》Export Hardware,弹出对话框

勾选include bitstream然后点击OK。

2.点击File-》Launch SDK发动SDK

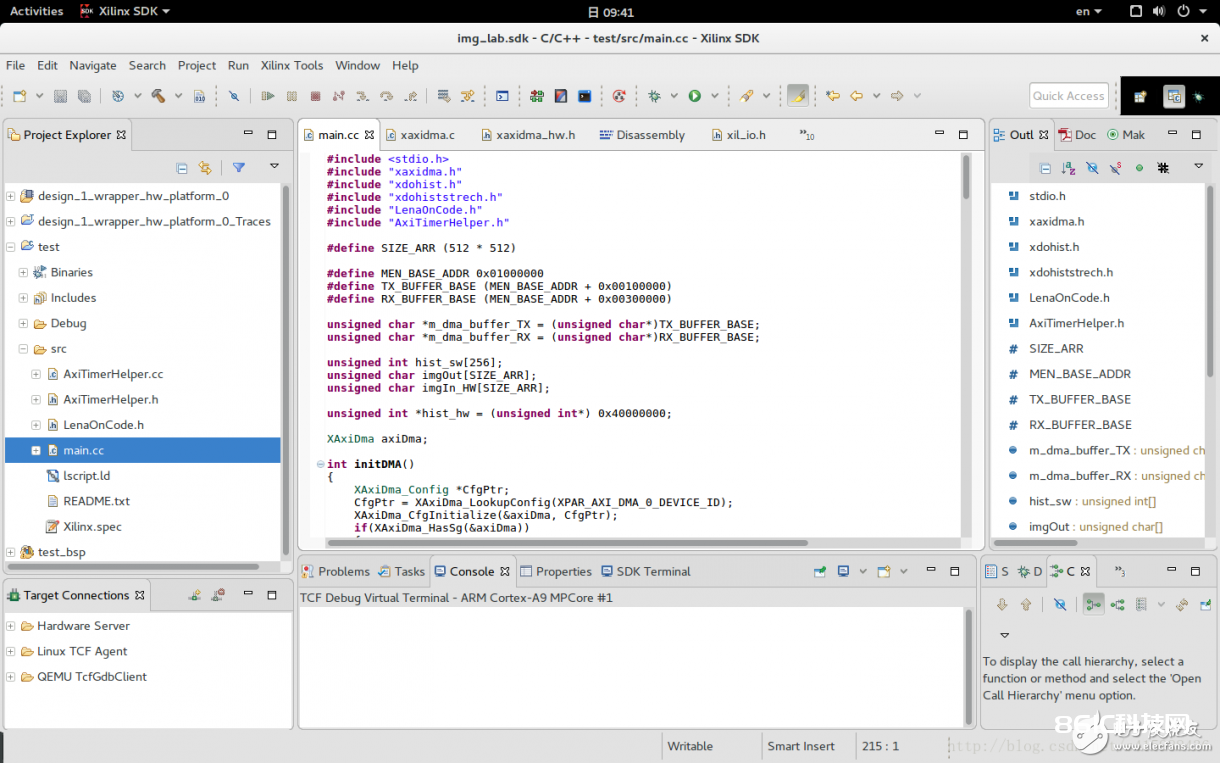

3.SDK开发环境如下,首要用于对ARM的开发,在之前生成ip核的时分会生成对应的驱动函数。

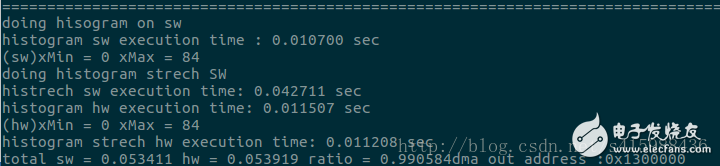

4.试验成果如下图所示