一、 时钟及锁相环

ADSP-BF531处理器运用来自外部晶体的正弦输入,或经过缓冲整形的外部时钟。假如运用外部时钟,该时钟信号应是TTL兼容信号,而且正常运转时,此时钟不能中止、改动、或低于指定的频率。此外部时钟应连到DSP的CLKIN引脚,且XTAL引脚有必要悬空。

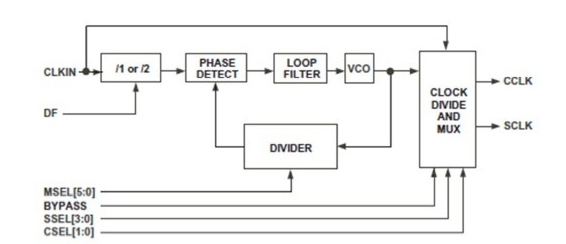

由于ADSP-BF531处理器有片内振动电路,所以也能够运用外部晶振。外部晶振应当连接到CLKIN和XTAL引脚,并与两个电容相连。电容值取决于晶振的类型,应当由晶振厂商供给。内核时钟(CCLK)和体系外设时钟(SCLK)可由输入时钟(CLKIN)信号取得,如图5-1所示。用户经过设置PLL_CTL中的倍频因子,可使片上PLL倍频CLKIN信号, CLKIN与倍频因子的乘积为PLL输出(VCO)的中心时钟,内核时钟(CCLK)和体系外设时钟(SCLK)便是由VCO发生。

图5-1 PLL 结构框图

用户能够经过四个MMR寄存器来操作或许读取PLL的状况。分别为分频寄存器(PLL_DIV),PLL操控寄存器(PLL_CTL),PLL状况寄存器(PLL_STAT)和PLL确定计数寄存器(PLL_LOCKCNT)。四个寄存器都是16位的,拜访时分需求留意对齐问题。

表5-1 PLL_DIV(地址:0XFFC0 0004 复位值0x0005)

| 位 | 称号 | 描绘 |

| 15:6 | – | 未用 |

| 5:4 | CSEL |

内核时钟挑选 00:CCLK=VCO/1; 01:CCLK=VCO/2; 10:CCLK=VCO/4; 11:CCLK=VCO/8。 |

| 3:0 | SSEL |

体系时钟挑选 0000:保存 1~15:SCLK= VCO / X |

表5-2 PLL_CTL(地址:0XFFC0 0000 复位值0x1400)

| 位 | 称号 | 描绘 |

| 15 | SPORT_HYS | 增加250mV滞后电压到SPORT 输入脚 |

| 14:9 | MSEL |

VCO倍频因子 0:64倍频 N=1~63:N倍频 |

| 8 | BYPASS |

越过PLL 0:不越过PLL(PLL有用) 1:越过 PLL |

| 7 | OUT_DELAY |

输出推迟 0:输出不推迟 1:PLL 到外部时钟输出,增加200ps的推迟 |

| 6 | IN_DELAY | 输入推迟 |

| 5 | PDWM |

掉电形式 0:一切内部时钟掉电 1:一切内部时钟敞开 |

| 4 | – | 未用 |

| 3 | STOPCK |

内核时钟中止 0:内核时钟正常运转 1:内核时钟中止 |

| 2 | – | 未用 |

| 1 | PLL_OFF |

PLL 电源操控 0:敞开PLL 电源 1:关断PLL 电源 |

| 0 | DF |

输入时钟二分频使能 0:输入时钟直连续PLL; 1:输入时钟二分频后连PLL。 |

表5-3 PLL_STAT(地址:0XFFC0 000C 复位值0x00A2 只读)

| 位 | 名 称 | 描 述 |

| 15:8 | – | 未运用 |

| 7 | VSTAT |

电压调理器指示 0:电压调理器未到达编程电压 1:电压调理器到达了编程电压 |

| 6 | CORE_IDLE | 内核中止状况 |

| 5 | PLL_LOCKED | 锁相环锁住 |

| 4 | SLEEP | 休眠 |

| 3 | DEEP_SLEEP | 深度休眠 |

| 2 | ACTIVE_PLLDISABLED | 激活形式,PLL制止 |

| 1 | FULL_ON | 一切均使能 |

| 0 | ACTIVE_PLLENABLED | 激活形式,PLL使能 |

当用户改动锁相环输出频率时,锁相环需求一段过渡时刻,来安稳到新的输出频率,PLL_LOCKCNT寄存器所界说的时钟计数便是设置新的时钟频率后,锁相环确定需求的周期数。

二、 电源办理

1. 动态电源办理操控器

ADSP-BF531的动态电源办理操控器(DPMC)与PLL结合,运用户能够动态地操控处理器的功用和功耗。用户能够使用DPMC供给下面的功用,对功用和功耗进行操控。

多种运转形式——ADSP-BF531有4种不同的运转形式,每个形式的功用和功耗都不同;

外设时钟——用户能够操控外设时钟的关断和接通,当一个外设处于闲暇或许未被运用时,能够节省功耗;

电压操控——ADSP-BF531供给一个片上电压调理器,使用buck技能,它能够操作Blackfin处理器内核的内部电压,然后进一步下降功耗。

2. 运转形式

ADSP-BF531有4种运转形式,每种形式有不同的功用/功耗特性,此外,动态功率办理有动态地改动处理器内核供电电压的操控功用,进一步下降功耗。操控每一个ADSP-BF531处理器外设的时钟也能下降功耗,表5-4总结了各种形式的运转特性。

表5-4 运转形式

| 运转形式 | 省电 | PLL状况 | PLL旁路 | CCLK | SCLK | 答应DMA拜访 |

| 全速 | 无 | 使能 | 否 | 使能 | 使能 | L1 |

| 活动 | 中 | 使能 | 是 | 使能 | 使能 | L1 |

| 休眠 | 高 | 使能 | 否 | 制止 | 使能 | |

| 深度休眠 | 最大 | 制止 | 制止 | 制止 |

(1) 全速形式

全速形式是Blackfin的最高功用形式。在该形式中,PLL被万能而且不被旁路,该形式是Blackfin正常执行时的状况,处理器和一切被使能的外设以全速运转。在该形式下,输入时钟(CLKIN)对内核时钟(CCLK)的频率比不能被改动。DMA存取可用于L1存储器,处理器能够从全速形式切换到活动、休眠或深度休眠形式。

(2) 活动形式

在此形式下,PLL被使能,但被旁路。由于PLL被旁路,处理器内核时钟(CCLK)和体系时钟(SCLK)运转于输入时钟(CLKIN)频率下。在此形式下,CLKIN到CCLK倍频可变,直到进入全速运转形式。经过适当地装备L1存储器,能够进行DMA拜访。

在激活形式下,经过PLL操控寄存器(PLL_CTL)能够制止PLL。假如被制止,在转换到全速或休眠形式前有必要被使能。

(3) 休眠形式

休眠运转形式经过封闭处理器内核(CCLK)的时钟来下降功耗,可是PLL和体系时钟(SCLK)仍在运转。一般经过外部事情或RTC活动来唤醒处理器。此形式下唤醒的呈现将会使处理器查看PLL操控寄存器(PLL_CTL)中旁路位(BYPASS)的值。假如旁路位被封闭,处理器将切换到全速运转形式。假如旁路位使能,处理器将切换到活动运转形式。

休眠形式时,体系DMA不支撑对L1存储器的拜访。在休眠形式下,一个唤醒事情能够使处理器切换到下面两个形式之一:

假如PLL_CTL中的BYPASS位被置位,则进行活动形式;

假如PLL_CTL中的BYPASS位被清零,则进行全速形式。

(4) 深度休眠形式

深度休眠形式经过中止PLL、CCLK和SCLK,到达最省电作用。在该方法中,除了实时时钟(RTC)外,处理器内核以及一切其他外设都被制止。该形式下不支撑DMA。

在深度休眠形式中,DEEP_SLEEP输出管脚输出有用电平。深度休眠方法只能被RTC中止或硬件复位事情激活。一个RTC中止使处理器切换到活动形式,一次硬件复位发动硬件复位序列。在深度休眠方法中,SDRAM的守时信号被封闭。在进入深度休眠方法之前,软件应该确保将SDRAM中重要信息转换到其他存储器中。

3. 片上内核电压调理器

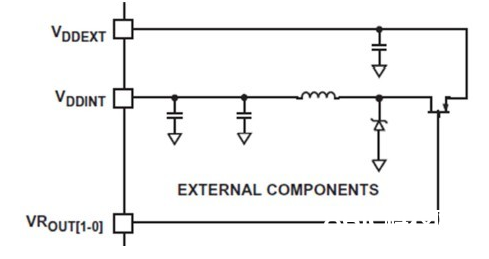

处理器内部供给了一个开关形式电压调理器,只需求几个外部元件,就能够组成一个电压能够设置的动态电源模块,为内核供电。这样,咱们就能够依据不同的处理才能需求,来操控内核电压,到达按需供电的意图。以节省能量。如图5-2所示,图中VROUT为内部调理器PWM 输出,与PMOS、蓄能电感、肖特基二极管以及几个相关的电容,组成典型的BUCK电路。

当然,在不需求功率操控的情况下,这一部分电路也能够省掉,能够用一个固定输出的电路替代。MS531第一版便是选用SPX3819-1.2固定输出的LDO作为内核电源的。VCCINT的规模为0.85~1.30V,不同电压,能支撑的最高频率也是不同的。假如要想更好的功用 ,就得确保较高的内核电压。

图5-2 电源调理器外部结构

VR_CTL 寄存器操控着一切的偏上内核电压调理参数,写入VR_CTL后,将会导致锁相环从头确定。表5-5为VR_CTL寄存器各位的意义。

表5-5 VR_CTL(地址:0XFFC0 0008 复位值0x00DB)

| 位 | 称号 | 描绘 |

| 15:9 | – | 未用 |

| 8 | WAKE |

RTC 唤醒设置 0:不答应RTC唤醒 1:答应RTC唤醒 |

| 7:4 | VLEV |

设定内核电压等级 0000-0101:保存 0110:0.85V 0111:0.90V 1000:0.95V 1001:1.00V 1010:1.05V 1011:1.10V 1100:1.15V 1101:1.20V 1110:1.25V 1111:1.30V |

| 3:2 | GAIN |

电压输出增益操控,值越大电压调理速率越快,可是简单过冲 00:5 01:10 10:20 11:50 |

| 1:0 | FREQ |

调理器的频率,频率越高需求的电感和电容越小,可是会发生较强的EMI 00:旁路/不作业形式 01:333kHz 10:667kHz 11:1MHz |