概述

跟着FPGA芯片密度的添加,串行PROM已不能习惯高密度的FPGA的装备。大容量的并行PROM所要求的寻址办法又不能直接与FPGA接口,这时能够选用XC9500 CPLD和PROM对高密度FPGA进行装备。FPGA设备在线装备或电源上电时,装备逻辑会被主动铲除。FPGA的PROGRAM信号有必要在300ns内置低,使装备逻辑复位。INIT输出在内部装备存储器清零期间坚持低电平。一旦INIT管脚变高,就标明设备已预备承受装备。

FPGA的装备有主设备串行装备和从设备串行装备两种办法。XC4000和Spartan系列设备在INIT变高后要求在设备预备接纳装备数据之前有一个超时期,但Spartan-Ⅱ不在此列。在主设备串行形式下,FPGA在超时到达要求之前封闭装备时钟(CCLK)。在从设备串行形式下,有必要在超时期完成后才干敞开CCLK。而Spartan-Ⅱ和Virtex系列在INIT信号变高之后不要求超时期,一旦INIT信号变高,设备当即预备接纳装备数据。

接口规划

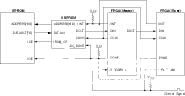

在串行装备形式下用并行PROM对FPGA进行装备时,需求专门的接口进行并行数据到串行数据的转化,并办理FPGA的装备信号。接口的规划办法许多,图1是运用XC9500 CPLD装备FPGA的电路结构。

VSPROM的规划

规划虚拟串行PROM(VSPROM)的意图是为并行PROM和FPGA之间的衔接供给接口,接口的使命是将从PROM中读来的数据转化成串行输出,然后再将地址递加。VSPROM的结构如图2所示。在处理数据的一起,VSPROM还办理INIT和DONE信号。在装备期间,假如INIT被FPGA拉低,标明呈现装备过错,VSPROM有必要复位并等候用户将FPGA复位,然后重新装备。一旦FPGA的DONE变高,标明装备成功,VSPROM就吊销ROM_CS来撤销PROM的使能,将自己和PROM与FPGA阻隔,并将DOUT设为高阻态。

在VSPROM的规划中,运用XC9536PC44-10、XCV600BG432-6和一个8位的PROM(AT27C080)验证。

主设备串行装备时,Xilinx FPGA供给装备时钟(CCLK)。CCLK与VSPROM的时钟CLK_IN直接相连。Virtex和Spartan-Ⅱ支撑的最大装备速率是60MHz,XC4000/Spartan系列支撑的最大装备速率是8MHz。但是,实践的最大装备速率还应该考虑PROM的存取时刻(TACC)和主设备串行输入的时刻(TDSCK)。

主设备串行形式下PROM的频率=1/(TACC+TDSCK)。

TACC关于Virtex为5.0ns,关于XC4000/Spartan系列是20.0ns,PROM的TACC关于AT27C080是100ns。因而,关于Virtex设备最大频率为9.5MHz,关于XC4000/Spartan设备最大频率为8.3MHz。这就是说,Virtex设备的装备频率受PROM的约束,而XC4000/Spartan设备的装备频率受自己内部CCLK的约束。为了加速Virtex设备的装备速度,能够挑选更快的PROM。在主设备串行形式下,FPGA在预备好接纳装备数据之前会封闭CCLK,因而VSPROM的规划不必考虑其他问题。

从设备串行装备有专门的振荡电路供给装备时钟,速度比较快。振荡电路的时钟输出有必要接FPGA的装备时钟(CCLK)和VSPROM的时钟(CLK_IN)。最大装备频率关于Virtex是66MHz,关于XC4000/Spartan系列是10MHz。相同,装备频率遭到PROM的存取时刻(TACC)和从设备串行输入时刻(TDCC)的约束,计算办法同上。

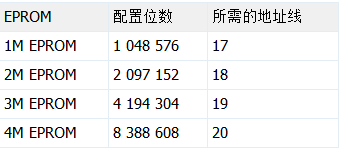

表1 不同的EPROM所需的地址线

从设备串行形式下对XC4000或许Spartan系列FPGA进行装备时,有必要考虑设备开端的次序(这儿评论的次序不适合Spartan-Ⅱ系列)。正如前面提及的,一旦INIT置高,设备能够接纳装备数据之前需求有一个超时期,VSPROM接口有必要能够在超时期到达之前封闭振荡电路的时钟输出。假如是Virtex或许Spartan-Ⅱ设备作为从设备,INIT置高后FPGA能够当即预备好接纳装备数据,就不必考虑超时的问题。

在以上两种装备办法下,并行PROM的巨细和数目由装备FPGA所要求的装备位的数目决议。PROM的巨细由所需求的地址线数目决议。缺省情况下,VSPROM规划运用19根地址线,对应4MB的PROM。当需求更多的容量存储装备数据时,能够修正VSPROM源程序(VHDL或GENERIC)使其习惯新的需求,详细情况拜见表1。假如装备要求多于19根地址线,能够运用XC9572规划VSPROM。

FPGA装备期间产生过错时,INIT信号变成低电平,装备程序间断。所以VSPROM需求办理INIT,当INIT变低时,VSPROM需求复位并等候FPGA的复位后才干进行重新装备。简略的办法是能够在INIT变低时用VSPROM操控FPGA的PROGRAM变低,迫使FPGA铲除自己的装备存储器,然后重试。或许能够将INIT接微操控器,在装备期间INIT变低时操控整个体系复位。

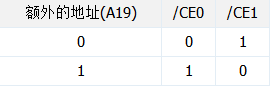

表2 两个PROM的地址译码

接口的扩展

FPGA要求的装备空间大于所选的PROM时,能够运用多个PROM,衔接办法如图3所示。这时地址线是20位,高位地址线 ADDRESS(19)用来挑选PROM,见表2。

多个FPGA能够直接级连,如图4所示。这种情况下对VSPROM没有特别的要求。CCLK,INIT,DONE和PROG信号有必要并联,前一个设备的DOUT信号衔接下一个的DIN。

调试运用

为了确保FPGA的CCLK和DIN信号不受任何搅扰,在规划电路板时通常在每个Vcc和GND之间加0.1μF和0.01μF的电容。一起,要确保Vcc的呼应速度足够快。假如电源呼应速度不够快、呼应单调性欠好,会影响体系的上电进程然后影响正确的装备。

一切的XC4000和Spartan设备都对5V和3.3V环境兼容。Virtex和Spartan-Ⅱ设备也能够直接运用于5V和3.3V的环境,在LVTTL与3.3V的Vcco相连时有必要运用缺省的I/O规范。详细情况拜见Xilinx设备的电压兼容性数据资料。Virtex-E设备不能直接运用在5V环境,因而在装备时有必要加以考虑。

责任编辑:gt