0 导言

跟着电力电子技能的不断发展以及工业用电设备对电能质量需求的不断进步,越来越多的杂乱拓扑结构、大容量体系、高安全稳定性的电力电子设备得到研讨并使用到很多实践工程实践。针对多种电力电子拓扑结构不同工程使用实践,其相应的操控、维护体系相同越来越趋于杂乱化和多样化。先进处理器的操控体系是现代电力电子设备的中心部件[1-3],以 DSP 为代表的传统处理器操控体系在中低压电力电子设备操控和维护中已有广泛的使用,而且取得了杰出的操控作用。但在高压大功率电力电子设备操控体系的使用上,传统 DSP 操控器还存在缺乏。首要是 AD 采样通道和 PWM 信号输出通道数量有限,难以满意拓扑结构杂乱的大功率电力电子设备的检测和操控要求;其次是因为 DSP 芯片在运转中复位在所难免,复位期间无法对电力电子设备进行有用操控与维护;最终是传统 DSP 操控器无法对输出 PWM 信号进行有用检测与辨认,且 PWM 信号犯错后无法当即采纳闭锁等维护措施。

但是,DSP 作为专门用于数字信号处理的微处理器,在条件进程、杂乱的多算法核算方面具有共同优势[4-5],能够在操控体系中添加 FPGA 和 CPLD 补偿其缺乏[6-8]。FPGA 具有强壮的并行处理才能和多时钟频率等长处[9-10], 能完结杂乱的时序逻辑规划,完结高速、高频的 AD 采样和 PWM 信号输出操控及通道扩展[11-12]。而 CPLD 则可高速检测 PWM 输出信号而且在 PWM 信号犯错毛病情况下瞬时发动体系闭锁功用,进步体系操控的牢靠性[13-14]。因而,将 DSP、FPGA 和 CPLD 高效结合并以此来规划操控体系,对高压大功率电力电子设备进行牢靠、全面的操控和维护具有重要意义。

依据上述布景,本文提出一套适用于高压大功率电力电子设备通用型操控操控器。该操控器选用主操控板与其他插件板相分隔的分板块硬件体系结构,结合了 DSP、FPGA、CPLD 各自功用特色的一起统筹了通用性;提出了多时间尺度控保交融的软件规划计划,别离从体系级、器材级、信号级三个层面完结对设备的操控和维护,以满意很多高压大功率电力电子设备对操控与维护的要求。

1 体系全体计划规划

针对高压大功率电力电子设备的安全牢靠性要求较高、操控算法较为杂乱、操控与检测信号量较多等特色,本文以 DSP+FPGA+CPLD 为中心,结合高功用外围器材和高速接口,规划了一种主操控器与外围插件板别离的硬件计划。

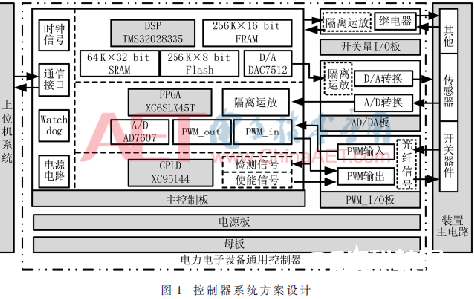

该体系集高速算法运转、快速输入输出接口、多时间尺度控保交融于一体,对不同结构和功率等级电力电子设备的算法履行、继电维护装备都有较强的适应性。依据 DSP+FPGA+CPLD 的电力电子设备通用操控器体系计划如图 1 所示。

2 体系硬件规划计划

2.1 体系首要器材选型

2.2 体系板块功用介绍

由图 1 可知,操控器首要分为包含 DSP、FPGA 和 CPLD 的主操控板,PWM 输入和输出的 PWM_I/O 板,A/D 转化和 D/A 转化的 AD/DA 板,开关量输入和输出的开关量 I/O 板,包含多个开关电源模块的电源板,以及担任上述各个板块间衔接的母板几部分。其间,各个功用板块电路模块规划固定,除主操控板、电源板和母板外,PWM_I/O 板、AD/DA 板、开关量 I/O 板均可依据操控目标需求进行板块数量添加。

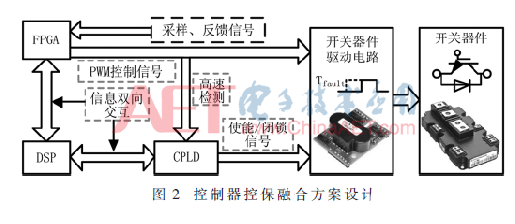

主操控板为整个操控器中心。其间 DSP 及其相应外围电路完结杂乱操控算法履行、事情记载、与上位机通讯、D/A 转化输出以及部分开关量输入输出等中心操控与体系级维护功用;FPGA 及其相应外围电路首要操控高速 A/D 采样与转化、PWM 信号的发生以及 PWM 信号的输出与接纳等器材级操控功用;CPLD 及其相应外围电路完结对 FPGA 发生的 PWM 信号的高速检测,并在 PWM 信号输出正确时输出使能信号完结 PWM 信号向开关器材的传输,不然闭锁 PWM 信号输出,并向 FPGA 和 DSP 进行反应,FPGA 中止 PWM 信号发生和输出,DSP 进行事情记载并输出告警信号。主操控板是整个操控器完结对电力电子设备的多时间尺度控保交融的中心板块。图 2 所示为操控器控保交融计划规划。

PWM_I/O 板是操控器输出中心操控信号的转化通道。其间光纤发射器 HFBR1528T 及其相应外围电路完结将 FPGA 输出的 PWM 电信号转化成 PWM 光信号,并在收到输出使能信号后向开关器材驱动电路输出 PWM 光信号;光纤接纳器 HFBR2528R 及其外围电路则担任将接纳到光信号转化成电信号,并输入值 FPGA。PWM_I/O 板是操控器完结 PWM 信号的输出、检测以及毛病闭锁的要害板块。

AD/DA 板为操控器要害操控信号与反应信号的改换通道。其间由二极管、电阻、电容、扩大器构成的滤涉及运放电路完结对外部传感器输入的电压信号的滤波与扩大,将带采样信号改换为 0~±10 V 的电压信号,并输入至主操控板;相同由二极管、电阻、电容、扩大器构成的运放电路完结对主操控板发生的小功率模拟信号进行扩大并输出。AD/DA 板是操控器完结闭环操控的要害环节。

开关量 I/O 板是操控器与紧迫停机、设备状况指示灯等外部开关量相衔接的通道。当外部开关量信号输入操控器时,经板上 TLP521 光电阻隔模块后转化小电量信号输入主操控板;当操控器开关量信号输出时,经板上继电器模块操控外部器材。

电源板是将外部输入 220 V AC 电源转化成其他板块所需求的 5 V、±15 V、24 V 等直流电源的模块。外部 220 V AC 电源输入操控器时,经板上双节电磁搅扰(ElectromagneTIc Interference,EMI)滤波器滤除高次谐波后,输入给板上各个开关电源模块转化成相应的直流电源。

母板是将上述各个板块进行有用衔接的板块。母板与其他板块之间选用 96 pin 欧式衔接器进行衔接。母板的存在使妥当操控器使用于需求不同的电力电子设备时只需从头规划母板进行直接扩展 PWM_I/O 板、AD/DA 板、开关量 I/O 板操作。

3 体系软件规划计划

操控器体系依据 DSP、FPGA、CPLD 各自特色,选用了依据 DSP 的毫秒级控保计划、依据 FPGA 的微秒级控保计划和依据 CPLD 的纳秒级维护计划相交融的多时间尺度一体化软件规划。

3.1 DSP 软件规划

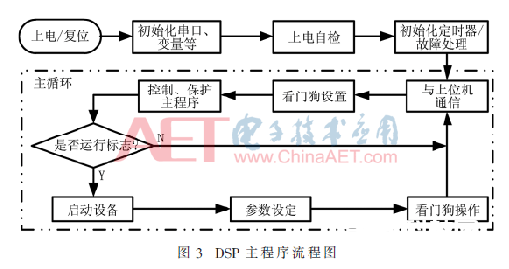

DSP 软件首要完结电力电子设备中心算法运算、与上位机通讯以及事情记载等功用,其程序可分为主程序部分和守时中止服务子程序部分。

主程序包含初始化和主循环两大部分。操控器上电或复位后,首要履行串口和数组初始化程序,然后进行开关量自检和 AD 通道的自检。若自检正常则进行初始化守时器操作,不然履行毛病处理程序,并输出告警信号。初始化完结后进入主循环程序,首要包含与上位机通讯、看门狗设置、等候设备运转等流程。DSP 软件主程序流程如图 3 所示。

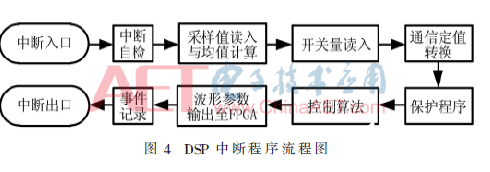

中止程序首要完结中止自检、对来自 FPGA 的 AD 采样值读入与平均值核算、开关量读入、通讯定值转化、维护程序履行、操控算法运算、波形参数(占空比或正弦波)输出以及事情记载。中止程序的履行周期可依据实践设备需求进行修正。DSP 中止程序流程如图 4 所示。

3.2 FPGA 软件规划

FPGA 软件首要为依据多时钟频率下并行处理的高速 AD 采样操控和 PWM 信号的输出全数字化完结。

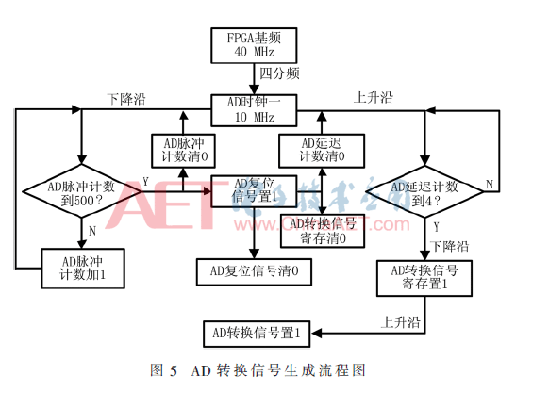

依据芯片 AD7606 采样转化时序的 AD 采样操控首要包含 AD 同步信号生成、AD 复位信号生成、AD 转化信号生成、AD 转化完结信号输出、AD 信号读取等流程。图 5 所示为以 FPGA 主频 40 MHz、10 kHz 采样频率为例的 AD 转化信号生成流程图。

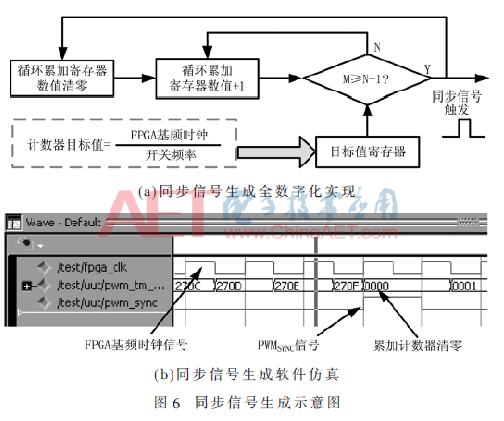

PWM 信号输出数字化完结办法为:使用计数器累加完结同步信号 PWMSNYC 的发生,同步信号的频率为电力电子设备的开关频率。同步信号的数字化生成及其软件仿真成果如图 6 所示。

3.3 CPLD 软件规划

CPLD 软件首要是对 FPGA 生成的 PWM 信号进行高速检测,并在毛病时进行闭锁。详细完结办法为:FPGA 在发生 PWM 信号输出时,一起作为 CPLD 的输入信号,CPLD 程序对输入信号进行高速逻辑判别:若判别输入信号正常,则输出使能信号,完结 PWM 信号向开关器材的输出;不然输出闭锁信号,闭锁 PWM 信号输出,并向 DSP 和 FPGA 输出告警信号。

4 试验验证与成果剖析

为验证本规划的可行性,在大型矿车制动能量收回与使用设备(以下简称“该设备”)上运用了本操控器。

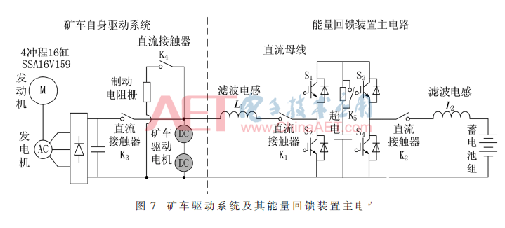

该设备是使用双向 Boost-Buck 改换电路结合超级电容和蓄电池完结矿车制动能量的收回的节能设备。图 7 所示为矿车驱动体系与该设备主电路拓扑结构图。

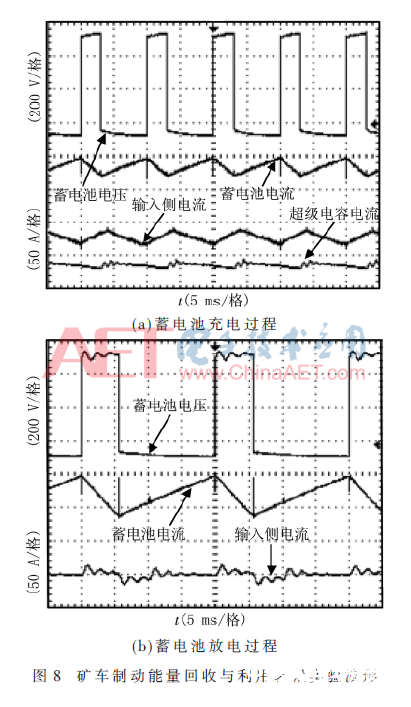

该设备直流母线电容为超级电容组,从左向右,当该设备吸收制动电流时,滤波电感 L1、开关器材 S1 和 S2 构成 Boost 升压电路,开关器材 S3 和 S4、滤波电感 L2 构成 Buck 降压电路;从右向左,当该设备开释蓄电池电能时,滤波电感 L2、开关器材 S3 和 S4 构成 Boost 升压电路,开关器材 S1 和 S2、滤波电感 L1 构成 Buck 降压电路。操控开关器材 S1、S2、S3 和 S4 的通断即可完结对矿车制动能量的收回与使用。在车载试验中,对该设备进行了若干功用性试验和维护动作试验。图 8 所示为部分试验波形,图 8(a)为蓄电池充电试验,此刻直流母线电压为 1 500 V,充电电流为 20 A;图 8(b)为蓄电池放电试验,此刻直流母线电压为 1 500 V,放电电流为 50 A。

用设备完结对矿车制动能量的收回与再使用。

5 定论

本文针对传统 DSP 操控体系在大功率电力电子设备使用中的缺乏,结合 DSP、FPGA、CPLD 三类干流操控芯片各自的特色,提出了一种适用于高压大功率电力电子设备的 DSP+FPGA+CPLD 的通用型操控器规划计划,并经过实践设备试验验证了本规划的可行性。其首要特色和优势如下:

(1)剖析了大功率电力电子设备的操控需求,规划了主操控板与其他插件板相别离的硬件体系,便利应对不同操控目标时的插件板扩展;

(2)依据多时间尺度控保交融的软件规划理念,别离依据体系级、器材级和信号级的时间尺度提出了 DSP、FPGA 和 CPLD 软件规划流程;

(3)在大型矿车制动能量收回与使用设备上使用了本规划,试验波形证明本操控器规划的可行性。