小编引荐:今日小编来跟咱们一同学习一下2D NoC可完成FPGA内部超高带宽逻辑互连

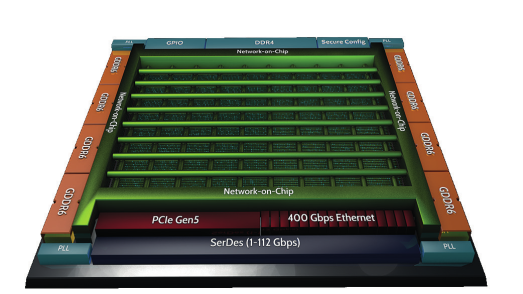

Achronix 最新根据台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器材包含了革命性的新式二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运转的高速公路网络相同,为FPGA外部高速接口和内部可编程逻辑的数据传输供给了超高带宽(~27Tbps)。

图1 Speedster 7t FPGA结构图

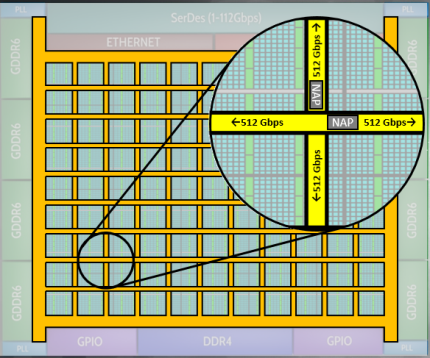

NoC运用一系列高速的行和列网络通路在整个FPGA内部分发数据,然后在整个FPGA结构中以水平缓笔直方法分发数据流量。NoC中的每一行或每一列都有两个256位的、单向的、行业标准的AXI通道,能够在每个方向上以512Gbps(256bit x 2GHz)的传输速率运转。

NoC为FPGA规划供给了几项重要优势,包含:

进步规划的功能。

削减逻辑资源搁置,在高资源占用规划中下降布局布线拥塞的危险。

减小功耗。

简化逻辑规划,由NoC去代替传统的逻辑去做高速接口和总线办理。

完成真实的模块化规划。

本文用一个详细的FPGA规划比如来展现NoC在FPGA内部逻辑互连中发挥的重要作用。本规划首要是完成三重数据加密解密算法(3DES)。该算法是DES加密算法的一种形式,它是关于每个数据块使用三次DES加密算法,经过添加DES的密钥长度添加安全性。

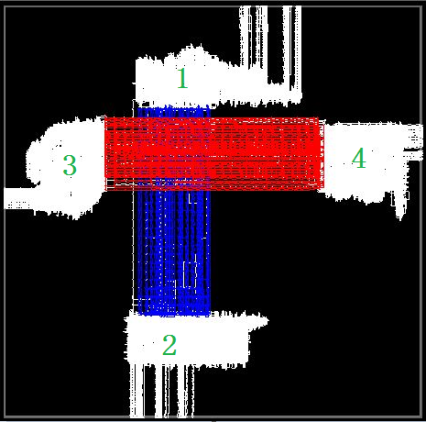

在该FPGA规划中,咱们将输入输出管脚放在的FPGA上下左右四个方向上。上面管脚进来的数据经过逻辑1进行解密然后经过蓝色的走线送到逻辑2加密今后从下面的管脚送出。左面管脚进来的数据经过逻辑3进行解密然后经过赤色的走线送到逻辑4加密今后从右边的管脚送出。如图2 所示。

图2 3DES规划(没有用NoC)后端布局布线图

本规划遇到的问题如下:

加密和解密模块中心的连线延时太长,假如不添加流水寄存器(pipeline),规划功能会收到很大约束。可是因为衔接总线位宽是256位,添加几级流水寄存器又会占用许多额定的寄存器资源。

上下模块之间的衔接总线和左右模块之间的衔接总线呈现了穿插,假如规划再杂乱一点有可能会遇到布局布线部分拥塞,会大大添加东西布局布线时刻。

上面两个问题也是广阔FPGA规划者在杂乱FPGA规划中或多或少会遇到的问题,导致的原因有可能是规划比较杂乱,也有可能是硬件渠道的约束,或许规划有必要衔接不同方位的外围Hard IP导致。

NoC的呈现让咱们上面遇到的问题方便的解决。NoC为FPGA逻辑内部互连供给了双向288bit的原始数据形式(Raw data mode)。 用户能够经过这288bit的信号进行逻辑直连或许自界说协议互连。

图3 使用2D NoC进行内部逻辑互连

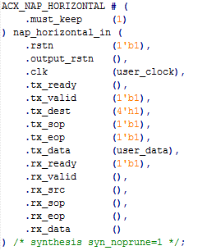

在NoC的每个穿插点上都有两个网络接入点(NAP),用户只需简略地经过例化NAP的原语或许宏界说就能够将自己的逻辑接入到NoC并进行互连。

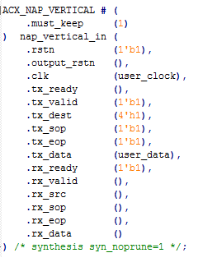

图4 网络接入点NAP

图5 例化NAP宏界说示例

这样经过在3DES加密和解密模块上别离例化NAP,就能够完成3DES加密和解密模块之间的NoC互连。

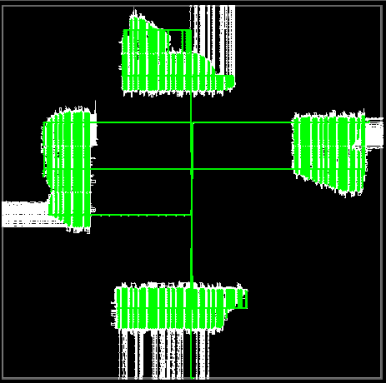

图6 3DES规划(使用NoC)后端布局布线图

这样在简化用户规划的一起,规划功能有了很大的进步,从之前的260MHz进步到了750MHz。 图6中能够看到之前逻辑之间很多的衔接总线现已看不到,总线的衔接都由NoC接收,在后端布局布线图中只能看到绿色时钟走线和白色模块内部的逻辑走线。

本文首要想经过这样一个比如给广阔FPGA规划者展现怎么使用NoC来进行FPGA内部逻辑的互连,然后给广阔FPGA规划者供给另一种考虑问题的思路。在传统的FPGA规划中呈现了功能无法提高,布局布线拥塞的时分,是否能够考虑使用Achronix新一代的Speedster7t FPGA来简化和加快用户的规划