作者 汤瑞 1.我国电子科技集团有限公司第四十一研讨所研制一部(安徽 蚌埠 233010) 2.电子信息测验技能安徽省要点实验室 通讯测验技能(安徽 蚌埠 233010)

摘要:跟着移动通讯的高速开展,矢量信号发生器和分析仪的需求越来越大,高功能宽带本振的高造价成为限制两种仪器本钱的主要因素之一。运用压控振荡器(VCO)完结高功能宽带本振规划,能够在下降模块尺度、下降模块本钱的前提下,完结高相噪、小型化的高功能本振。

*基金项目:国家科技严重专项(编号:2016ZX03001007),安徽省要点研讨与开发计划(编号:1704a0902031)

汤瑞(1988),男,硕士,助理工程师,研讨方向:本振与射频通道规划。

0 导言

移动通讯的开展带动了高功能、大带宽的通讯矢量信号发生器和分析仪的快速开展。本振的相位噪声是限制发射机和接收机的要害性方针,也是衡量一台仪器水平与层次的重要标志之一[1-2]。现在现有的具有高频段、高相噪方针的本振大部分选用依据YIG振荡器的规划计划,此计划规划杂乱,本钱较高,用VCO规划的本振大多用于低端、经济型的产品中。如何用经济型的VCO 规划出高频段高功能的本振以及把规划的高频段高功能本振进行小型化处理,关于既要求高方针,又要求低本钱,并且便携的丈量仪器来说已火烧眉毛。

1 计划规划

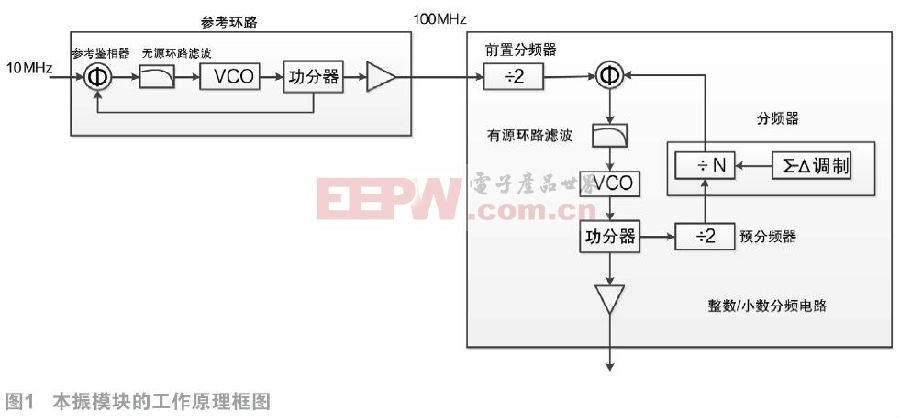

选用宽带高功能VCO(ADI公司HMC586LC4B)外加宽带放大器的方法做成的本振模块,发生4.0 GHz~8.0 GHz,+12 dBm±1 dBm的本振信号输出,是通讯矢量信号源和分析仪整机射频电路的中心模块,其功用块包括参阅环电路、鉴相电路、Σ-Δ调制、分频电路以及FPGA 操控电路等。规划的电路模块的Σ-Δ调制器的宽度(16/24/32/48)能够经过调理对应寄存器的值来操控,别的电路还包括扫频功用。计划原理框图如图1所示。

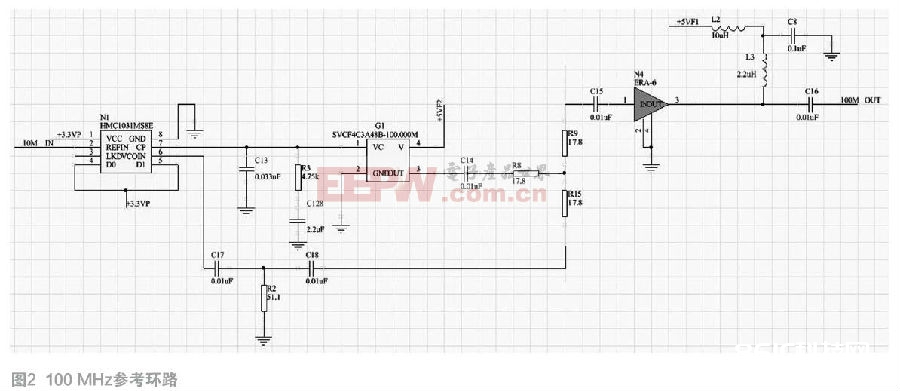

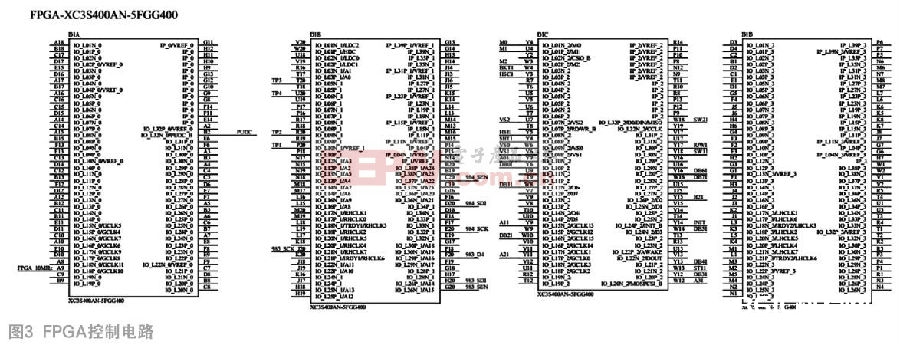

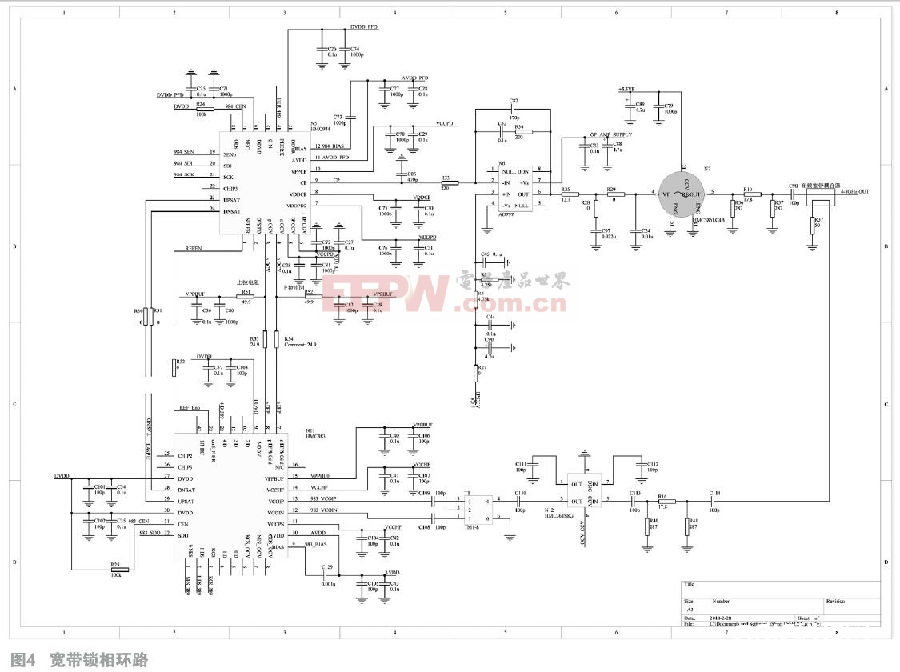

计划中的各个模块原理图及功用简介如下:图2为100 MHz参阅环路模块完结10 MHz高纯参阅经过锁相环 路变成100 MHz高频参阅,用作HMC984LP4E鉴相器的参阅;图3为FPGA操控电路模块操控HMC983LP5E不同寄存器的送数,完结确定不同频率和扫频功用;图4为宽带锁相环

路变成100 MHz高频参阅,用作HMC984LP4E鉴相器的参阅;图3为FPGA操控电路模块操控HMC983LP5E不同寄存器的送数,完结确定不同频率和扫频功用;图4为宽带锁相环 路模块经过HMC983LP5E分频器、HMC984LP4E鉴相器、有源环路滤波器和宽带耦合微带电路完结4 GHz~8 GHz的宽带锁相环

路模块经过HMC983LP5E分频器、HMC984LP4E鉴相器、有源环路滤波器和宽带耦合微带电路完结4 GHz~8 GHz的宽带锁相环 路。

路。

模块中运用的各个参数的值如下:

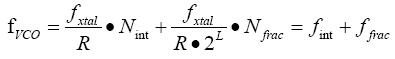

己知: fxtal= 100 MHz,R=2,L=48。

假定fvco= 4600.025 MHz,则4600.025 /(100 /2)= 92.005,所以Nint= 92。

由公式(1)可核算出fvco=140737488355.328,取Nfrac= 140737488355.328。

(1)

(1)

其间:

fvco:压控振荡器(VCO)频率(单位Hz);

fxtal :晶振的频率(单位Hz);

Nint :分频数的整数部分;

Nfrac: 分频数的小数部分;

R :参阅频率的分频数;

L : Σ-Δ调制器的宽度。

对应寄存器因送入的值分别为5Ch,分数分频数存在两个寄存器,Nfrac[17:0]的值为3A5E3h,Nfrac[47:18]的值为8312h。

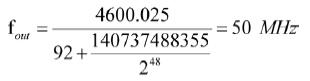

由公式(2)可核算出分频器的输出频率fout的值[3-5]。

(2)

(2)

Nint和Nfrac 能够经过设置相对应的寄存器的值来设定,因而,当需求得到某个输出频率时,只需经过核算得到相对应的整数和小数分频数,并把这两个对应的数值设定到对应的寄有器,就可得到想要的输出频率。整数和小数分频数是经过软件核算得到并经过FPGA 依照dataSheet 的要求送入相应的寄存器内。

2 要害电路规划

2.1 高频宽带耦合器规划

规划初期选用3个17.8 Ω电阻组成功分网络,测验成果不抱负,信号输出平整度无法满意计划要求。之后,依据计划规划要求,进行ADS仿真,规划出如图5所示的微带耦合器,直接放置到印制板上,减少了装置过程,并且作用抱负。信号平整度得到了优化,达到了计划要求。

2.2 宽带放大器电路规划

整机计划需求大于+10 dBm的本振信号作为混频本振,锁相环 路自身发生的信号功率只要0 dBm左右,需求接入一个宽带放大器才干确保输出信号,满意整机关于本振信号的要求。宽带放大器挑选FGB-1509(FIRSAR公司),该放大器的增益和增益平整度、频率规模都能够满意计划的需求。选用适宜的偏置电路,使得该芯片正常作业,就可完结输出+12 dBm±1 dBm。

路自身发生的信号功率只要0 dBm左右,需求接入一个宽带放大器才干确保输出信号,满意整机关于本振信号的要求。宽带放大器挑选FGB-1509(FIRSAR公司),该放大器的增益和增益平整度、频率规模都能够满意计划的需求。选用适宜的偏置电路,使得该芯片正常作业,就可完结输出+12 dBm±1 dBm。

3 测验成果

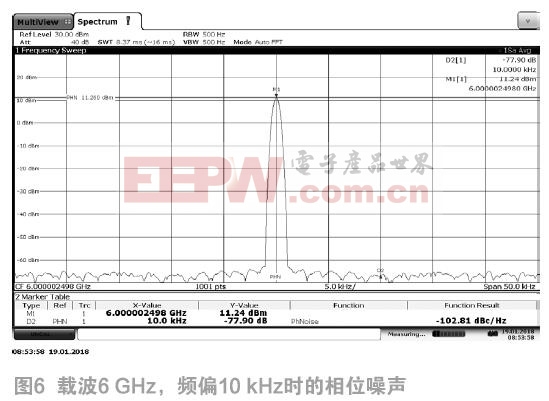

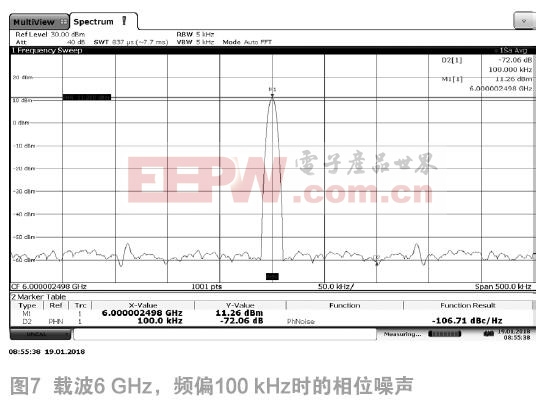

模块烧入编写好的FPGA工程后,接入整机调试渠道,运用罗德与施瓦茨公司的FSW26测验输出的信号,相位噪声方针如图6所示,载波6 GHz,频偏10 kHz时为-102.81 dBc/Hz;如图7所示,载波6 GHz,频偏100 kHz时为106.71 dBc/Hz。

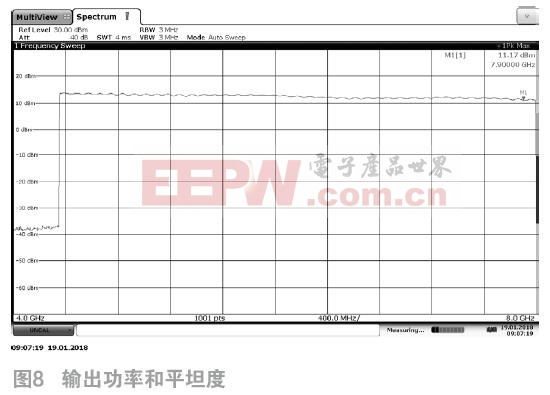

模块输出信号的功率和平整度如图8所示。

4 定论

运用FPGA操控HMC983LP5E不同的分频数,得到需求的频率点,完结4 GHz到8 GHz的频率源,完结了本钱低、功能高的高频宽带本振模块,达到了预期的计划方针。计划用经济型的VCO 规划出高频段高功能的本振并把规划的高频段高功能本振进行小型化处理,关于既要求高方针又要求低本钱并且便携的丈量仪器来说至关重要, 现在这个计划现已使用到两款产品中,两款产品年出产100台。

参阅文献:

[1]远坂俊昭.锁相环 (PLL)电路规划与使用[M].何希才,译.北京:科学出版社,2006.

(PLL)电路规划与使用[M].何希才,译.北京:科学出版社,2006.

[2]杜勇.锁相环技能原理及FPGA完结[M].北京:电子工业出版社,2016.

[3]Hittite Microwave Corporation.HMC586LC4B WIDEBAND MM%&&&&&% VCO w/ BUFFER AMPLIFIER, 4.0 – 8.0 GHz[Z].Chelmsford:Hittite

[4]Hittite Microwave Corporation.HMC984LP4E DIGITAL PHASE-FREQUENCY DETECTOR[Z].Chelmsford:Hittite

[5]Hittite Microwave Corporation.HMC983LP5E DC – 7 GHZ FRACTIONAL-N DIVIDER AND FREQUENCY SWEEPER[Z].Chelmsford:Hittite

本文来源于《电子产品世界》2018年第7期第30页,欢迎您写论文时引证,并注明出处。