7.1FPGA规划仿真验证的原理和办法

7.1.1FPGA规划仿真验证

严厉来讲,FPGA规划验证包含功用与时序仿真和电路验证。仿真是指运用规划软件包对已完结的规划进行完好测验,模仿实践物理环境下的工作情况。

功用仿真是指仅对逻辑功用进行测验模仿,以了解其完结的功用是否满意原规划的要求。仿真进程没有参加时序信息,不触及详细器材的硬件特性,如延时特性等,因而也叫前仿真。它是对HDL硬件规划言语的功用完结才能进行仿真,以保证HDL言语描绘能够满意规划者的开始目的。

时序仿真则是在HDL能够满意规划者功用要求的基础上,在布局布线后,提取有关的器材推迟、连线延时等时序参数,并在此基础上进行的仿真,也称为后仿真,它是挨近实在器材运转的仿真。

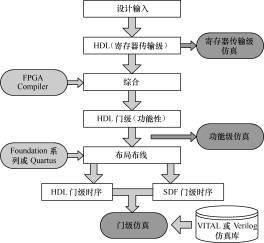

如图7.1所示是FPGA规划仿真验证的根本办法。

图7.1FPGA规划仿真验证根本办法

7.1.2FPGA规划仿真的切入点

在FPGA的规划中,完好的规划流程往往会触及多个EDA东西,比方规划输入东西、归纳东西、布局布线东西、仿真东西等。如何将这些EDA东西进行恰当的结合,在契合各个东西接口情况下发挥各个东西的专长,是每一个FPGA规划工程师都要面对的问题。

如图7.2所示是运用仿真东西ModelSim与归纳东西FPGACompilerII及布线东西FoundationSeries或Quartus相配合完结FPGA规划的流程图。

图7.2FPGA规划仿真切入点

在规划输入阶段,因为Modelsim仅支撑VHDL或VerilogHDL,所以在选用多种规划输入东西时,能够运用文本编辑器完结HDL言语的输入。当然也能够运用相应的东西以图形方法完结输入,但有必要能够导出对应的VHDL或VerilogHDL格局。

近年来呈现的图形化HDL规划东西,能够接纳逻辑结构图、状况转换图、数据流图、控制流程图及真值表等输入方法,并经过装备的翻译器将这些图形格局转化为HDL文件,如MentorGraphics公司的Renoir,Xilinx公司的Foundation系列都带有将状况转换图翻译成HDL文本的规划东西。

从图7.2能够看出,在FPGA规划进程中,有3处能够运用Modelsim进行仿真。

(1)寄存器传输级(RTL)仿真。

此级仿真是对规划的语法和根本功用进行验证(不含时序信息)。在RTL仿真阶段,应该树立一个测验台。此测验台能够在整个FPGA流程中进行仿真验证(RTL级、功用级、时序门级)。测验台不光供给测验鼓励与接纳呼应信息,并且能够测验HDL仿真流程中的要害功用(如运算部件输出值的正确性等)。测验台的发生能够直接运用文本编程得到,也能够运用图形化东西输入,再由软件翻译为HDL格局,例如运用HDLBencher软件运用其杰出的波形输入界面输入测验鼓励,再由其主动转化为HDL格局而得到。

(2)针对特定的FPGA专有技能的仿真。

此级仿真是在归纳后、完结前而进行的功用仿真。功用仿真一般验证归纳后是否能够得到规划者所需求的正确功用,并且功用仿真的成果往往与RTL级仿真成果相同。

(3)门级仿真。

此级仿真是针对门级时序进行的仿真,门级仿真体现出因为布局布线而发生的实践延时。在这个阶段,仿真的成果和规划者挑选的FPGA类型有着直接的联系。因为不同的FPGA的内部成果有所差异,因而同一个规划在不同FPGA类型上得到的门级仿真成果也是不同的。