在最原始的测验进程中,对集成电路(IntegratedCircuit,IC)的测验是依托有经历的测验人员运用信号发生器、万用表和示波器等仪器来进行测验的。这种测验办法测验功率低,无法完结大规模大批量的测验。跟着集成电路的集成度和引脚数的不断增加,工业出产上有必要要运用新的合适大规模电路测验的测验办法。在这种情况下,集成电路的主动测验仪开端不断发展。

现在国内的同类型产品中,一部分选用了单片机完结,这部分仪器剖析速度慢,难以用于大规模的测验体系之中,并且在管脚的扩展性上遭到严峻的约束。另一部分运用了DSP芯片,尽管功用上较为完善,但造价不菲,有用功用有限。本文的规划是根据FPGA完结逻辑芯片的功用故障测验。因为FPGA芯片价格的不断下降和低端芯片的不断出现,运用FPGA作为主控芯片能够更合适于商场,且有利于对功用进行扩展。试验标明,该体系规划合理,能对被测芯片进行精确的功用测验。

1.逻辑芯片功用测验的基本理论简介

功用测验也称为合格-不合格测验,它决议了出产出来的元件是否能正常作业。一个典型的测验进程如下:将预先界说的测验模板加载到测验设备中,它给被测元件供给鼓励和搜集相应的呼应;需求一个探针板或测验板将测验设备的输入、输出与管芯或封装后芯片的相应管脚连接起来。测验模板指的是施加的波形、电压电平、时钟频率和预期呼应在测验程序中的界说。

元件装入测验设备,测验设备履行测验程序,将输入模板序列应用于被测元件,比较得到的和预期的呼应。假如观察到不同,则表明元件犯错,即该元件功用测验不合格。

2.测验体系规划

该测验体系由下位机硬件电路和上位机测验软件两大部分构成。体系选用功用模块化规划,操控灵敏,操作简略,并且选用ROM存储测验向量表库,便利今后的芯片型号增加和扩展,有很好的实践应用性。

2.1 硬件规划

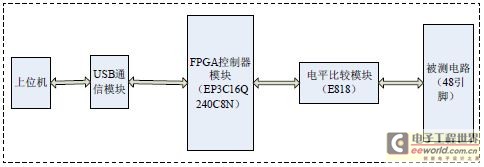

体系硬件主要由FPGA操控器模块、串口通讯模块、电平比较模块和测验渠道模块构成,其结构如图1所示。

图1 体系硬件结构图

操控器模块选用Altera的FPGA芯片EP3C16Q240C8N,装备芯片选用EPCS4.操控器由运用VerilogHDL硬件言语完结了包含串口接纳模块、数据转化与测验维护模块和串口发送模块三个部分的功用规划。串口接纳模块完结与串口芯片MAX3232进行通讯,接纳由上位机发送来的测验指令;数据转化与测验维护模块发生完结一个类似于D触发器的维护器,对测验端的被测芯片输出脚进行双维护,保证其在测验后的回测值不受初值影响;串口发送模块将测验后得到的数据组合为一个回测寄存器,并依照串口通讯协议将回测数据发送回上位机。

串口通讯模块选用MAX3232芯片,现串口的全双工数据传输。

E818电平比较电路为逻辑功用测验的中心硬件部分。E818是SEMTECH公司专门针对ATE逻辑功用测验而开发的窗口比较器芯片,它处理了被测目标DUT芯片的双向输入数据电平要求。

2.2 软件规划

体系软件上位机软件是运用VC++6.0来编写的。上位机调用Access中的测验数据,经串口发送出后,体系硬件就会运转测验程序。测验完毕后硬件体系会将测验得到的回来数据发送回上位机软件。这时,上位机软件接纳到回来数据后需求对回来数据与规范无故障值进行比照,以确认此次测验是否正确经过。所以上位机软件的功用分为:数据库的调用,测验矢量的接纳和发送和回测信号的比照三大部分。体系软件流程图如图2所示。

图2 体系软件流程图

3.体系测验验证

3.1 惯例测验

以芯片74LS08为例,测验流程如下:

(1)运用Microsoft Office Access2003软件树立测验数据库,并在数据库中树立几款不同被测芯片的测验数据。