1 导言

集成运放以其价格低廉、性能优越等特色在个人数据助理、通讯、轿车电子、音响产品、仪器仪表、传感器等范畴得到广泛应用。跟着数字技能的不断进步和集成电路商场的开展.兼有模仿和数字集成电路的SOC或混合集成电路将越来越受注重。与此一起,集成运放参数的测定也将对研制人员和技能仪器提出更高的要求,传统的运放测验仪校准计划已不能满意商场特别是国防军工的要求.运放测验仪的校准面对严峻应战。因而,进步运放测验仪的测验精度,确保运放器材的准确性是现在应处理的关键问题。

2 体系计划证明

2.1 信号发生器计划证明

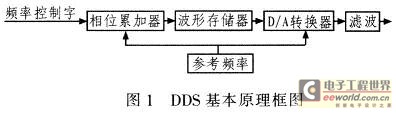

考虑到单片函数发生器的外接电阻电容对参数影响很大,因而发生的频率安稳度较差、精度低、抗搅扰才能低,且不易操控;而选用数字锁相环频率组成技能,因为锁相环自身是一个慵懒环节,确定时刻长,所以频率转化时刻也会添加,一起频率受VCO可变频率规划的影响,频带不能做得很宽。这儿选用直接数字频率组成技能(Direct Digital Frequency Synthesis,简称DDFS或DDS)。DDS以Nyquist时域采样定理为根底,在时域中进行频率组成,图1为其基本原理框图。DDS依据相位累加组成技能,在数字域中完成频率组成,可输出高精度的频率信号,频率规划大、精度高、操控性能好且易完成。DDS专用集成器材依据DDS原理,具有转化速度快、分辨率高、频带宽等特色,可输出安稳的高频信号,但不合适发生低频信号。因而体系中5Hz低频信号由FPGA内部的DDS供给。

2.2 丈量操控电路计划证明

为在同一电路中完成不同参数的分步丈量及主动量程转化,需规划通断操控电路。因而,这儿选用模仿开关。因存在导通电阻,在选通时该电阻加于电路,会带来丈量差错;继电器导通电阻较小,但相对于模仿开关规划大、电路散布参数,简单引起闭环测验电路的寄生振动;考虑到精度,体系选用继电器操控不同参数测验电路的主动转化,经过添加补偿电容来防止振动,为防止输出波形失真,体系还选用三极管共发射极电路对继电器进行操控。2.3幅值检测计划证明计划1:数字办法。由A/D转化器采样后将数据送入FPGA进行峰值检测或有效值检测,该办法可进步精度和安稳度,且防止了模仿器材不安稳或漂移等要素的影响,但受 A/D转化器采样速率的约束,所处理的信号频率达不到很高。计划2:模仿办法。包含峰值检波和有效值检波。前者经过操控%&&&&&%充放电速度完成,后者依据沟通信号有效值界说式,选用模仿电路完成,典型有效值检测器材如AD637。体系在丈量AVD、KCMR时,输出信号的沟通重量频率为5 Hz,故选用计划1;丈量增益带宽积BWG时,输出频率规划为40 kHz~4 MHz,故选用计划2。

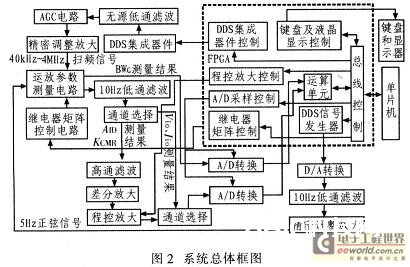

依据以上计划证明,体系整体框图如罔2所示。体系首要由信号发生、参数测验、测验电路操控和人机交互等模块组成,单片机和FPGA一起操控模块。5 Hz信号由FPGA内部DDS发生,扫频信号由AD9851发生;丈量电路的输出成果经后级滤波、扩大处理后由A/D转化器采样送至FPGA进行运算;单片机和FPGA经过继电器挑选以丈量电路和丈量量程;FPGA供给键盘和显示器以完成人机交互;丈量成果存储在RAM中,并能经过微型打印机打印出来。

3 理论剖析与首要电路规划

3.1 信号源的完成

5 Hz信号发生的参阅频率为fCLK=1 MHz,相位累加器的位数是32,频率操控字为21 475,其输出频率则为(106/232)×21475≈5.000 038 1 Hz,而相对差错的绝对值为(5.000 038 1-5)/5×100%≈0.000 762%。5 Hz信号对D/A转化速率要求不高,为进步精度,体系选用12位D/A转化器材MX7541。

40 kHz~4 MHz扫频信号由DDS专用器材AD9851发生。经过对输出正弦波的频率进行步进操控可完成扫频输出。频率分辨率设为1 kHz,假如以1 kHz为频率步进值,则需求步进(4×106-40×103)/1 000=3 960次,而要求扫描时刻小于等于10 s。扫描速度应大于等于10 s/3 960=2.525次/ms。考虑到实测器材的状况,为确保丈量的可靠性,选用非等步长步进,即跟着频率添加,步进量添加,在挨近截止频率点时减小步进频率,确保频率分辨率为1 kHz。

在AD9851输出级接截止频率为15 MHz的椭圆滤波器来按捺高频谐波搅扰,并经过AD603构成的AGC电路和精细调整扩大电路使输出有效值安稳在2 V。

3.2 运放参数测验电路

体系选用“被测器材一辅佐运放”形式构成安稳的负反馈网络。使输出电压箝坐落预置电压,从而将小电压、小电流的丈量转化为伏特级电压的丈量。依据VIO、IIO、KCMR、BWG等5个参数丈量电路的相似性将其简化为一个规范丈量电路模板.经过按键挑选不同参数的丈量电路,如图3所示。

3.2.1 输入失调电压VIO、输入失调电流IIO的丈量

闭合S1、S3、S4、S12,S2→3、S11→3,测得辅佐运放的输出电压为VIO,则有:![]()

在重复VIO丈量过程的根底上再断开S3、S4,测得辅佐运放的输出电压为VLI,则有:![]()

在丈量VIO时,Ri=100 Ω,Rj=61.6 kΩ,其精度均为0.3%,由Ri和RF形成的最大差错小于0.6%;在丈量IIO时,应满意:![]()

体系选取R=436 kΩ,IIO~(0,4μA),VIO~(0,40 mV),以上两个条件均能满意。

3.2.2 差模开环沟通电压增益AVD的丈量

闭合S1、S3、S4、S10、S12,S2→3、S11→1,设信号源输出电压为VS,测得辅佐运放输出电压为VLO,则有:![]()

AVD的丈量差错在很大程度上取决于电路中R1、R2的匹配精度,若匹配差错为δ=(R1-R2)/R2,δ1=(Rf-Ri)/Ri,则单纯由电阻失配引起的相对差错为△A VD=”20″ log(δ+1),该体系占为0.6%。

根据GB3442-82的集成运放参数测试仪规划

1引言集成运放以其价格低廉、性能优越等特点在个人数据助理、通信、汽车电子、音响产品、仪器仪表、传感器等领域得到广泛应用。随着数字技术的不断进步和集成电路市场的发展.兼有模拟和数字集成电路的SOC或混合

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/ceping/206065.html