在当今的GHz速率的串行数据测验中,眼图和颤动测验是最重要的两个测验项目。眼图和颤动丈量中,测验仪器有必要从待测验信号中康复参阅时钟,用该时钟同步和采样数据。因而,康复时钟的办法会直接影响眼图和颤动测验成果,各种串行数据规范都规则了颤动丈量中时钟康复电路CDR的参数,正确的设置测验仪器的CDR参数才能够使丈量成果与芯片接纳端的实践功能坚持一致。

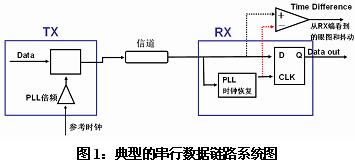

下图1所示为某串行数据链接的体系图,在Fibre Channel、Gigabit Ethernet、SDH等串行链路中都选用了这样的架构。发送端(TX)发送的信号经过信道传输到接纳端(RX)后,收发器芯片RX部分的时钟康复电路从串行数据中康复出时钟,用康复的时钟来同步串行数据,进行采样。因为多种原因,进入RX的串行数据信号可能有较大的颤动,抱负情况下(锁相环PLL的环路带宽无穷大时),时钟康复电路的PLL输出的时钟和RX的输入数据信号同相,即零颤动,这时,RX的判别电路(如图1中的D触发器)有最大的树立时刻和坚持时刻余量。可是,因为PLL的环路响应为低通滤波器特性,只能消除串行数据中低频段的颤动,不能处理高频颤动,所以,现实情况中收发器芯片RX端“看到”的眼图是有颤动的。

在图1中,RX端PLL的参数是影响眼图和颤动功能的决定因素。PLL是一种广泛运用的电子电路,能够用于取得特定频率的时钟、射频信号调制与解谐和串行数据的时钟康复。

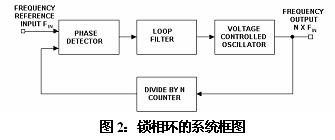

如图2为PLL的体系图,包含鉴相器(phase detector)、环路滤波器(loop filter)、压控振荡器(voltage controlled oscillator,简称VCO)三个根本部分。PLL的作业原理请参阅模仿电路书本。

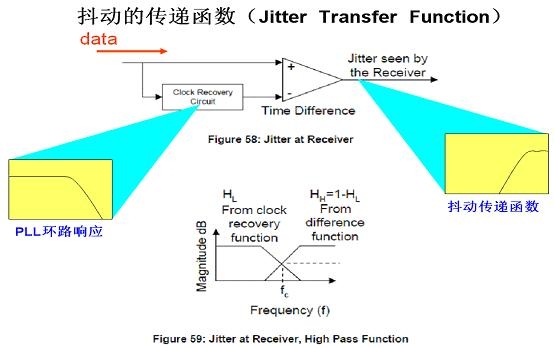

在接纳端的PLL中,鉴相器、环路滤波器和VCO三部分组成的环路的频响为低通滤波器特性。如下图3所示,接纳端的时钟康复电路的频响是一个低通滤波器,其传递函数为HL,当串行数据信号的颤动改变频率较低时,即从直流到PLL的到频率,PLL能及时追寻到数据跳变沿(即锁住相位),输出的时钟与输入数据同相(严厉讲相位差为固定常数),这样颤动为零。当接连边缘的颤动改变太快时(即存在高频颤动时),PLL不能及时追寻到边缘的改变,所以输出的时钟和数据边缘存在颤动,所以,接纳端的CDR不能滤除高于到频率的颤动,它的颤动传递函数(Jitter Transfer Function简称JTF)的频响为高通滤波特性,接纳端CDR又称为TIE颤动的高通滤波器。如图3,颤动传递函数HH=1-HL。

图3:颤动的传递函数

在收发器接纳端除了选用如图1所示的PLL来康复时钟外,另一种时钟康复办法是运用相位内插器(phase interpolator,简称PI),在FBDIMM和PCI Express中都运用PI来康复时钟,可是运用仪器测验时,能够用PLL来建模。

测验高速串行数据信号的眼图与颤动的仪器都运用了根据锁相环的时钟康复办法。其间,实时示波器首要运用软件PLL来康复参阅时钟,取样示波器和误码率测验仪都运用硬件PLL来康复时钟。实时示波器作为最遍及和广泛应用的测验仪器,本文仅介绍实时示波器的软件CDR和眼图测验、颤动测验的联系。