S3C2440内部集成了一个Nand flash操控器。S3C2440的Nand flash操控器包含了如下的特性:

l 一个引导发动单元

l Nand Flash存储器接口,支撑8位或16位的每页巨细为256字,512字节,1K字和2K字节的Nand flash

l 软件形式:用户能够直接拜访Nand Flash存储器,此特性能够用于Nand Flash存储器的读、擦除和编程。

l S3C2440支撑8/16位的Nand Flash存储器接口总线

l 硬件ECC生成,检测和指示(软件纠错)。

l Steppingstone接口,支撑大/小端形式的按字节/半字/字拜访。

我用的开发板是天嵌的TQ2440,板子用到的Nand Flash是Samsung公司的K9F2G08U0A,它是8位的Nand flash。本文只介绍Nand Flash的电路原理和Nand Flash的读、写、擦除等根本操作,暂不触及Nand Flash发动程序的问题。

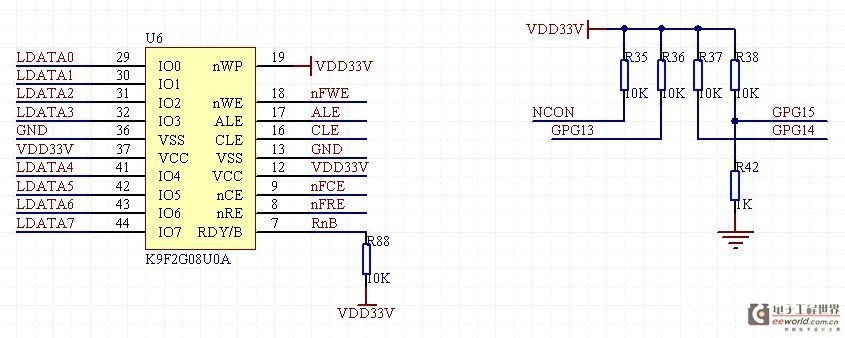

Nand Flash的电路衔接如图 1所示:

图 1 Nand Flash电路原理

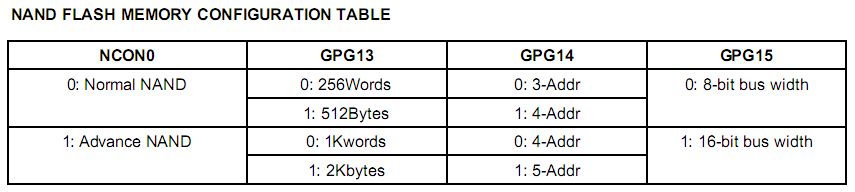

上图的左面为K9F2G08U0A与2440的衔接图,原理方面就不多介绍,去看看datasheet估量就懂得了,右边的部分是S3C2440的Nand操控器的装备。装备引脚NCON,GPG13,GPG14和GPG15用来设置Nand Flash的根本信息,Nand操控器经过读取装备引脚的状况获取外接的Nand Flash的装备信息,图 2是这四个装备引脚的界说:

图 2 Nand操控装备引脚信息

因为K9F2G08U0A的总线宽度为8位,页巨细为2048字节,需求5个寻址指令,所以NCON、GPG13和GPG14应该接高电平,GPG15应该接低电平。

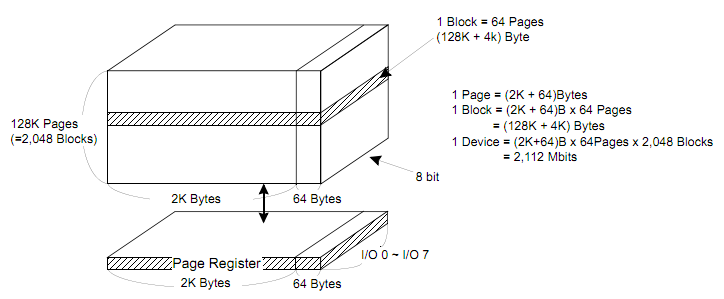

K9F2G08U0A没有地址或数据总线,只需8个IO口,这8个IO口用于传输指令、地址和数据。K9F2G08U0A主要以page(页)为单位进行读写,以block(块)为单位进行擦除。每一页中又分为main区和spare区,main区用于正常数据的存储,spare区用于存储一些附加信息,如块好坏的符号、块的逻辑地址、页内数据的ECC校验和等。K9F2G08U0A的存储阵列如图 3所示:

图 3 K9F2G08U0A内部存储阵列

由上图,咱们能够知道:K9F2G08U0A的一页为(2K+64)字节(2K表明的是main区容量, 64表明的是spare区容量),它的一块为64页,而整个设备包含了2048个块。这样算下来一共有2112M位容量,假如只算main区容量则有256M字节(即256M×8位)。

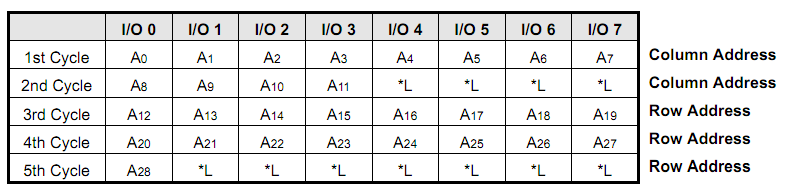

图 4 K9F2G08U0A地址序列

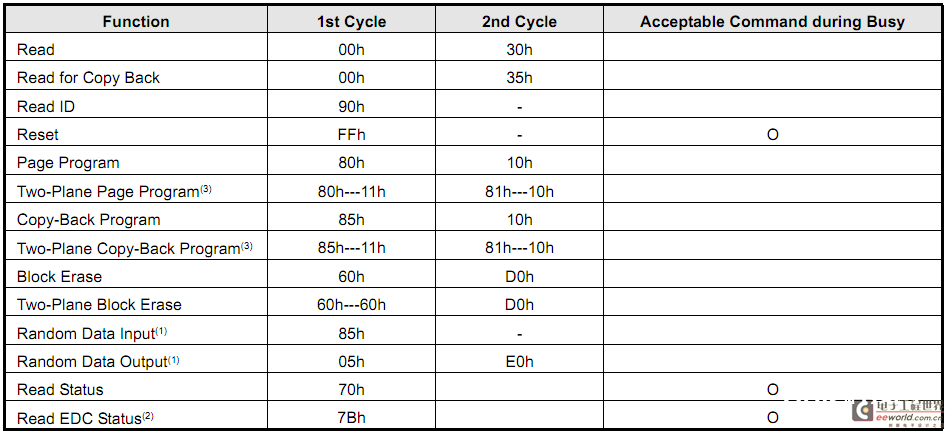

要完结用8个IO口来要拜访这么大的容量,如图 4所示:K9F2G08U0A规则了用5个周期来完结。第一个周期拜访的地址为A0~A7;第二个周期拜访的地址为A8~A11,它作用在IO0~IO3上,而此刻IO4~IO7有必要为低电平;第三个周期拜访的地址为A12~A19;第四个周期拜访的地址为A20~A27;第五个周期拜访的地址为A28,它作用在IO0上,而此刻IO1~IO7有必要为低电平。前两个周期传输的是列地址,后三个周期传输的是行地址。经过剖析可知,列地址是用于寻址页内空间,行地址用于寻址页,假如要直接拜访块,则需求从地址A18开端。因为一切的指令、地址和数据全部从8位IO口传输,所以Nand flash界说了一个指令集来完结各种操作。有的操作只需求一个指令(即一个周期)即可,而有的操作则需求两个指令(即两个周期)来完结。K9F2G08U0A的指令阐明如图 5所示:

图 5 K9F2G08U0A指令表

为了方便运用,咱们宏界说了K9F2G08U0A的常用指令

#define CMD_READ10x00 //页读指令周期1

#define CMD_READ20x30 //页读指令周期2

#define CMD_READID 0x90 //读ID指令

#define CMD_WRITE1 0x80 //页写指令周期1

#define CMD_WRITE2 0x10 //页写指令周期2

#define CMD_ERASE1 0x60 //块擦除指令周期1

#define CMD_ERASE2 0xd0 //块擦除指令周期2

#define CMD_STATUS0x70 //读状况指令

#define CMD_RESET0xff //复位

#define CMD_RANDOMREAD1 0x05 //随意读指令周期1

#define CMD_RANDOMREAD2 0xE0 //随意读指令周期2

#define CMD_RANDOMWRITE 0x85 //随意写指令

接下来介绍几个Nand Flash操控器的寄存器。Nand Flash操控器的寄存器主要有NFCONF(Nand Flash装备寄存器),NFCONT(Nand Flash操控寄存器),NFCMMD(Nand Flash指令集寄存器),NFADDR(Nand Flash地址集寄存器),NFDATA(Nand Flash数据寄存器),NFMECCD0/1(Nand Flash的main区ECC寄存器),NFSECCD(Nand Flash的spare区ECC寄存器),NFSTAT(Nand Flash操作状况寄存器),NFESTAT0/1(Nand Flash的ECC状况寄存器),NFMECC0/1(Nand Flash用于数据的ECC寄存器),以及NFSECC(Nand Flash用于IO的ECC寄存器)。

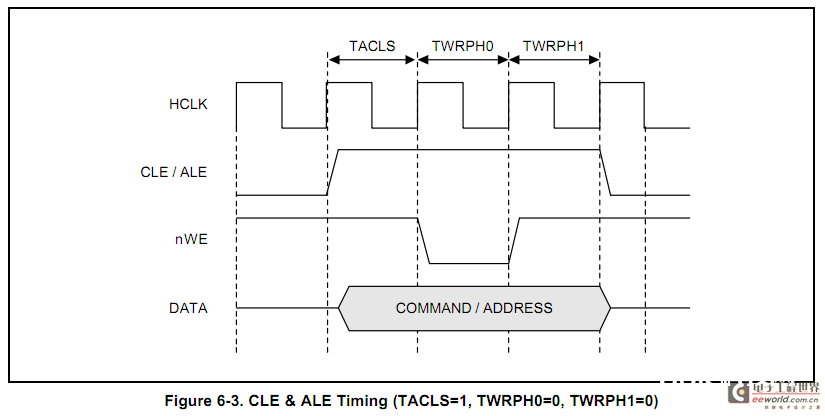

(1)NFCONF:2440的NFCONF寄存器是用来设置NAND Flash的时序参数TACLS、TWRPH0、TWRPH1。装备寄存器的[3:0]是只读位,用来指示外部所接的Nand Flash的装备信息,它们是由装备引脚NCON,GPG13,GPG14和GPG15所决议的(比方说K9F2G08U0A的装备为NCON、GPG13和GPG14接高电平,GPG15接低电平,所以[3:0]位状况应该是1110)。

(2)NFCONT:用来使能/制止NAND Flash操控器、使能/制止操控引脚信号nFCE、初始化ECC。它还有其他功用,在一般的运用顶用不到,比方确定NAND Flash。

(3)NFCMMD:关于不同类型的Flash,操作指令一般不一样。参阅前面介绍的K9F2G08U0A指令序列。

(4)NFADDR:当写这个寄存器时,它将对Flash宣布地址信号。只用到低8位来传输,所以需求分次来写入一个完好的32位地址,K9F2G08U0A的地址序列在图4现已做了具体阐明。

(5)NFDATA:只用到低8位,读、写此寄存器将发动对NAND Flash的读数据、写数据操作。

(6)NFSTAT:只用到位0,用来检测NAND是否准备好。0:busy,1:ready。

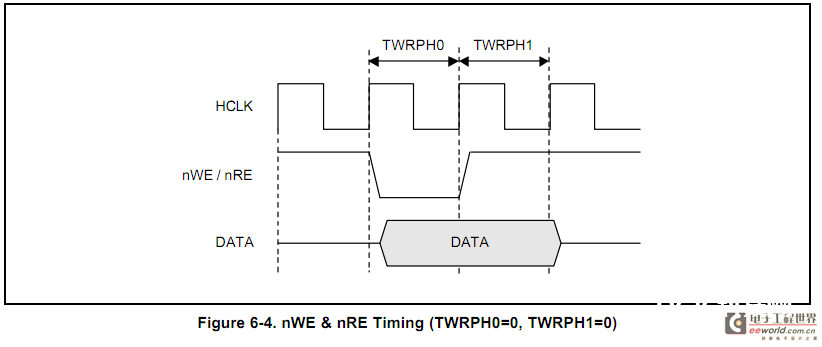

NFCONF寄存器运用TACLS、TWRPH0、TWRPH1这3个参数来操控NAND Flash信号线CLE/ALE与写操控信号nWE的时序联系,它们之间的联系如图6和图7所示:

图6 CLE/ALE时序图

图7 nWE和nRE时序图

TACLS为CLE/ALE有用到nWE有用之间的持续时刻,TWRPH0为nWE的有用持续时刻,TWRPH1为nWE无效到CLE/ALE无效之间的持续时刻,这些时刻都是以HCLK为单位的。经过查阅K9F2G08U0A的数据手册,咱们能够找到并核算与S3C2440相对应的时序:K9F2G08U0A中的Twp与TWRPH0相对应,Tclh与TWRPH1相对应, TACLS应该是与Tcls相对应。K9F2G08U0A给出的都是最小时刻, 2440只需满意它的最小时刻即可。TACLS、TWRPH0、TWRPH1这三个变量取值大一些会更稳妥,在这里,这三个值别离取1,2和0。