这两个都是小型设备的处理器架构。MIPS架构的处理器多用在网关、猫、机顶盒什么的。ARM处理器用在便携设备,智能手机。这两个东西的商场简直很少堆叠,因此也谈不上比照。

普通用户重视MIPS首要仍是因为我国所谓的”龙芯“。龙芯一开端抄袭MIPS,后来购买到了授权。倒也并非龙芯不想展开X86架构的桌面CPU商场或许ARM架构的移动设备商场,是因为这两家的授权太过于严苛。X86的授权Intel已然不或许再授权。ARM是一家芯片规划公司,只能给出运用授权,不会赞同让龙芯自行规划。只要MIPS才可行,MIPS的授权说白了便是随意抄随意改。

许多龙芯的支撑者提出了MIPS有理论上有许多的抢先,但不要忘了ARM是一家商业公司,商场占有率高,竞赛认识也十分强。简直一切的智能手机都是ARM架构,便是最有力的证明。

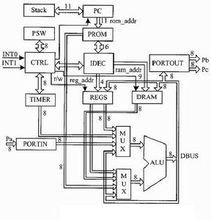

1.流水线结构 pipeline

– MIPS 是最简略的体系结构之一,所以使大学喜爱挑选 MIPS 体系结构来介绍核算体系结构课程。

– ARM has barrel shifter

shifter是两面性的,一方面它能够进步数学逻辑运算速度,另一方面它也添加了硬件的杂乱性。所以和能够完结相同功用的adder/shift register比较,功率更高,可是也占用更多的芯片面积。

– MIPS have “branch delay slot” and “load delay slot”

MIPS运用编译器来处理上面的两个问题。因为MIPS开端的规划思维便是运用简略的RISC硬体,然后靠编译器及其他软体技能,来到达RISC的完好概念。

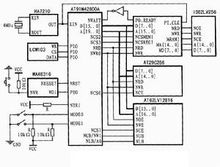

2.指令结构 instruction

– MIPS have 32bit and 64bit architecture,but ARM only have 32bit architecture

ARM11 部分64位

– MIPS是开放式的架构,用户能够在开发的内核中参加自己的指令,

– ARM has 4-bit condition code in every instruction

ARM 在这一点很像x86。MIPS在MIPS IV也参加”conditional move”指令,来进步pipeline的功率。

– ARM has pre- and post-increment addressing modes

auto-increment/decrement on load/store instructions

– 在节约代码空间方面,MIPS16 很相似ARM Thumb

3.寄存器 register

-因为MIPS内核中有32个寄存器(Register),而ARM只要16个,这种结构规划上的先天优势,决议了在平等功用表现下,MIPS的芯片面积和功耗会更小。

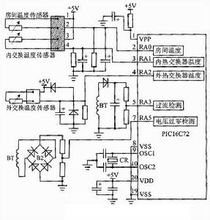

– ARM 有一组特别用处寄存器cp0-cp15,能够运用MCR,MRC等指令操控;相对应的,MIPS也有cp0 0-30,运用mfc0,mtc0 指令操控。

– Register banking in ARM. r8-r12 FIQ mode;r13:SP r14:LR

感觉不出banked register有什么长处。

– MIPS has a hard-wired-to-zero register ,but ARM not

MIPS use register $0 for Zero

4.地址空间 address space

– MIPS 开端地址是0xbfc00000,会有4Mbyte的巨细约束,但一般MIPS芯片都会采纳一些办法处理这个问题。

ARM没有这种问题。

MIPS24K 开端地址改到了0xbf000000,现在有16Mbyte的空间了。

– MIPS don’t have to turn paging on to enable the cache.

MIPS have the address space for both cache and un-cache

but ARM need enable/disable cache

5.功用 function

– Float point: MIPS64 has.

ARM’s support for FP is limited, and usually not included, and it is a 32 bit architecture

– ARM use JTAG,MIPS use EJTAG。Debug东西一般两种都支撑。运用起来感觉差不多。

6.功用 performance

– 具体功用比较,因为差异性太大,所以很难分出谁好谁坏。从个人经历来讲 MIPS4k和ARM9根本上是同一个等级的,但ARM9功用好像要比MIPS4K好。

相同是32bit的MIPS24K功用上比MIPS4K有很大进步,也应该比ARM9要好些。

因为没有用过ARM11和MIPS34K的芯片,无法比较,但感觉这两个好像是一个等级的。

Cortex-A8和 MIPS 74K都是最新的规划,应该功用也差不多。

7.运用

– 在1000MHz以上的运用,很难找到选用ARM架构的产品。

MIPS架构用在200MHz或许是266MHz以下的运用比较少,而这恰恰是ARM的主攻商场。

– ARM 因为功耗小,遍及用在在手机/PDA等便携式消费电子范畴; MIPS 在住所网关、线缆调制解调器、线缆机顶盒等,因为MIPS 多核的展开,现在大型网关设备也多用它。

– ARM 选用硬核授权;MIPS 选用软核授权,用户能够自己装备,做自己的产品。

8.未来展开

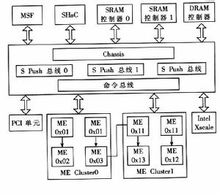

– ARM的下一代走向多内核结构,而MIPS公司的下一代中心则转向硬件多线程功用(multithreading)

MIPS 的multi-threading 很相似Intel 的 HyperThreading技能。从现在的展开来看,多内核占上风。

2008.12.21: 其实今日看来,也欠好妄自谈论孰好孰坏,尽管, HT技能在intel上展开并欠好(现已根本被dual core)替代,可是并不能揣度说MT在MIPS上就展开欠好,究竟mips的运用场合多是嵌入式范畴,而MT的功耗小芯片面积小的优势正好能发挥效果。

2008.12.29: MIPS也并不是只要multithreading, 其完结在许多的MIPS cpu的厂商都有multi-core的mips cpu在出,比方cavium, broadcom, infineon,国内的龙芯也有多核的产品。

2009.6.11: MIPS的多核展开明显比ARM要好。从 Cavium,RMI,公司的产品许多的运用便可见一斑。

9.总结

自己感觉ARM和MIPS在一开端的RISC的规划上有许多不同,但跟着技能的展开,各自取长补短,好的技能我们都会运用。比方ARM11和MIPS R1000就运用了许多相同的技能。感觉RISC做到了极至就都相同了。

精简指令集修改risc一般指精简指令集

本词条短少信息栏,补偿相关内容使词条更完好,还能快速晋级,赶忙来修改吧!

RISC的英文全称是Reduced Instruction Set Computer,中文是精简指令集核算机。特征是一切指令的格局都是共同的,一切指令的指令周期也是相同的,而且选用流水线技能。在中高档服务器中选用RISC指令的CPU首要有Compaq(康柏,即新惠普)公司的Alpha、HP公司的PA-RISC、IBM公司的PowerPC、MIPS公司的MIPS和SUN公司的Sparc。

目录

-

1简介

-

2展开布景

-

展开不合

-

提出原由

-

3优势

-

4特征

-

5结构特征

-

6展开前景

1简介修改

精简指令集,是核算机中央处理器的一种规划形式,也被称为RISC(Reduced Instruction Set Computer的缩写)。[1] 这种规划思路对指令数目和寻址办法都做了精简,使其完结更简略,指令并行履行程度更好,编译器的功率更高。常用的精简指令集微处理器包括DECAlpha、ARC、ARM、AVR、MIPS、PA-RISC、PowerArchitecture(包括PowerPC)和SPARC等。这种规划思路最早的产生缘自于有人发现,尽管传统处理器规划了许多特性让代码编写愈加快捷,但这些杂乱特性需求几个指令周期才干完结,而且常常不被运转程序所选用。此外,处理器和主内存之间运转速度的不同也变得越来越大。在这些要素促进下,呈现了一系列新技能,使处理器的指令得以流水履行,一起下降处理器拜访内存的次数。前期,这种指令集的特征是指令数目少,每条指令都选用规范字长、履行时刻短、中央处理器的完结细节关于机器级程序是可见的。

2展开布景修改

在前期的核算机业中,编译器技能没有呈现。程序是以机器言语或汇编言语完结的。为了便于编写程序,核算机架构师造出越来越杂乱的指令,能够高阶程序言语直接陈说高阶功用。其时的观点是硬件比编译器更易规划,所以杂乱的东西就加进硬件了。

加快杂乱化的其它要素是短少大内存。内存小的环境中,具有极高消息密度的程序较有利。当内存中的每一字节如此宝贵,例如贮存某个完好体系只需几千字节,它使工业移向高度编码的指令、长度不等的指令、履行多个操作的指令,和履行数据传输与核算的指令。其时指令封包问题远比易解的指令重要。

那时运用磁性技能,内存不只小,而且很慢。这是保持极高消息密度的其它原因。借着具有极高消息密度封包,当有必要存取慢速资源时能够下降频率。

CPU只要少量缓存器的两个原因︰

CPU内部缓存器远贵于外部内存。以其时的集成电路技能水准,大缓存器集对芯片或电路板区域仅仅剩余的糟蹋。

具有大数量的缓存器将需求大数量的指令位(运用宝贵的RAM)以做为缓存器指定器。

根据上述原因,CPU规划师试着令指令尽或许做更多的作业。这导致一个指令将做悉数的作业︰读入两个数字,相加,而且直接在内存贮存核算结果。其它版别将从内存读取两个数字,但核算结果贮存在缓存器。另一个版别将从内存和缓存器各读一个数字,并再次存入内存。以此类推。这种处理器规划原理终究成为杂乱指令集(CISC)。

其时的方针是给一切的指令供给一切的寻址形式,此称为「正交性」。这在 CPU 上导致了一些杂乱性,但就理论上每个或许的指令都能够独自的调试(调用,be tuned),这样使得程序员能够比用简略的指令来得更快速。

这类的规划终究能够由光谱的两端来表达, 6502 在光谱的一端,而 VAX 在光谱的另一端。单价25美元的 1MHz 6502 芯片只要单一的通用缓存器, 但它的极精简的单周期内存界面(single-cycle memory interface)让一个位的操作效能和更高频率规划简直相同,例如 4MHz Zilog Z80 在运用相同慢速的回忆芯片下(大约近似 300ns)。

展开不合

在核算机指令体系的优化展开进程中,呈现过两个天壤之别的优化方向:CISC技能和RISC技能。CISC是指杂乱指令体系核算机(Complex Instruction Set Computer);RISC是指精减指令体系核算机(Reduced Instruction Set Computer)。这儿的核算机指令体系指的是核算机的最低层的机器指令,也便是CPU能够直接辨认的指令。跟着核算机体系的杂乱,要求核算机指令体系的结构能使核算机的全体功用更快更安稳。开端,人们选用的优化办法是经过设置一些功用杂乱的指令,把一些原因由软件完结的、常用的功用改用硬件的指令体系完结,以此来进步核算机的履行速度,这种核算机体系就被称为杂乱指令体系核算机,即Complex Instruction Set Computer,简称CISC。另一种优化办法是在20世纪80年代才展开起来的,其根本思维是尽量简化核算机指令功用,只保存那些功用简略、能在一个节拍内履行完结的指令,而把较杂乱的功用用一段子程序来完结,这种核算机体系就被称为精简指令体系核算机.即Reduced Instruction Set Computer,简称RISC。RISC技能的精华便是经过简化核算机指令功用,使指令的均匀履行周期削减,然后进步核算机的作业主频,一起许多运用通用寄存器来进步子程序履行的速度

提出原由

IBM公司设在纽约Yorktown的JhomasI.Wason研讨中心于1975年安排力气研讨指令体系的合理性问题.因为其时已感到,日趋杂乱的指令体系不光不易完结.而且还或许下降体系功用.1979年以帕特逊教授为首的一批科学家也开端在美国加州大学伯克莱分校展开这一研讨.结果表明,CISC存在许多缺陷.首要.在这种核算机中.各种指令的运用率相差悬殊:一个典型程序的运算进程所运用的80%指令.只占一个处理器指令体系的20%.事实上最频频运用的指令是取、存和加这些最简略的指令.这样-来,长时刻致力于杂乱指令体系的规划,实际上是在规划一种可贵在实践中用得上的指令体系的处理器.一起.杂乱的指令体系必定带来结构的杂乱性.这不光添加了规划的时刻与本钱还简略形成规划失误.此外.尽管VLSI技能现在已到达很高的水平,但也很难把CISC的悉数硬件做在一个芯片上,这也阻碍单片核算机的展开.在CISC中,许多杂乱指令需求极杂乱的操作,这类指令多数是某种高档言语的直接翻版,因此通用性差.因为选用二级的微码履行办法,它也下降那些被频频调用的简略指令体系的运转速度.因此.针对CISC的这些弊端.帕特逊等人提出了精简指令的想象即指令体系应当只包括那些运用频率很高的少量指令.并供给一些必要的指令以支撑操作体系和高档言语.依照这个准则展开而成的核算机被称为精简指令集核算机(ReducedInstructionSetComputer-RISC)结构.简称RISC.

3优势修改

RISC和CISC是规划制作微处理器的两种典型技能,尽管它们都是企图

在体系结构、操作运转、软件硬件、编译时刻和运转时刻等许多要素中做出某种平衡,以求到达高效的意图,但选用的办法不同,因此,在许多方面差异很大,它们首要有:

(1)指令体系:RISC规划者把首要精力放在那些常常运用的指令上,尽量使它们具有简略高效的特征。对不常用的功用,常经过组合指令来完结。因此,在RISC机器上完结特别功用时,功率或许较低。但能够运用流水技能和超标量技能加以改善和补偿。而CISC核算机的指令体系比较丰厚,有专用指令来完结特定的功用。因此,处理特别任务功率较高。

(2)存储器操作:RISC对存储器操作有约束,使操控简略化;而CISC机器的存储器操作指令多,操作直接。

(3)程序:RISC汇编言语程序一般需求较大的内存空间,完结特别功用时程序杂乱,不易规划;而CISC汇编言语程序编程相对简略,科学核算及杂乱操作的程序规划相对简略,功率较高。

(4)中止:RISC机器在一条指令履行的恰当当地能够呼应中止,可是比较CISC指令履行的时刻短,所以中止呼应及时;而CISC机器是在一条指令履行完毕后呼应中止。

(5)CPU:RISCCPU包括有较少的单元电路,因此面积小、功耗低;而CISCCPU包括有丰厚的电路单元,因此功用强、面积大、功耗大。

(6)规划周期:RISC微处理器结构简略,布局紧凑,规划周期短,且易于选用最新技能;CISC微处理器结构杂乱,规划周期长。

(7)用户运用:RISC微处理器结构简略,指令规整,功用简略掌握,易学易用;CISC微处理器结构杂乱,功用强大,完结特别功用简略。

(8)运用规模:因为RISC指令体系的确认与特定的运用范畴有关,故RISC机器更适合于专用机;而CISC机器则更适合于通用机。

4特征修改

一致指令编码(例如,一切指令中的op-code永久坐落相同的位方位、等长指令),可快速解译︰

泛用的缓存器,一切缓存器可用于一切内容,以及编译器规划的单纯化(不过缓存器中区分了整数和浮点数);

单纯的寻址形式(杂乱寻址形式以简略核算指令序列替代);

硬件中支撑少量数据型别(例如,一些CISC核算机中存有处理字节字符串的指令。这在RISC核算机中不太或许呈现)。

RISC规划上一起也有哈佛内存模块特征,凡指令流和数据流在概念上分隔;这意味着更改代码存在的内存地址对处理器履行过的指令没有影响(因为CPU有着独立的指令和数据缓存),至少在特别的同步指令宣布前。在另一面,这答应指令缓存和数据缓存一起被拜访,一般能改善运转功率。

许多前期的RISC规划相同同享着欠好的副效果——搬运延时槽,搬运延时槽是指一个跳转或搬运指令之后的指令空间。不管搬运是否产生,空间中的指令将被履行(或许说是搬运效果被推迟)。这些指令让CPU的算术和逻辑单元(ALU)繁忙比一般履行搬运所需更多的时刻。现在搬运延时槽被认为是完结特定RISC规划的副效果,现代的RISC规划一般避免了这个问题(如PowerPC,最近的SPARC版别,MIPS)。

5结构特征修改

RISC是简化指令集核算机的简略缩写,其风格是着重核算机结构的简略性和高效性。RISC规划是从满足的不行短少的指令集开端的。它的速度比那些具有传统杂乱指令组核算机结构的机器快得多,而且RISC机因为其较简练的规划,较易运用,故具有更短的研制开发周期。RISC结构一般具有如下的一些特征:

①单周期的履行:它一致用单周期指令。从根本上克服了CISC指令周期数有长有短,形成运转中偶发性不确认,致使运转异常的问题。

②选用高效的流水线操作:使指令在流水线中并行地操作,然后进步处理数据和指令的速度。

③无微代码的硬连线操控:微代码的运用会添加杂乱性和每条指令的履行周期。

④指令格局的规格化和简略化:为与流水线结构相适应且进步流水线的功率,指令的格局有必要趋于简略和固定的规式。比方指令选用16位或32位的固定的长度,而且指令中的操作码字段、操作数字段都尽或许具有一致的格局。此外,尽量削减寻址办法,然后使硬件逻辑部件简化且缩短译码时刻,一起也进步了机器履行功率和可靠性。

⑤选用面向寄存器堆的指令:RISC结构选用许多的寄存器——寄存器操作指令,使指令体系更为精简。操控部件更为简化,指令履行速度大大进步。因为VLSI技能的迅速展开,使得在一个芯片上做许多的寄存器成为或许。这也促成了RISC结构的完结。

⑥选用装入/存储指令结构:在CISC结构中。许多设置存储器——存储器操作指令,频频地拜访内存,将会使履行速度下降。RISC结构的指令体系中,只要装入/存储指令能够拜访内存,而其它指令均在寄存器之间对数据进行处理。用装入指令从内存中将数据取出,送到寄存器;在寄存器之间对数据进行快速处理,并将它暂存在那里,以便再有需求时。不用再次拜访内存。在恰当的时分,运用一条存储指令再将这个数据送回内存。选用这种办法能够进步指令履行的速度。

⑦重视编译的优化,力求有效地支撑高档言语程序。

一般运用的单片机中,MCS一51系列的单片机归于CISC的体系结构;AVR系列的单片机则归于RISC的体系结构。

6展开前景修改

鉴于RISC的规划特征以及其无与伦比的长处,RISC体系结构处理器的展开方向:

一

650) this.width=650;” class=”lazy-img” alt=”” src=”http://f.hiphotos.baidu.com/baike/s%3D220/sign=28bdb2601038534388cf8023a312b01f/9c16fdfaaf51f3dea918f86894eef01f3a297917.jpg” style=”border:0px;background-image:url(“http://img.baidu.com/img/baike/img-loading.gif”);background-color:transparent;width:220px;height:130px;background-position:50% 50%;” />扩展指令集

是添加处理器的并行性;

二是扩展支撑可弹性并行核算机体系的功用;

三是进步工艺水平。终究RISC与DSP在嵌入式运用中完美交融,密不行分。

RISC微处理器不只精简了指令体系,选用超标量和超流水线结构;它们的指令数目只要几十条,却大大增强了并行处理才能。如:1987年SunMicrosystem公司推出的SPARC芯片便是一种超标量结构的RISC处理器。而SGI公司推出的MIPS处理器则选用超流水线结构,这些RISC处理器在构建并行精简指令体系多处理机中起着中心的效果。RISC处理器是当今UNIX范畴64位多处理机的干流芯片。

功用特征

功用特征一:因为指令集简化后,流水线以及常用指令均可用硬件履行;

功用特征二:选用许多的寄存器,使大部分指令操作都在寄存器之间进行,进步了处理速度;

功用特征三:选用缓存—主机—外存三级存储结构,使取数与存数指令分隔履行,使处理器能够完结尽或许多的作业,且不因从存储器存取信息而怠慢处理速度。

运用特征

因为RISC处理器指令简略、选用硬布线操控逻辑、处理才能强、速度快,世界上绝大部分UNIX作业站和服务器厂商均选用RISC芯片作CPU用。如原DEC的Alpha21364、IBM的PowerPCG4、HP的PA—8900、SGI的R12000A和SUNMicrosystem公司的UltraSPARC║。

运转特征

RISC芯片的作业频率一般在400MHZ数量级。时钟频率低,功率耗费少,温升也少,机器不易产生毛病和老化,进步了体系的可靠性。单一指令周期包容多部并行操作。在RISC微处理器展开进程中。曾产生了超长指令字(VLIW)微处理器,它运用十分长的指令组合,把许多条指令连在一起,以能并行履行。VLIW处理器的根本模型是标量代码的履行模型,使每个机器周期内有多个操作。有些RISC处理器中也选用少量VLIW指令来进步处理速度。