逻辑规划范畴正在发生底子变化。新一代规划东西协助软件开发者将其算法表达直接转化成硬件,而无需学习传统的硬件规划技能。

这些东西及相关规划办法学一同被归类为电子体系级 (ESL|0″>ESL) 规划,广泛地指从比现在干流的寄存器传输级 (RTL) 更高的笼统等级上开端的体系规划与验证办法学。与硬件言语如 Verilog 和 VHDL比起来,ESL 规划言语在语法和语义上与盛行的 ANSI C 比较挨近。

ESL 与 FPGA 有何联系?

ESL 东西现已存在了一段时刻,而许多人觉得这些东西首要专心于 ASIC 规划流程。但是事实上,越来越多的 ESL 东西供给商正在专心于可编程逻辑;现在,商场上有多种东西支撑专为赛灵思® FPGA 而优化的体系规划流程。ESL 流程是对 FPGA 规划东西的一种天然演进,能够使更多和更广泛以软件为中心的用户群更简单地运用可编程硬件的灵活性。

咱们来考虑一些由 ESL 和 FPGA 构成严重组合的情形:

- ESL 东西和可编程硬件一同构成一个依据桌面的硬件开发环境,契合软件开发者的作业流程模型。东西可供给针对特定的依据 FPGA 的参阅板的优化支撑,软件开发者能够运用这些支撑发动项目评价或原型构建。这些板及相应的参阅运用程序均运用更高等级的言语编写,这使创立定制的、硬件加速的体系更为快速和简单。实践上,现在软件程序员能够以运用微处理器参阅板及东西大体相同的办法,运用依据 FPGA 的参阅板及东西。

- 经过运用现在FPGA 中已很遍及的高功用嵌入式处理器,软件和硬件规划组件能够装入到一个器材中。从体系的软件描绘开端,您能够依据运用程序的功用要求,将每个规划块用硬件或软件来完结。ESL 东西支撑智能切割和软件功用到等效硬件功用的主动导出,然后增加了价值。

ESL 进步了“勘探式规划和优化”的概念。ESL 办法学与可编程硬件的结合运用,使测验很多或许的运用完结以及对极大不同的软件/硬件切割战略快速进行试验成为或许。这种试验的才能——测验新办法和快速剖析功用与尺度平衡——使 ESL/FPGA 用户能够比运用传统的 RTL 办法以更短的时刻完结更高的整体功用。

此外,经过在更笼统的等级上作业,您能够运用更少的击键和更少的代码行来表达您的意图。这一般意味着快得多的规划完结,和更少的犯错时机,而这些错误将需求冗杂的、初级调试。

ESL 的方针受众

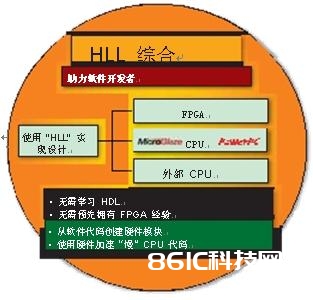

ESL 流程对预期 FPGA 用户的首要长处是其生产率和易用性。经过将发生硬件电路的完结细节进行笼统,这些东西向以软件为中心的用户群(图 1)发出了呼唤。在更高的笼统等级上作业,使具有 C 言语等传统软件编程言语技能的规划者能够更快地以硬件探究其主意。在大多数状况下,您能够无需经验丰富的硬件规划者的协助而完结整个规划的硬件完结。

以软件为中心的运用程序和算法开发者已将该办法的长处运用于 FPGA,他们包含体系工程师、科学家、数学家、和嵌入式与固件开发者。

合适 ESL 办法学的运用程序的特征包含具有很多内循环的核算密集型算法。这些运用程序能够经过硬件中的并发并行履行完结巨大加速。ESL 东西已在音频/视频/图画处理、加密、信号与分组处理、基因摆放、生物信息、地球物理和天体物理等运用范畴成功协助进行了项目布置。

ESL 规划流程

与 FPGA 相关的 ESL 东西包含两个首要规划流程:

1、高档言语 (HLL) 归纳。HLL 归纳掩盖算法或行为归纳,可从 C 或C类的软件言语生成硬件电路。各种协作伙伴处理方案选用不同的办法将高档规划描绘转化为 FPGA 完结。怎么完结这一点构成了各种 ESL 产品之间的底子不同。

您能够将 HLL 归纳用于各种运用状况,包含:

- 模块生成。在这种运用形式下,HLL 编译器能够将以 C 表明的功用块(例如一个 C 子程序)转化成相应的硬件块。生成的硬件块随后被收入整个硬件/软件规划。这样,HLL 编译器生成了整个规划的一个子模块。

模块生成经过快速生成,然后集成算法硬件组件,答应软件工程师参加整个体系的规划。那些寻求以更快的办法构建新的、以核算为导向的硬件块的硬件工程师们,也能够运用模块生成。

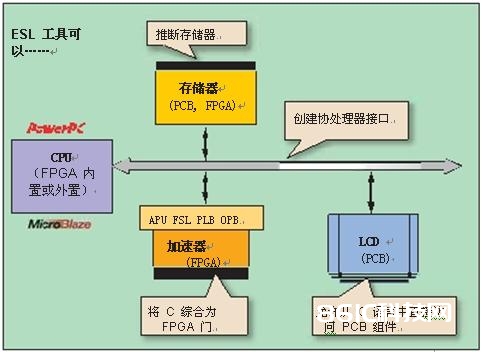

- 处理器加速。在这种运用形式下,HLL 编译器答应经过在 FPGA 的可编程结构中创立定制加速器块,来加速在处理器中运转的时刻要害功用或瓶颈功用。

除创立加速器外,这些东西还能够主动揣度存储器并生成所需的硬件-软件接口电路,以及完结处理器与硬件加速器块之间通讯的软件设备驱动程序(图 2)。与运转在 CPU 中的代码比较,FPGA 加速的代码其运转速度能够快几个数量级,而耗费的功率则大大下降。

2、体系建模。关于大型规划,或处理器用作整个规划的一部分时,运用传统的 RTL 模型进行体系仿真或许会十分慢。一种盛行的新式 ESL 办法选用了高速业务级模型,一般运用 C++ 编写,以大大加速体系仿真速度。

ESL 东西为您供给了一种依据虚拟渠道的验证环境,您能够在其中剖析和调整规划的功用和功用特点。这意味着能够更早运用体系的虚拟表明,完结更大的规划探究和假定剖析。

您能够评价和改善功用问题,如推迟、吞吐率和带宽,以及挑选性的软件/硬件切割战略。一旦规划满意功用方针,就可将其付诸硅完结。

|

|

图 1:大多数用于 FPGA 的 ESL 东西均针对以软件为中心的用户群。 |

|

|

|

图 2:ESL 东西笼统了在 FPGA 中加速处理器运用程序有关的细节。 |

ESL 东西供给商面对的应战

相对而言,面向 FPGA 的 ESL 东西对商场来说是新生事物;客户承受仍然是一个要害应战。ESL 东西供给商面对的最大应战之一,是需求战胜人们对 ESL 和 FPGA 能够做什么,已存在哪些处理方案和功用,以及该技能的实践用处和长处等问题的遍及性知道缺乏。其他应战还包含用户对成果质量的了解和重视以及与 ESL 承受相关的学习曲线。

虽然一些如由 ESL 引进的典范转化,需求长时刻才可为现有 FPGA 用户社区彻底承受,咱们仍需求处理现在阻止承受的一些要害问题。这一点尤为重要,由于今日的 ESL 技能已做好预备,向潜在的很多方针受众供给严重实践价值。

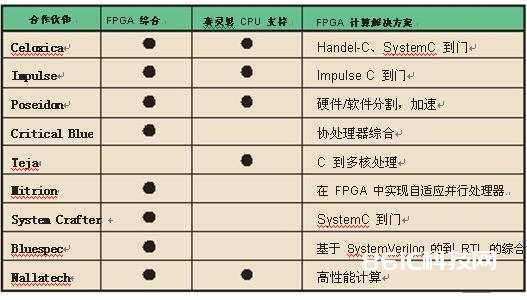

赛灵思 ESL 建议

赛灵思以为 ESL 东西具有极大地改动硬件和软件规划者创立、优化和验证杂乱电子体系办法的潜力。为了将这一新式技能的悉数长处带给客户,和树立一种适用于特别针对 FPGA 的 ESL 技能的公共渠道,赛灵思活跃联络其生态体系协作伙伴,成立了协作性的联合 ESL 建议(表 1)。

|

|

表 1:赛灵思 ESL 协作伙伴选用从高档言语到 FPGA 完结的不同办法。 |

该建议的主旨是加速针对 FPGA 的 ESL 立异脚步,和使该技能更靠近以软件为中心的用户群的需求。作为建议的一部分,有以下两个要点:

- 工程协作。赛灵思将与协作伙伴严密协作,继续进一步进步 ESL 产品阵营的价值。这将包含改善编译器成果质量和增强东西互操作性及整体易用性等作业。

- ESL 知道与宣扬。赛灵思将向当时及预期新客户宣扬面向 FPGA 的 ESL 流程的价值和长处。该方案将企图奉告和教育用户有关现在已有 ESL 处理方案类型的常识,以及各种产品怎么供给处理现有问题的更好办法。意图是协助用户就各种协作伙伴 ESL 产品满意其专用需求的合适性做出信息全面的决议计划。更大的知道将导致客户承受度进步,反过来又会促进可继续的面向 FPGA 的协作伙伴 ESL 生态体系。

开端运用 ESL

作为构筑各种面向 FPGA 的 ESL 尽力的更大知道的第一步,赛灵思已组合各种资源推出了一个全面的 ESL 网站。其内容包括现在商场上每个协作伙伴 ESL 处理方案的专门及共同方面,旨在协助您决议哪个(若有的话)可用处理方案最合适您的运用。要开端您的 ESL 导向,请拜访 www.xilinx.com/esl。

此外,赛灵思还开设了一个新的面向 FPGA 的 ESL 论坛,地址为:http://toolbox.xilinx.com/cgi-bin/forum。在这里,您能够参加针与面向 FPGA 的 ESL 规划有关的各种主题的评论。

定论

面向 FPGA 的 ESL 东西为您供给了经过可编程硬件探究您的主意而无需学习与硬件规划有关的低层细节的才能。今日,您有时机从广泛的立异和生产率增强处理方案中挑选专门针对赛灵思 FPGA 优化的处理方案。跟着 ESL 建议的正式发布,赛灵思全面投入与第三方生态体系的协作,力图为当时及潜在未来客户供给最佳的 ESL 东西。面向继续更新和新开发随时做好预备。

作者:Milan Saini 技能营销司理 赛灵思公司 @xilinx.com”>milan.saini@xilinx.com