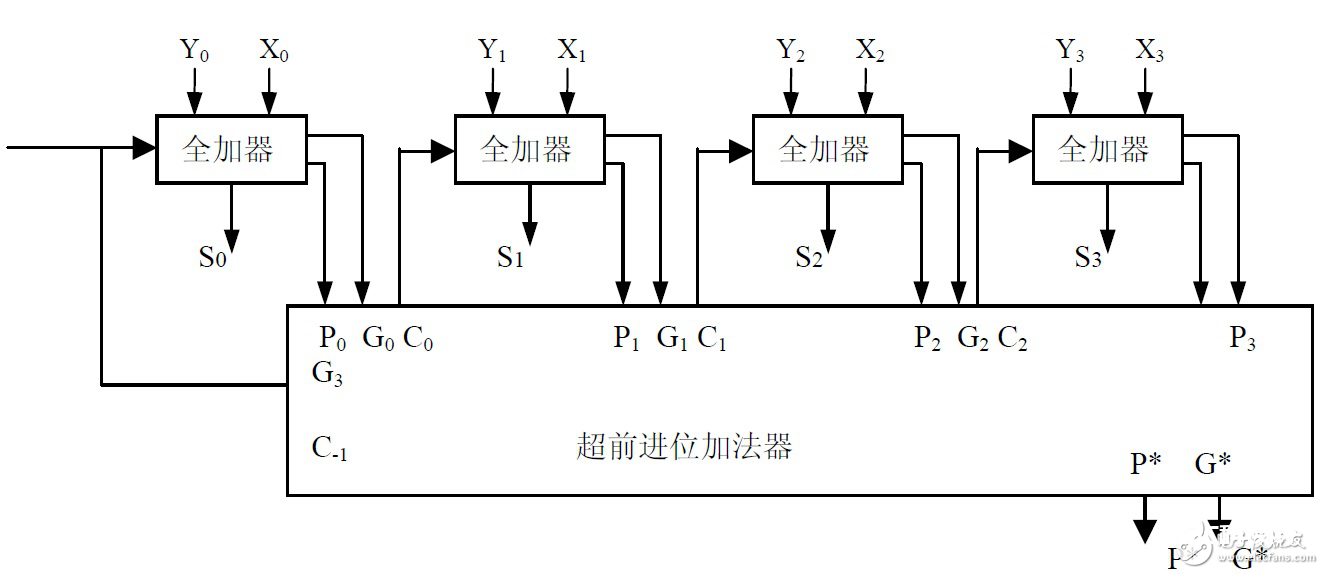

面积和速度这两个目标贯穿戴FPGA规划的一直,是规划质量点评的终极标准。

“面积”:指一个规划所耗费的FPGA的逻辑资源数量。FPGA中的逻辑资源,也便是触发器( FF)和查找表(LUT) 。

“速度”:是指规划结果在芯片上安稳运行时所能到达的最高频率,这个频率由规划的时序情况决议。与规划满意的时钟周期、PAD to PAD TIme、树立时刻、坚持时刻和时钟到输出延时等很多时序特征向量密切相关。

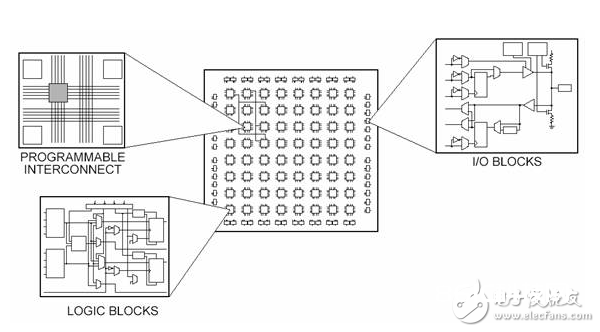

逻辑仿制

逻辑仿制是一种最基本的经过增加面积改进时序条件的优化手法。这种办法最常用的场合是调整信号的扇出。当一个信号要驱动后级的许多单元时,也便是有多级扇出时,可能会呈现如图1中左图所示的一些扇出途径的长延时。此刻的解决办法便是经过信号逻辑的仿制来削减途径延时。

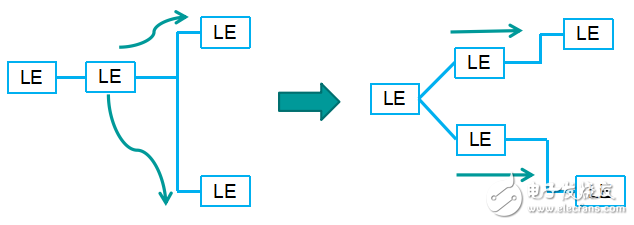

串并转化

串并转化是面积与速度交换思维的另一种表现。假定FPGA 上处理模块的处理速度最大为100Mbits/ s,假如输入数据流的速率是300 Mbits/ s。在这种情况下,如图2所示,首先将输入数据进行串并转化,然后运用这3个模块并行处理分配的数据,最终将处理结果“并串转化”,完结数据速率的要求。

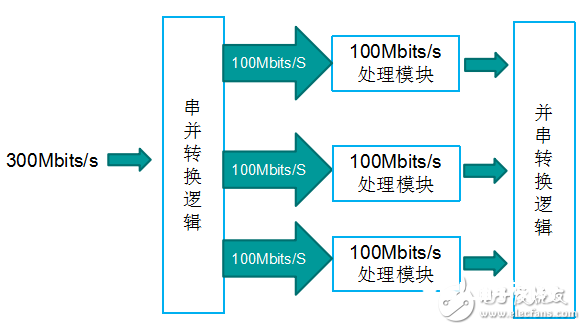

布尔逻辑扩展运算-超前进位加法器

在数字信号处理的快速运算电路中常常用到多位数字量的加法运算,这时需求用到并行加法器。现在遍及选用的超前进位加法器,只是在几个全加器的基础上增加了一个超前进位构成逻辑,以削减因为逐位进位信号的传递所形成的推迟。下面的逻辑图表明了一个四位二进制超前进位加法电路。

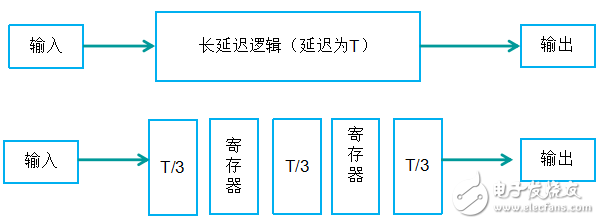

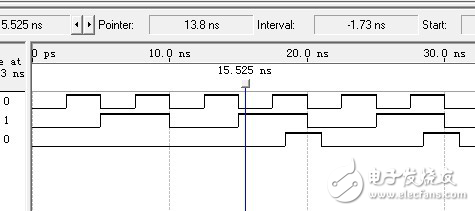

布尔逻辑扩展运算-流水线技能

所谓流水线规划实际上便是把规划较大、层次较多的组合逻辑电路分为几个级,在每一级刺进寄存器组暂存中心数据。K级的流水线便是从组合逻辑的输入到输出刚好有K个寄存器组(分为K级,每一级都有一个寄存器组)上一级的输出是下一级的输入而又无反应的电路。

运用EDA东西进步作业时序

东西优化规划的作业时序主要是经过给规划增加各式各样的时序束缚,时序束缚能够标准规划的时序行为,表达规划者希望满意的时序条件。经过附加束缚能够操控逻辑的归纳、映射、布局和布线,以减小逻辑和布线延时,然后进步作业频率。

面积的优化—逻辑资源的同享

例如:运用数据选择器完成加法器(运算器)的同享。