现在数字锁相环在数字通信、雷达、无线电电子学、仪表仪器、高速核算机及导航体系中得到了广泛的运用。与传统的模仿锁相环比较,全数字锁相环克服了模仿锁相环易受电压改动的影响和温度漂移的缺陷,因而具有作业安稳、可靠性高、便利完结等长处。跟着大规模可编程逻辑器材的开展,不只为全数字锁相环的规划带来的史无前例的便利,并且能够把整个体系作为一个功用模块,嵌入SoC(SysteIn on Chip)中,构成片内锁相环,进步环路的作业功用,这将具有十分严重的含义。全数字锁相环的结构方式多种多样,但都是以完结锁相速度更快,锁相规模更大,相位抖动更小作为规划的方针。现在的全数字锁相环大多是在已知输入信号频率的前提下,考虑体系的时钟频率,然后确认除N计数器的N值。这类全数字锁相环的中心频率是不能够改动的,因而,锁频规模有限。当输入信号的频率发生较大改动时,该锁相环将不能到达确定状况。文献规划了一种高精度主动变模操控的快速全数字锁相环,该办法既能够大大进步确定速度,又能够大幅度下降噪声对环路的搅扰,可是该数字锁相环的频带宽度较窄,在运用上受到了约束。有文献对数字锁相环的频带怎么拓展进行研讨,其主要的思维是改动环路的中心频率。文献选用可控模/数分频器的简略办法完结捕获时刻小而捕获带宽宽的全数字锁相环,处理了“捕获时刻”和“捕获带宽”两者彼此对立的问题。可是该办法完结的全数字锁相环在输入信号频率发生的骤变时,将无法确定。

在此提出了一种具有主动变模操控的宽频带的全数字锁相环。在传统的主动变模操控的全数字锁相环的基础上,增加了共同的鉴频锁存模块,能够随时盯梢输入信号频率的改动,在先确定输入信号频率的基础上快速完结相位的确定。整个体系选用VHDL言语规划完结,运用QuartusⅡ软件对体系进行仿真验证,给出了核算机的仿真成果。

1 改善后的主动变模操控的全数字锁相环的结构和作业原理

如图1所示为改善后的主动变模操控的全数字锁相环的体系方框图。图中的鉴相器选用边缘触发鉴相器,相对于异或门鉴相用具有更大的鉴相规模,边缘触发型鉴相器的线性鉴相规模为±π。该规划中的数字环路滤波器为可变模的K可逆计数器,鉴相器的输出ue作为K可逆计数器的计数方向操控信号,K计数器的计数值增加到K时,就输出“加”指令;反之,K计数器的计数值减到0时,就输出“减”指令。在体系作业进程中,主动变模操控器通过检测电路对输入信号ui和输出信号uo的相位差进行计数,然后通过比较电路和模数操控电路挑选适宜的模值mo,不断地更新K计数器的K值。脉冲加减电路作为数控振荡器的一部分,是整个体系中最重要的模块。脉冲加减电路的功用是在接收到“加”、“扣”指令时,能够精确地在本地高速时钟clk中刺进和扣除一个脉冲,把调整后的脉冲序列作为除N计数器的时钟源,对输出信号uo的相位进行调整。该规划的最大特色便是除N计数器模块的N值能够依据输入信号的改动不断更新,使输出信号uo快速盯梢输入信号ui的频率,一起到达对体系中心频率的不断更新,完结宽频带快速锁相的意图。N值的检测是由鉴频和锁存模块完结的,当输入信号ui为上升沿时,内部计数器开端计数,直到ui变为低电平时,计数器中止计数。一起在ui为低电平时把计数成果送入锁存器中作为除N计数器的分频值。上述即为改善后的主动变模操控的全数字锁相环的作业原理。

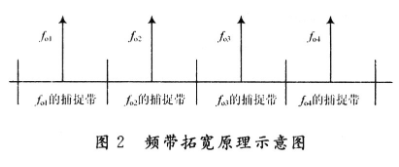

从以上的剖析可知,该规划的全数字锁相环具有两个明显长处:榜首,因为选用主动变模操控的数字环路滤波器,很好地处理了环路的捕捉时刻和抗噪声功用之间的对立。模值K的巨细对整个体系的功用具有很大影响,K值越大,体系呼应越慢,捕捉时刻越长;相反,K值越小,体系呼应越快,捕捉时刻越短。可是在体系由捕捉进入同步进程后,假如K值太小,会因可逆计数器的频频循环计数而发生继续的进位或借位脉冲,导致输出信号相位抖动,增加了同步差错。选用主动变模操控后,体系能够依据输入/输出信号相位差错的巨细,对模值K进行挑选更新。在环路捕捉进程中,挑选较小的模值,可增加环路带宽,加速确定速度;在同步进程中,挑选较大的模值,可缩小环路带宽,有利于按捺相位抖动,减小同步差错,然后能够完结快速高精度的锁相。第二,在传统全数字锁相环结构的基础上增加了共同的鉴频锁存模块,不只能够捕捉和确定不知道的输入信号,还能够使体系具有较宽的频带宽度,完结对频率发生改动的输入信号的快速确定。该规划的频带拓展原理能够描绘为:在鉴频锁存模块,输入信号频率的核算是以外部高速时钟作为时钟源的,外部时钟频率越高得到的N值越精确。能够精确核算出的频率值就相当于不同体系中心频率,而在每个中心频率邻近锁相环体系都有一个捕捉带。因而,挑选适宜的外部高速时钟,不同的中心频率所得到的不同捕捉带,就能够构成整个环路的捕捉带。所以,该规划与传统的数字锁相环体系比较具有较宽的频带。如图2所示为频带拓展原理示意图。

2 体系规划和核算机仿真成果

该规划在Altera公司出产的QuartusⅡ7.1开发软件平台上,运用自顶向下的体系规划办法,首要依据体系各功用模块的要求,运用VHDL言语编写程序,规划出环路各个部分的逻辑电路,并进行仿真验证。然后,再将各个部分组合起来进行体系规划和仿真。最终,用FP-GA芯片予以完结。限于篇幅,这儿只对鉴频锁存模块的VHDL规划、仿真作为一个列子详细给出。其他模块不再赘述。该模块顶层部分的VHDL源代码如下:

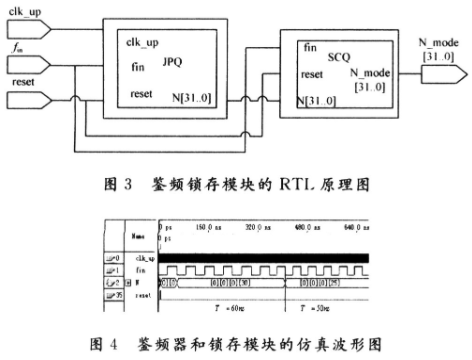

图3为QuartusⅡ7.1归纳出的鉴频锁存模块的RTL原理图。图中JPQ,SCQ分别是由底层的VHDL代码归纳出的鉴频器和锁存器,完结对输入信号鉴频和锁存的功用。图4为QuartusⅡ7.1的时序仿真波形图。图3中clk_up=1 ns为鉴频锁存模块的时钟源,fin为体系的输入信号ui的输入端,reset为体系的复位信号,N[31..0]为锁存器输出的鉴频成果。仿真成果标明该模块能够正确的完结鉴频和锁存的功用。

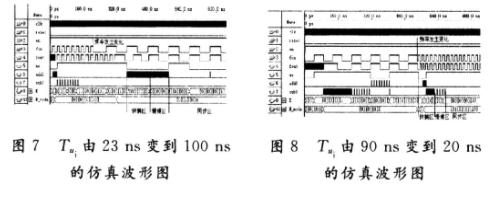

环路中各部分的规划仿真完结之后,再对整个体系进行规划和验证。在仿真图中clk为体系时钟;reset为复位信号;en为体系使能信号;fin和fout分别为输入输出信号;ue标明fin是超前仍是滞后fout;add1,sub1是“加”、“扣”脉冲信号;K为fin和fout之间相位差错的量化值;N_mode为除N计数器的N值。主动变模操控电路依据输入与输出信号之间差错的巨细,将环路的作业进程分为:快捕区、慢捕区和同步区。图5为输入信号周期Tui=23 ns的仿真波形图。图6为输入信号周期Tui=100 ns的仿真波形图。

图5和图6标明:该规划对输入的高频和低频信号都具有快的盯梢功用。图7为输入信号周期Tui由23 ns变到100 ns的仿真波形图。图8为输入信号的周期Tui由90 ns变到20 ns的仿真波形图。图7和图8标明:该规划对频率骤变(高频骤变到低频和低频骤变到高频)的输入信号具有快的盯梢功用。

3 结 语

通过核算机仿真能够看出:规划的全数字锁相环具有很快的锁相速度,很多的试验标明在7个输入信号周期内环路就进入确定状况。从图5和图6的仿真成果能够看出,规划的全数字锁相环锁频规模很宽。别的,锁相精度和体系的外部高频时钟有很大联系,假如时钟频率很高,那么锁相精度就越高。一起,外部高频时钟与该全数字锁相环的带宽也有很大的联系,在鉴频锁存模块是把外部高速时钟分频后的时钟作为时钟源的,因而,外部高频时钟频率越高,通过鉴频得到的分频值N才干越精确。总归,该规划的主动变模的全数字锁相环在外部时钟频率很高的情况下,不只具有较快的锁相速度,并且具有较宽的锁频规模和较高的锁相精度。

该规划的全数字锁相环结构简略,易于集成,可选用VHDL言语完结体系规划,便利运用EDA软件进行归纳仿真,可制成片内锁相环。下一步需求要点做的作业是:研讨怎么运用环形数控振荡器,运用操控字来操控环形数控振荡器的输出替代该规划中的外部高速时钟源;另一方面,在除N分频模块研讨怎么运用小数分频的技能进步了体系的精度。

责任编辑:gt