0 导言

PWM(Pulse Width Modulation)是通过调理输出波形的脉冲宽度来改动输出电压巨细的一种调制办法,在沟通传动、电力拖动体系和操控范畴有着广泛的用处,但选用PWM调制技能在负载上的电流波形对错正弦波,这就使负载上具有许多的高次谐波成份,对体系的目标和稳定性构成很大的损害。正弦型脉宽调制(Sinusoidal Pulse Width ModulaTIon,SPWM)是一种使输出的PWM波形按正弦的规矩进行改动的技能,然后大大的提高了后级功率开关器材的稳定性和体系的功率。常见的SPWM波形发生办法首要有两种:一种是运用专门的SPWM发生芯片如TMS320 F2812来发生,这种办法的特点是一次能够发生6路或12路SPWM信号;另一种办法运用天然采样法的原理,选用数字或模仿办法发生三角波和正弦波,再运用比较器对发生的三角波和正弦波进行比较而得到SPWM波,这种办法发生SPWM波的路数比较灵敏,电路原理简略,但详细完成比较复杂。

1971年3月,美国学者J.TIemcy,C.M.Rader和B.Gold提出了从相位概念动身直接组成所需波形的一种新的频率组成原理,称之为直接数字频率组成器(DDS)。DDS技能是一种直接数字组成办法,不需求振动和锁相环节,直接将波形函数进行离散化,以时刻为地址,起伏为量化数据,顺次存入波形存储器,使接连的数据流通过数/模转换器发生需求的波形。本文运用FPGA内部的DDS模块发生离散化的正弦波和三角波,从而发生数字的SPWM波形,再通过死区发生、脉冲消去处理后就得到了能够驱动后级功率放大管的驱动信号,运用该办法能够灵敏的发生所需的恣意调制比和载波比的SPWM波形,而且能够使负载上谐波含量大大减小,有用确实保了整个体系的稳定性。

1 SPWM波形的FPGA完成

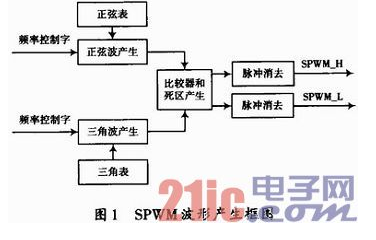

依据SPWM天然采样法的原理,发生合适逆变器功率放大管所需的SPWM信号的电路首要包含正弦波发生模块、三角波发生模块、比较和死区发生模块和脉冲消去模块,它们之间的联系如图1所示。

正弦波发生模块依据主操控器传来的频率操控字从ROM表中读出相应的正弦波的离散值,相同,三角波发生模块依据频率操控字从存储三角波的ROM表中读出三角波的离散值,比较器和死区发生模块依据传来的正弦波和三角波的离散值进行比较,直接进行比较发生上桥臂驱动信号,将正弦波离散值或三角波离散值加上一个特定的值或减去一个特定值再和三角波进行比较,发生上桥臂对应的下桥臂驱动信号,这时发生的信号已经是带死区的SPWM信号,再通过脉冲消去模块,消去功率器材来不及反响的窄的驱动信号,最终就能够得到直接驱动逆变器的一对SPWM信号。

1.1 波形发生模块

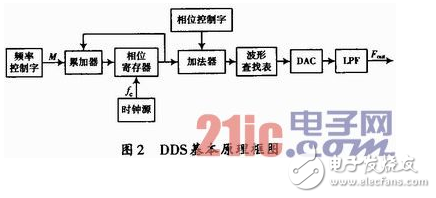

DDS技能是一种全数字的频率组成技能,是将已知的信号通过取样、量化,构成可供查询的数据表存于数据ROM中,通过改动频率操控字来改动输出所需频率的一种技能。如图2所示,DDS首要由频率操控字、累加器、相位寄存器、时钟源、加法器、相位操控字、波形查找表、DAC和LPF等模块组成。但因本规划不需求模仿信号,直接运用其间的数字信号,故不需求DAC和LPF模块,悉数在FPGA内部数字化完成。数字三角波的发生和数字正弦波的发生相同,专一不同便是在波形表顶用量化后的三角波数据替代正弦波数据。

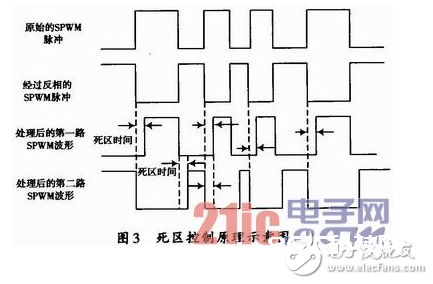

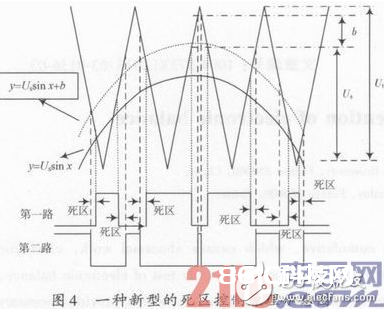

软件完成办法与脉冲消去办法大致相同,一般都是规划一个加减计数器,依据死区时刻来确认加减计数器的最大值d,由计数器的最大值d来确认死区时刻。这种完成办法是一般的完成办法,本规划提出了一种新式的死区发生办法,如图4所示,实线表明正常选用天然采样法的正弦波形和三角波形,正弦波y=Ussin x的半波的起伏为Us,三角波的起伏为Ut,依据天然采样法的原理,这儿假定正弦波大于三角波时输出为高电平,小于时输出为低电平,依据正弦波和三角波的交点及电平输出的判别规矩能够得到SPWM脉冲的榜首路波形,这时把正弦波向上平移b个单位,如图4中的虚线,正弦波形y=Ussin x变为y=Ussinx+6,再依据天然采样法的原理用平移后的正弦波和三角波相交,依据交点判别输出凹凸电平,这样判别输出的电平凹凸就能够得到第二路的SPWM波形,生成了SPWM波形的死区,在本规划中选用的是数字办法发生SPWM,依据图4,能够在程序中按原本的办法发生榜首路信号,把从ROM中取出的正弦信号加上b,再和原本的方波信号进行比较,这样就能够得到第二路SPWM信号,相同道理,也能够把三角波向上平移b个单位来发生第二路SPWM信号,但不管平移正弦波或三角波,都要确保平移后的正弦波的波形起伏要小于三角波的波形起伏。也能够规划第三个ROM,在程序外把通过向上平移后的正弦波形进行量化,存入ROM表中,在程序顶用这个表和三角波的离散值进行比较,仅仅这样规划会添加FPGA硬件资源的耗费和增大存储器的存储空间。

正弦信号往上偏移值b确实认是依据死区时刻的值来确认的,这个值越大,则死区时刻也越长,所以,能够调理b的值来增大或减小死区时刻。一对通过死区处理后的SPWM波形如图5所示,从图5中能够看出,死区时刻为16μs。

1.3 脉冲消去模块

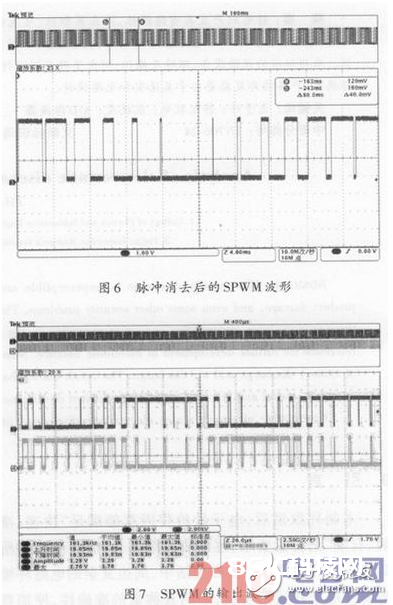

在发生的SPWM脉冲中,完好的SPWM脉冲序列包含了占空为从0~100%的脉冲,因而有些脉冲的宽度能够到达十分小,而实际上,过窄的脉冲是无用的,由于在这样短的脉冲继续时刻内,后级的功率放大管是不能彻底导通或关断,只会添加功率器材的损耗,所以有必要删去这些不良窄波;如图4所示,第二路的SPWM波形会呈现比榜首路SPWM波形小两倍死区时刻的脉冲,假如某个脉冲已经在临界的宽度了,通过死区发生模块就会变成一个对后级的功率管来说过窄的脉冲,这也便是脉冲消去模块在死区模块后级的原因,它的作用是消去一些原本就有的和通过死区处理后的毛刺。处理后的波形如图6所示,图7为处理后的一对带死区的SPWM波形。

不管选用这种办法发生的SPWM波形,仍是运用加减计数器的办法来发生SPWM波形,通过脉冲消去模块,都会存在输出的两路SPWM脉冲不对称性问题,如图7所示,便是有或许其间一路的波形缺失或所对应的另一路波形呈现缺失,但这个问题能够在脉冲消去后再加一个模块进行处理而防止;关于载波频率变小时负载谐波变大的问题能够参阅器材参数选用必定频率范围内的动态载波比和动态死区时刻来处理。

2 结语

本文规划了一种依据FPGA的带死区的SPWM波形发生技能,关于SPWM的死区发生,一般都是使用加减计数器来完成,本文提出了一个新的挑选,把死区发生模块交融到了比较模块中,运用波形平移技能,奇妙的发生了所要求死区时刻的SPWM波形。生成的SPWM波形输出给后级的功率放大电路,检测体系负载上的电压和电流波形为较好的正弦波形,很好地满意了规划的要求。